Fターム[5B033AA01]の内容

Fターム[5B033AA01]の下位に属するFターム

Fターム[5B033AA01]に分類される特許

1 - 20 / 62

半導体集積回路

【課題】性能低下を招くことなく回路面積を削減出来る半導体集積回路を提供すること。

【解決手段】第1メモリ30と、第1メモリ30に対するキャッシュメモリとして働く第2メモリ10とを備える。第1メモリ30からデータが読み出される場合の第1読み出し、第2メモリ10からデータが読み出される場合の第2読み出し、及び該データを第2メモリ10から読み出すと決定する判定、は、複数の処理ステージのうちのいずれかの処理ステージで実行される。第1読み出しにて読み出されたデータが出力されるタイミングと、第2読み出しにて読み出されたデータが出力されるタイミングとは同一である。第1読み出しで読み出されたデータは、第2メモリ10を経由しない経路を用いて出力される。

(もっと読む)

制御装置、及び制御方法

【課題】複数のレジスタへのアクセスを高速に行う。

【解決手段】制御装置は、複数のレジスタのアドレスをそれぞれ保持し、前記複数のレジスタのアドレスとは異なる第1のアドレスの指定に応答して前記複数のレジスタのアドレスを出力するアドレス設定部と、前記アドレス設定部から前記複数のレジスタのアドレスが入力され、当該複数のレジスタを選択する選択信号を同じタイミングで出力する第1のデコーダと、前記第1のアドレスに対する書込みデータを前記選択信号により選択される複数のレジスタに並行して書き込み、また、前記選択信号により選択される複数のレジスタから並行して読み出したデータを前記第1のアドレスからの読出しデータとして出力するデータ入出力部とを有する。複数のレジスタへ同時にアクセスでき、レジスタアクセスが高速化される。

(もっと読む)

サブワード実行を用いるVLIWベースのアレイプロセッサで条件付き実行をサポートする方法及び装置

【課題】複合条件に基づくサブワード並列実行をサポートする。

【解決手段】汎用フラグ(ACF)は階層を使用して定義され、エンコードされる。加えられた各ビットは、前の機能性のスーパーセットを提供する。条件の組合せを用いて、複合条件に基づく条件付き分岐の順次シリーズを回避することができ、次いで複合条件を条件付き実行のために使用することができる。フラグの数を変えることによって、条件付きオペレーションの並列性は、例えばVLIW実行での単一の処理からオクタル処理まで、かつ処理要素のアレイにわたって広範に変化することができる。異なるプロセッサ中で生成された条件に基づいて1つのプロセッサ中の条件付き実行を指定することを可能にして、多数のPEは、条件情報を同時に生成することができる。多数のプロセッサアレイ中の各プロセッサは、異なるユニットをそれらのACFに基づいて条件付きで独立に動作させることができる。

(もっと読む)

情報処理装置および情報処理方法

【課題】情報処理に必要なビット操作が多様化し、必要な処理も複雑化している。

【解決手段】情報処理装置10は入力レジスタ12に格納されたデータをビットごとに操作し、その結果を出力レジスタ14に格納する。セレクタ回路18は、入力レジスタ12からの128ビットの入力データから1ビットの出力データを選択する。アンド回路20は、対応するセレクタ回路18からのデータが有効な場合にのみ、当該データを出力レジスタ14の対応するビットに出力する。制御信号生成器16は各セレクタ回路18に、選択すべきビットの番号を示すセレクト信号を入力するとともに、各アンド回路20に、セレクタ回路18から入力されたデータが有効か無効かを示す信号を入力する。

(もっと読む)

情報処理装置およびプログラム

【課題】既存のプログラムをVLIW型プロセッサで実行可能であり、処理オーバーヘッドを低減した情報処理装置等を提供すること。

【解決手段】VLIW型プロセッサを備える情報処理装置は、メモリ内に保存されたプログラムをVLIW型命令に変換する命令変換プロセッサを有し、プログラムに応じてレジスタで命令変換プロセッサの制御ソフトウェアを設定することで、制御ソフトウェアを切り替える。

(もっと読む)

情報処理装置

【課題】所定の命令実行により参照したデータの条件に応じて、その後の処理の切り替えを効率良く行う。

【解決手段】CPU(130)は、命令セットを構成する命令を実行する。上記命令セットには、メモリ空間上のデータを読み込むロード命令が含まれ、上記ロード命令で読み込まれたデータには、データリード分岐発生ビット領域を有するフォーマットタイプのデータが含まれる。上記CPUには、データリード分岐制御レジスタ(300,310)と、データリード分岐アドレスレジスタ(320,330)と、リードデータ解析部(60)とを含む。上記データリード分岐発生ビット領域に、データリード分岐発生を示すビット値が設定され、上記データリード分岐制御レジスタに、データリード分岐発生ビットが有効であることを示す値が設定されている場合に、上記データリード分岐アドレスレジスタに記憶されたアドレス値に分岐することで処理の切り替えが行われる。

(もっと読む)

マイクロプロセッサ

【課題】用途に応じて同一マイクロプロセッサを使い分ける場合に、命令デコード、命令実行などにより規定される最大動作周波数の制約が発生する。

【解決手段】本発明は、例えば、用途に応じて、最大動作周波数を可変にするために、命令または命令セットの一部を無効化させることを特徴とする。一例として、命令を、メモリから読み出してフェッチする命令フェッチ部と、命令フェッチ部でフェッチした命令に対するデコード処理を行う命令デコード部と、デコード後の命令に対する処理を実行する命令実行部とを有して構成されるマイクロプロセッサにおいて、前記命令デコード部が、外部設定値を入力とし、外部設定値によって、一部の命令をデコード対象から除外すること、または低速化させることを特徴とする。

(もっと読む)

マイクロプロセッサ及びその制御方法

【課題】マイクロプロセッサの処理速度を向上させること。

【解決手段】マイクロプロセッサは、データを格納する第1のレジスタセットと、第1のレジスタセットから退避させたデータを格納するとともに、格納したデータを第1のレジスタセットに復帰させる第2のレジスタセットと、第1のレジスタセットから第2のレジスタセットにデータを退避させるとともに、第2のレジスタセットから前記第1のレジスタセットにデータを復帰させるレジスタI/Fと、スタックメモリに退避させるレジスタの情報を退避レジスタ情報として生成する退避レジスタ情報生成部と、第2のレジスタセットに格納されたデータ及び退避レジスタ情報をスタックメモリに退避させるとともに、退避レジスタ情報を読み出してスタックメモリに退避させたデータを第2のレジスタセットに復帰させるスタックI/Fと、を有する。

(もっと読む)

同時マルチスレッディングプロセッサ、制御方法、プログラム、コンパイル方法、及び情報処理装置

【課題】同時マルチスレッディングプロセッサにおいて、スレッドの実行時間を削減する。

【解決手段】同時マルチスレッディングプロセッサは、デコード後に複数のスレッドで実行されるように、該複数のスレッドのうち、該命令が実行されるスレッドを識別するためのスレッド識別子が付加された、単一のスレッドに属する複数の命令をフェッチするフェッチ手段と、前記フェッチ手段によりフェッチされた前記複数の命令をデコードし、前記複数のスレッドを生成し、それぞれの該命令に付加された前記スレッド識別子の示すスレッドに、該命令を割り当てるデコード手段と、前記デコード手段により生成された前記複数のスレッドを並列に動作させることにより、前記複数の命令を実行する実行手段と、を有する。

(もっと読む)

乗累算演算を実行するための装置および方法

【課題】乗累算演算を実行するデータ処理装置及び方法を提供する。

【解決手段】該データ処理装置は、制御信号に応答して、入力データ要素において、データ処理演算を実行するデータ処理回路を含む。命令デコーダ回路は、入力オペランドとして、第1入力データ要素、第2入力データ要素及び述語値を指定する述語化された乗累算命令に応答して、データ処理回路を制御するように制御信号を生成し、第1入力データ要素および前記第2入力データ要素を乗算し、乗算データ要素を生成し、該述語値が第1の値を有する場合、該乗算データ要素を初期累算データ要素に加算して結果累算データ要素を生成し、該述語値が第2の値を有する場合、該初期累算データ要素から該乗算データ要素を減算して、該結果累算データ要素を生成することで、乗累算演算を実行する。本発明は、パフォーマンス、エネルギー消費及びコード密度を改善する。

(もっと読む)

データプロセッサ

【課題】プレフィックス付きの命令を含む命令セットにおいて効率的なスーパースカラ命令発行と低消費電力とを実現する。

【解決手段】命令コードに対して、プレフィックスコードか、それ以外の命令コードかを判定し、その判定結果と前記16ビットの命令コードとを出力する命令フェッチ部(FTC)を採用すると共に、その判別結果に基づいて命令コードデコードするデコーダ(BDYDEC1,BDYDEC2)とプレフィックスコードをデコードするデコーダ(PRFDEC1,PRFDEC2)とを別々に配置する。さらに、プレフィックスはこれが修飾する16ビットのような固定長命令コードよりも先にデコーダに供給される。プレフィックスコードの後続の固定長命令コードは、プレフィックスコードのデコーダと同じパイプライン(Pipe1,Pipe2)のデコーダに供給される。

(もっと読む)

データ処理装置、履歴保存装置、データ処理方法およびプログラム

【課題】値再利用(メモ化:Memoization)の際、実行結果を保存しておくメモリから実行結果を退避させることにより、値再利用の効率を改善させる。

【解決手段】履歴メモリ430は、実行結果が再び利用される再利用区間の実行結果を実行履歴として保持する。主記憶部130は、再利用区間のうち実行が反復される反復再利用区間の実行結果を退避履歴として保持する。履歴制御部510は、反復再利用区間の実行結果であるループ個別履歴に基づいて、退避履歴およびループ代表履歴を生成する。これにより、反復再利用区間の実行結果を退避履歴として主記憶部130に退避するとともに、その実行結果を含むループ個別履歴の代わりにループ代表履歴を履歴メモリ430に登録する。

(もっと読む)

情報処理装置及びベクトル型情報処理装置

【課題】レジスタ・リネーミング機構を実装するプロセッサを備えた情報処理装置におい、プログラムを最適化するだけの手段では回避できないメモリアクセスやレジスタの解放待ち時間を回避すること。

【解決手段】レジスタ・リネーミング機構を実装すると共に、図1(a)に示すレジスタの使用状況の下で、ユーザ(プログラマ等)は、命令セットに導入した専用命令(論理レジスタに割り当てが可能な未使用の仮想レジスタの数を増加または減少させる命令)を発行し、実行させる。これにより、未使用の仮想レジスタの数を図1(b)、図1(c)に示すように変更できるので、ソフトウェアによって、それ自身のプログラム特性に最適化したレジスタの利用を図ることが可能となる。また、レジスタ上のデータをメモリへ退避するようなメモリアクセスの発生や、レジスタの解放待ち時間の発生が抑制されるので、処理性能を向上させることができるようになる。

(もっと読む)

マイクロコンピュータ

【課題】汎用レジスタの使用効率を最適化することが可能なマイクロコンピュータを提供すること。

【解決手段】制御部13は、命令コードのデコード結果に応じて、命令の実行を制御する。GRAレジスタ32は、複数の汎用レジスタのそれぞれに対するアクセス属性を記憶する。モード記憶部31は、CPUの動作を制御するためのモードを記憶する。そして、レジスタアクセス許可判定回路33は、制御部13から汎用レジスタに対してアクセス要求がある場合に、GRAレジスタ32に記憶されるアクセス属性およびモード記憶部31に記憶されるモードに応じて、当該汎用レジスタに対するアクセスを許可するか否かを判定する。したがって、モードに対応して使用される汎用レジスタの本数を変更することができ、汎用レジスタの使用効率を最適化することが可能となる。

(もっと読む)

データをシャッフルするための方法及び装置

【課題】効果的にデータをシャッフルするための方法及び装置を提供すること。

【解決手段】一実施例の方法は、L個のデータ要素を有する第1オペランドとL個の制御要素を有する第2オペランドとを受け取ることからなる。各制御要素に対して、当該制御要素により指定された第1オペランドデータ要素からのデータは、それのゼロクリアフィールドが設定されていない場合に関連付けされた結果のデータ要素位置にシャッフルされ、それのゼロクリアフィールドが設定されていない場合、関連付けされた結果のデータ要素位置にゼロが配置される。

(もっと読む)

演算装置及び電子機器

【課題】多重ループ処理を効率良く実行できる演算装置及び電子機器等を提供すること。

【解決手段】演算装置は、命令をデコードする命令デコード部170と、デコード結果に基づいて、第1、第2のループ処理で実行される命令の開始アドレスが設定される第1、第2のループ開始アドレス用レジスター140、150と、デコード結果に基づいて、第1、第2のループ処理で実行される命令の命令数が設定される第1第2のループ命令数レジスター110、210と、デコード結果に基づいて、第1、第2のループ処理のループ回数が設定される第1、第2のループ回数レジスター120、220と、デコード結果に基づいて、第1、第2のループ処理を実行する命令実行部190とを含む。

(もっと読む)

半導体集積回路及びレジスタアドレス制御装置

【課題】既存の半導体集積回路に対して機能の追加や修正がある場合でも、当該既存の半導体集積回路で作成したソフトウェアを使用可能、かつ、CPUの性能を向上可能な半導体集積回路及びレジスタアドレス制御装置を提供すること。

【解決手段】半導体集積回路110は、モード1からモードN(120、130、140)に対応して、アドレスビットの割り当てを組み換えたレジスタマップ1〜レジスタマップN(121、131、141)を有する。各レジスタマップは、対応するモードによって選択することができ、モードを切替えることで、いずれかのレジスタマップが使用可能となる。

(もっと読む)

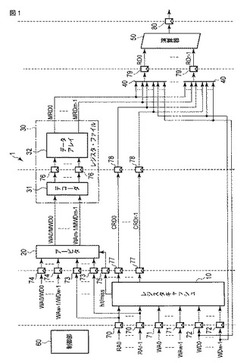

半導体集積回路

【課題】性能低下を招くことなく回路面積を削減出来る半導体集積回路を提供すること。

【解決手段】データを保持する第1メモリ30と、前記第1メモリ30に対するキャッシュメモリとして働く第2メモリ10とを備え、前記データに対する読み出し処理と書き込み処理とを複数の処理ステージによりパイプライン実行する半導体集積回路1であって、前記読み出し処理の対象となるデータを前記第1メモリ30から読み出すと決定された場合に、該データの前記第1メモリ30からの読み出しを前記処理ステージのいずれかRR、RR/CRにおいて行う。

(もっと読む)

情報処理装置

【課題】マイコンなどの情報処理装置のレジスタ拡張を行う場合、拡張レジスタにアクセスするには、命令コードの追加・変更やレジスタ切り替えのための操作が必要になる。

【解決手段】命令メモリ1と、データメモリ9と、命令メモリから読み出された命令に従って制御信号を生成する命令制御部4と、命令制御部による制御信号に従ってデータメモリに対してアクセスを行うロード・ストアユニット10と、命令制御部による制御信号に従って演算を行う演算器5,6と、演算器5で用いるデータを格納する標準レジスタ群7と、演算器6で用いるデータを格納する拡張レジスタ群8と、選択信号A3により標準レジスタ群7と拡張レジスタ群8とのいずれかを選択する選択手段12と、選択手段12に対し選択信号A3を出力する選択条件判定手段13とを備え、選択条件判定手段13は、装置内部の特定の状態信号に基づいて選択信号A3を生成する。

(もっと読む)

プロセッサ、プロセッサのデータ処理方法、情報処理装置

【課題】 大容量のレジスタファイルから小さいレイテンシで大量のデータを効率よく計算することができるプロセッサを提供する。

【解決手段】 プロセッサは、演算手段と、演算手段にクロスバースイッチを介して接続する複数の少ポート大容量のRAMをインタリーブ化したレジスタファイルと、演算手段の演算結果を格納し、クロスバーを介して演算結果をレジスタファイルに書き戻すと共に、クロスバーをバイパスするパスを介して演算手段に格納データを出力するレジスタキャッシュとを含む。

(もっと読む)

1 - 20 / 62

[ Back to top ]