Fターム[5B042GA15]の内容

デバッグ、監視 (27,428) | 対象プログラム、装置 (3,643) | 対象システム、対象装置 (2,500) | キャッシュメモリを有するもの (24)

Fターム[5B042GA15]に分類される特許

1 - 20 / 24

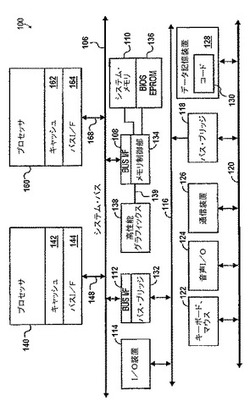

複数のデータ・エレメントの収集及び分散

【課題】複数のデータ・エレメントの収集及び分散におけるオーバーヘッドを低減するプロセッサを提供する。

【解決手段】効率的なデータ転送処理は、単一の命令が複数のデータ・エレメントに対する第1の記憶域と第2の記憶域との間の転送処理を指定し、プロセッサ装置140,160によりデコードする段階、前記プロセッサ内の演算実行部による実行のために単一の命令を発行する段階、単一の命令の実行中に例外の発生を検出する段階、及び該例外に応答して、該例外を分配する前に、未解決のトラップ又は割り込みを例外ハンドラに分配する段階、により達成されうる。

(もっと読む)

クリティカルパスに基づく解析のための性能モニタリングアーキテクチャ強化

【課題】マイクロアーキテクチャの性能をモニタリングし、そのモニタリングされた性能に基づいてマイクロアーキテクチャをチューニングする方法及び装置を提供する。

【解決手段】シミュレーション、解析上の推論、リタイアメントプッシュアウト測定、全体実行時間、およびインスタンス当たりのイベントコストを決定する他の方法によって性能がモニタリングされる。インスタンス当たりのイベントコストに基づき、マイクロアーキテクチャおよび/または実行ソフトウェアは、性能を強化すべくチューニングされる。

(もっと読む)

情報処理装置およびデータの復旧方法

【課題】記憶装置に書き込まれていないデータがメモリ内にある状態でオペレーティングシステムがクラッシュしても、メモリ内のデータを記憶装置に復旧する。

【解決手段】情報処理装置は、メインメモリと、第1記憶装置と、第2記憶装置と、第1書込手段と、第2書込手段と、第3書込手段と、を具備する。第1記憶装置は、オペレーティングシステムを格納する。第1書込手段は、第2記憶装置に書き込まれるデータをメインメモリに書き込み、データの第2記憶装置内の書き込まれる位置を示す書き込み位置情報をメインメモリに書き込む。第2書込手段は、オペレーティングシステムのクラッシュ時に、メインメモリ内のデータおよび書き込み位置情報を第1記憶装置内の書込領域に書き込む。第3書込手段は、クラッシュ後の起動時に、第1記憶装置内のデータを第1記憶装置内の書き込み位置情報に基づいて第2記憶装置に書き込む。

(もっと読む)

デバッグ支援装置及びデバッグ支援用プログラム

【課題】並列に実行されるプログラムの潜在的な不具合を検出することができるデバッグ支援装置およびそのためのプログラムを提供する。

【解決手段】デバッグ支援装置は、プログラムを並列に実行する複数のCPUの動作を模擬する複数のCPU模擬部C0,C1,C2と、前記複数のCPU によって共有される共有資源の模擬部Mと、各CPU模擬部と前記共有資源の模擬部間において発生した所定のイベントを検出するイベントモニタ部C3,C13,C23と、並列実行される前記プログラムのスレッド間の相対的な順序関係の情報を記録するためのベクトルクロック表と、前記相対的な順序関係の情報に基づいて、スレッド間の順序関係が半順序関係となるイベントが発生したか否かを判定し、前記半順序関係であるイベントが発生したときに、前記共有資源に対するキャッシュ操作に関する履歴情報を記録するカスタム部CPとを有する。

(もっと読む)

シミュレーション装置、シミュレーション方法、及びシミュレーション用プログラム

【課題】従来技術のシミュレータ(シミュレーション装置)では、命令がデバッガのメモリウィンドウなどで直接編集された場合、デコード・キャッシュの内容と異なってしまい、正しい命令の実行が行えない。

【解決手段】シミュレータ(シミュレーション装置)は、メモリが書き換えられ、その内容が命令であれば、該当する命令のデコード・キャッシュに変更フラグを立てる命令変更通知部と、該当命令実行時に、デコード・キャッシュに変更フラグがあるかを検出し、変更フラグがあれば、再フェッチ・デコードを行う実行シミュレーション部を有する。

(もっと読む)

マイクロプロセッサ及びマイクロプロセッサのデバッグ方法

【課題】マイクロプロセッサの内部の論理不正動作の調査を容易化できるようにする。

【解決手段】論理動作不正が発生する命令列を、比較命令格納バッファ40に記憶し、プログラムを動作させ、命令比較部41で、実際に実行している命令と比較命令格納バッファ40に記憶されている命令とを比較し、コピー指示のある命令を検出すると、偶数個のコピー命令を生成する。後続のコピーされた偶数個の命令は、前方に存在する命令が完了するまで実行しない命令間隔に設定しており、タイミングや競合による論理動作不正を発生しない。命令列中の最後の命令から1命令ずつコピー指示を前の命令に移動させながらプログラムを実行し、多数決処理チェックの結果を確認することで、論理動作不正の発生する命令を特定する。

(もっと読む)

キャッシュシステム

【課題】コストの増大を抑制でき、デバッグの実行に要する時間の低減を可能とするキャッシュシステムを提供すること。

【解決手段】複数に分割されたメモリ領域を単位としてキャッシュ容量を変更可能であって、デバッグモードにおけるアクセスに関するアクセス履歴情報を作成する履歴作成手段である履歴作成部112を有し、デバッグモードにおいて、複数に分割されたメモリ領域のうちの少なくとも一つのメモリ領域へのキャッシュアクセスが制限され、キャッシュアクセスが制限されたメモリ領域へアクセス履歴情報が格納される。

(もっと読む)

処理装置および履歴取得方法

【課題】ユーザプログラム実行時の処理装置の内部の動作状況を確認する技術を提供する。

【解決手段】処理装置は、一連の命令を含む実行対象のプログラムを実行するプロセッサ部を含む処理装置であって、処理装置の動作履歴を記録する履歴記録部と、履歴記録部による記録処理を制御するとともに、履歴記録部に記録された動作履歴を読み出す管理部と、実行対象のプログラム中の命令のうち、管理部宛の制御命令を管理部に引き渡す処理を起動する起動命令を検出し、起動命令にしたがって制御命令を管理部に引き渡す入力部と、管理部が読み出した動作履歴を管理部から受け取る出力部とを備える。

(もっと読む)

データ処理装置の監視およびその監視データの集計

【課題】開始と終了イベントとの間に生じるデータ処理装置内の複数のアドレス指定可能場所へのアクセスを監視するための監視回路を提供する。

【解決手段】前記監視回路は、監視される前記複数のアドレス指定可能場所を識別するデータを保存するためのアドレス場所保存と、監視データ保存とを含み、前記監視回路は、前記開始イベントの検出に応答して、前記複数のアドレス指定可能場所へのアクセスを検出し、前記監視データ保存内に前記検出されたアクセスの集計に関連する監視データを保存し、前記監視回路は、前記終了イベントの検出に応答して、前記監視データの収集を停止し、前記監視回路は、消去イベントの検出に応答して、前記保存された監視データを出力し、前記監視データ保存を消去する、データ処理装置が開示される。

(もっと読む)

プロセッサの性能監視のための方法、性能モニタ、およびシステム

【課題】プロセッサから性能パラメータを収集するための改良された方法およびシステムを提供する。

【解決手段】本発明はコンピュータ・アーキテクチャに関し、とりわけ、プロセッサの性能を評価することに関する。性能モニタは、プロセッサのL2キャッシュ・ネスト内に配置することができる。性能モニタはL2キャッシュ・アクセスを監視し、プロセッサ・コアをL2キャッシュ・ネストに結合するバスを介して、1つまたは複数のプロセッサ・コアから性能データを受け取ることができる。一実施形態では、バスは、プロセッサ・コアから性能モニタへ性能データを転送するための追加のラインを含むことができる。

(もっと読む)

プロセス状態監視装置

【課題】各処理プロセスを実行する際のキャッシュのヒット率を向上させることにより、ホストからのトランザクション処理の応答時間を短縮する。

【解決手段】処理分散装置は、複数の処理プロセス実行手段と、ディスパッチャプロセス実行手段とを備える。処理プロセス実行手段は、各々が処理プロセスを実行する。ディスパッチャプロセス実行手段は、ホストから要求されるなどして発生した処理を、処理プロセス実行手段に振り分ける。ここで、各処理プロセス実行手段は、キャッシュを有し、キャッシュをクリアするとキャッシュクリア通知をディスパッチャプロセス実行手段に送信する。ディスパッチャプロセス実行手段は、処理プロセス実行手段に処理を振り分ける際、キャッシュクリア通知を利用して各処理プロセスのキャッシュ生存時間を監視し、キャッシュ生存時間が最も長い処理プロセス実行手段に処理を割り振る。

(もっと読む)

プロセッサ装置およびプロセッサデバッグ方法

【課題】デバッグ回路の削減を図るとともに、高速なアドレス比較部を用いなくてもよいプロセッサ装置を提供する。

【解決手段】演算処理部11と、演算処理部のトレースデータを格納するトレースメモリ12と、演算処理部からのメモリアクセスアドレスに従って外部メモリ30に対するアクセス制御を行うバスコントローラ20を備える。トレースメモリ12は、外部メモリにおける命令コードまたはデータ上における置換対象に対応した置換制御用アドレスも格納するように構成される。バスコントローラ20は、メモリアクセスアドレスとトレースメモリからの置換制御用アドレスとを比較するアドレス比較部21と、外部メモリから読み出された命令コードまたはデータについて、アドレス比較部による比較結果が所定の条件を満たす場合は、別の命令コードまたはデータに置き換える置換処理部24を有する。

(もっと読む)

データ処理システムにおけるキャッシュトランザクションのための方法及び装置

複数の新規のスヌープトランザクションタイプ(60)が記載される。その一部がリクエスト内にアドレス情報を含み、その他がリクエスト内にキャッシュエントリ情報を含む。一部の応答(61)がタグアドレス情報を含み、一部の応答は含まない。一部が、トランザクションのデータ部中にデータバスライン(41)上でタグアドレス内容を提供する。これらの新規のスヌープトランザクションタイプは、データ処理システムのデバッグ中に極めて有用である。 (もっと読む)

タスク遷移図表示方法及び表示装置

【課題】マルチプロセッサシステムにおけるタスク遷移とキャッシュミスなどの性能情報とを関連させた分析を可能にし、またシステム処理の並列度とタクス遷移との関連を明確にする。

【解決手段】トレース情報と、トレース情報に対応する性能情報とをメモリから取得し、トレース情報に基づくタスク遷移状態と性能情報とを遷移図上に重畳させて表示する。またトレース情報に基づいて複数のプロセッサの動作状態に対応する並列度を求め、その並列度をタスク遷移図と時間的に同期させて表示する。

(もっと読む)

プロセッサおよびプロセッサ制御方法

【課題】メモリ領域の不整合の場合の原因解析の容易化および処理速度の向上を、簡単な回路構成で実現するプロセッサを提供すること。

【解決手段】プロセッサ100は、CPUコア101のブレークポイントに定められたアドレスと、CPUコア101がアクセスするデータキャッシュ102のアドレスとの一致判定を比較器104でおこなう。また、データキャッシュ102は、アクセスによるキャッシュヒット/ミスの検出結果を表すキャッシュヒット信号を出力する。また、AND回路106は、比較器104の一致判定信号と、データキャッシュ102のキャッシュヒット信号とに基づいてCPUコア101にデータブレーク信号を出力し、ブレークを実行させる。

(もっと読む)

コンピュータシステムおよびコンピュータシステムにおけるメモリダンプ制御方法

【課題】メモリダンプの書き込み時間をより短縮する。

【解決手段】システムクラッシュ発生時にメモリ12の内容をダンプしてダンプ格納部24に記録する。キャッシュメモリ部23は、データ格納部25の内容をコピーして保持するリードキャッシュ領域と、データ格納部25への書き込みデータを一時保持するライトキャッシュ領域とを有する。ライト制御部21は、キャッシュメモリ部23におけるキャッシュ領域を動的に割り当てるようにキャッシュメモリ部23を制御する。メモリダンプの指示があった場合に、リードキャッシュ領域と、ライトキャッシュ領域の内でデータ格納部25への書き込みが終了しているライトキャッシュ領域とを、ダンプするメモリ内容を一時保持するダンプキャッシュ領域23dとして割り当てる。

(もっと読む)

クリティカルパスに基づく解析のための性能モニタリングアーキテクチャ強化

ここに記載の方法および装置は、マイクロアーキテクチャの性能をモニタリングし、そのモニタリングされた性能に基づいてマイクロアーキテクチャをチューニングする。シミュレーション、解析上の推論、リタイアメントプッシュアウト測定、全体実行時間、およびインスタンス当たりのイベントコストを決定する他の方法によって性能がモニタリングされる。インスタンス当たりのイベントコストに基づき、マイクロアーキテクチャおよび/または実行ソフトウェアは、性能を強化すべくチューニングされる。 (もっと読む)

ソフトウェアアプリケーションのストライドプロファイリング方法および装置

【課題】ソフトウェアアプリケーションのストライドプロファイリングのための方法および装置を提供する。

【解決手段】システムの一例では、データキャッシュミスなど何らかのイベントにより起きたメモリアクセス命令に関連する命令アドレスとデータアドレスとを報告するためにハードウェアパフォーマンスカウンタを使用する。同じ命令アドレスが2つ以上のデータアドレスに関連するとき、2つのデータアドレス間の差が報告される。同じ命令に対しそれら2つ以上のデータアドレス差が記録されると、システムは、2つ以上の差の最大公約数となる命令に関連するストライドを決定する。このストライドは、データキャッシュプリフェッチを最適化するため、コンパイラによって使用されることもできる。さらに、検査位相とスキッピング位相とを繰り返すことにより、データキャッシュミスのアドレスを監視することに伴うオーバーヘッドも減らすことができる。データキャッシュミスは、スキッピング位相の間より検査位相の間で多く見つかる。  (もっと読む)

(もっと読む)

メモリダンプ採取方法

【課題】

主記憶装置にメモリダンプ手順を読み込むことなくメモリダンプを採取することを可能とするメモリダンプ採取方法を提供する。

【解決手段】

キャッシュメモリ11を備えたCPU10と、CPUが使用する主記憶装置30と、プログラムが使用していたメモリ内容を外部記憶装置50にダンプするためのメモリダンプ手順を格納したROM20とを備え、メモリダンプ手順をキャッシュメモリ11に格納し、格納したメモリダンプ手順にしたがってプログラムが使用していたメモリ内容を外部記憶装置50にダンプする計算機のメモリダンプの採取方法であって、計算機に障害が発生したとき、該計算機を再起動したのち、キャッシュメモリ11を主記憶装置30のアドレス空間の一部に対応させ、主記憶装置30の初期化を行う前に、キャッシュメモリ11に前記メモリダンプ手順21を読み込ませて該手順を実行することによりメモリダンプを採取する。

(もっと読む)

CPUメモリアクセス解析装置

【課題】システムLSIにおいて、CPUメモリアクセス解析によるソフトウェアの処理速度面での最適化を行うため、システムの振舞いに影響を与えず、低いバンド幅でCPUメモリアクセス状態を出力すること。

【解決手段】システムLSI内に、キャッシュミスヒット信号を検出するキャッシュアクセス検出手段と、プロセス切替を検出するプロセス切替検出手段と、前記プロセス切替信号を受信した場合にはプロセス切替情報を、前記キャッシュミスヒット信号を受信した場合にはキャッシュミスヒット情報をシステムLSI外部に出力するように制御する出力制御手段と、前記出力制御手段に従ってプロセス切替情報、あるいは、キャッシュミスヒット情報を生成しシステムLSI外部に出力する出力選択手段を有し、キャッシュミスヒット時のメモリアクセス状態をプロセスIDに対応付けられた仮想アドレスとして出力することを特徴とする。

(もっと読む)

1 - 20 / 24

[ Back to top ]