Fターム[5B042JJ13]の内容

デバッグ、監視 (27,428) | 動作監視、異常又は誤りの検出 (3,508) | 監視内容 (773) | プログラムの暴走、ループの検出 (112)

Fターム[5B042JJ13]に分類される特許

1 - 20 / 112

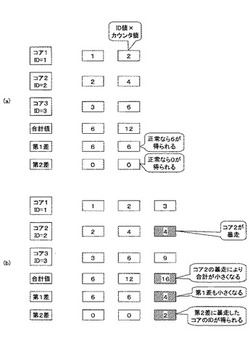

コア監視装置、情報処理装置

【課題】マルチコアマイコンにおいて、異常の生じたコアをソフト的な負荷増大を抑制して判別可能なコア監視装置を提供すること。

【解決手段】複数のコアから共通の周期で通知を受け付けるコア監視装置17であって、 コアから通知を受け付けた際、各コアに固有のコア識別数値(例えば、カウンタ値×ID)をコア毎に生成するコア識別数値生成手段31と、複数のコアのコア識別数値を合計した合計値を算出する合計値算出手段32と、最後に算出された合計値を記憶する合計値記憶手段36と、合計値算出手段が算出した合計値と、合計値記憶手段に記憶された合計値との差である第一の差を算出する第一の差算出手段33と、第一の差を記憶する第一の差記憶手段37と、第一の差算出手段が算出した第一の差と第一の差記憶手段に記憶された第一の差との差である第二の差を算出する第二の差算出手段34と、を有する。

(もっと読む)

モバイル端末のプログラム起動保全システム

【課題】モバイル端末内のエージェントプログラムが停止した場合に、極短時間でこれを回復させる保全技術を提供する。

【解決手段】エージェントプログラム14は、一定間隔でハートビートを発信するハートビート発信部24を備える。OSフレームワーク18は、ハートビートをヘルパープログラム16に伝達するハートビート伝達部28と、ヘルパープログラム16からの要請に基づいてエージェントプログラム14を再起動させると共に、ハートビートを伝達する時点でヘルパープログラム16が起動状態にない場合にこれを再起動させるプログラム起動部30を備える。ヘルパープログラム16は、ハートビートを受領する度にタイマーをリセットして時間を計測し、一定の時間を経過しても次のハートビートが伝達されない場合に、OSフレームワーク18にエージェントプログラム14の再起動を要請するエージェント監視部26を備える。

(もっと読む)

プログラム検査装置

【課題】プログラムの問題箇所を容易に発見できる妥当性検査を行うことができ、システムプログラマのデバック効率を向上する。

【解決手段】IEC 61131-3に準拠した命令語を用いるプログラムのオブジェクトファイルを取得し、ステップ順に機械語のスタック操作をシミュレーションして得られた変数、あるいは定数を用いて、プログラムの動作不備を引き起こす可能性のある箇所および要因を検出する検出部12Cと、検出部12Cで検出された箇所および要因を表示する表示処理部12Dと、を備え、検出部12Cは、シミュレーションの過程で得られる変数、あるいは、定数を用いて、変数の領域外アクセスの箇所を検出する機能12C1と、無限ループの可能性がある箇所を検出する機能12C2と、データの精度が欠落する可能性がある箇所を検出する機能12C3と、条件が成立しない可能性のある箇所を検出する機能12C4と、の少なくとも1つを含む。

(もっと読む)

制御装置

【課題】CPUの暴走を検知して正常な状態に復帰させるためにWDT回路は有効であるが、複数のCPUを備えた制御装置では、全てのCPUに各々WDT回路を設けたのではコストが高くなると共に制御装置が大型化するという問題が生じる。

【解決手段】メインCPUが暴走した場合にメインCPUをリセットして正常化するウォッチドッグタイマ装置をメインCPUに対して設けると共に、メインCPUがサブCPUの作動状態を監視し、サブCPUが暴走した場合にはメインCPUがサブCPUをリセットする。

(もっと読む)

情報処理装置、情報処理方法及びプログラム

【課題】外部装置が接続されたときに、動作ログを必要な場合にのみ外部装置に保存する情報処理装置を提供する。

【解決手段】情報処理装置の一例である画像処理装置は、動作ログをログ領域250に保持し、システム監視・デバッグログプロセス221がUIを制御するUI制御プロセス220がエラー状態にあるか否かを監視する。USBドライバ230がUSBメモリメディア140の装着を検知すると、システム監視・デバッグログプロセス221は、UI制御プロセス220が正常に動作しているかの生存確認を行い、エラー状態にあると判定した場合に、ログ領域250に保持されている動作ログをUSBメモリメディア140に保存する。

(もっと読む)

端末装置並びにフリーズ検出方法及び端末装置の制御方法

【課題】細かい設定をすることなく、自動的にフリーズ状態を検出し、リセット処理等を行う端末装置の提供。

【解決手段】端末装置は、電源からCPUに供給される電流値を測定する電流測定部と、前記CPUをリセットするリセット制御部と、前記CPUと独立して動作し、動作モードに反した電流値の定常状態が観測された場合、前記リセット制御部に前記CPUをリセットさせる電流監視部と、を備える。

(もっと読む)

プログラム実行状況監視装置、および実行状況監視プログラム

【課題】多くの記憶容量を必要とすることなくプログラムが正常に実行されているか否かを監視できる技術を提供する。

【解決手段】実行状況監視装置1は、第1の値および第2の値のうちの直近の時刻に更新された値との対応関係が所定条件を満たすための第1の操作を行うことで求められる値である第1新値に、第1の値および第2の値のうちの直近の時刻に更新されていない値を更新し(S120,S140)、第1新値に対して第2の操作を行うことで操作値を生成する(S130,S150)。そして、操作値に対して第1の操作および第2の操作を相殺する操作を行うことで求められる値である第2新値に、第1の値および第2の値のうちの直近の時刻に更新されていない値を更新し(S230,S240)、第1の値と第2の値との対応関係が所定の関係になっているか否かを判定する。

(もっと読む)

画像形成装置、及び画像形成装置における動作監視方法

【課題】

CPUの動作を監視するウォッチドッグタイマ(WDT)の不要な動作を防止して消費電力を低減する。

【解決手段】

CPU110と、CPU110の動作を監視し、CPU110の異常動作を検知して正常動作に復帰させるWDT112と、自装置を構成する各機器の動作状態に関する動作情報を取得する動作情報取得部116と、取得された前記動作情報から特定される動作状態が予め定めた条件を満たすときに、WDT112の動作をOFFにする監視制御部118と、を有する。

(もっと読む)

暴走検出装置

【課題】プログラムの暴走を精度良く検出可能な暴走検出装置を提供する。

【解決手段】複数の関数から構成されたプログラムの暴走を検出する暴走検出装置であって、前記プログラムの各関数に従って所定の処理を実行する処理部と、前記処理部による制御に応じて暴走判定値を記憶する記憶部と、を備え、前記処理部は、各関数の処理実行前に、前記記憶部に記憶されている暴走判定値に基づいて、本関数が正規の順序で呼出された関数か否かを判定し、否の場合に前記プログラムが暴走していると判断する。

(もっと読む)

P−RUN信号出力装置、組込制御装置

【課題】組込ソフトウェアが異常動作したときは確実にリセット信号を出力し、組込ソフトウェアが正常動作している間はリセット信号を不要に発生させないようにすることのできる技術を提供することを目的とする。

【解決手段】本発明に係るP−RUN信号出力装置は、優先度の異なる複数の組込プログラムの実行状態を監視し、システムクロックが示す時刻と各組込プログラムの前回実行時刻との差分が所定閾値を超えている場合は、P−RUN信号を出力しない。また、P−RUN信号を出力するか否かを判断してP−RUN信号を出力する処理を、組込プログラムのなかで最も優先度の高いもの以上の優先度で実行する。

(もっと読む)

マイクロコンピュータ制御システム、並びにそれを用いた充電装置および太陽光電源システム

【課題】マイクロコンピュータ制御システムに設けられた複数のマイクロコンピュータのうちのいずれかが暴走状態に陥ったとしても、その暴走状態を認識することができるマイクロコンピュータ制御システムを提供する。

【解決手段】複数のマイクロコンピュータ5、6を備えたマイクロコンピュータ制御システムであって、前記複数のマイクロコンピュータ5、6の各々が、自己の動作状態を他のマイクロコンピュータ6、5へ伝達するための動作確認信号A1、A2を発生する動作確認信号発生部7、8と、他のマイクロコンピュータ6、5からの動作確認信号A2、A1を基に当該他のマイクロコンピュータ6、5の動作状態を認識する動作状態認識部(動作状態判定制御部9、10)とを備える。

(もっと読む)

半導体装置及びレジスタの保護方法

【課題】マイクロコンピュータにおけるプログラムの暴走時にレジスタの値を誤書き込みからより確実に保護する。

【解決手段】半導体装置は、タイマ4と、保護回路5とを具備する。タイマ4は、保護対象のレジスタ6a、7aへの書き込みを制御する制御信号S1に応答して、所定の第1時間経過後にタイマ信号CMPを出力する。保護回路5は、タイマ信号CMPを受信するまで書き込みを無効とし、タイマ信CMP号を受信開始後の所定の第2時間内の書き込みを有効とする。

(もっと読む)

ストール監視装置、ストール監視方法及びプログラム

【課題】BMC等のコントローラを二重化することなく、BMC等のコントローラにストールが発生した場合でも、コンピュータシステムを継続して動作させる。

【解決手段】コンピュータシステム100を構成するプロセッサ103、メモリ105及びI/O107の電源以外を管理するBMC11と、プロセッサ103、メモリ105及びI/O107の電源を管理する電源コントローラ13とを備える。BMC11は、電源コントローラ13によりリセットされるリセット部11aと、電源コントローラ13のストールを検出するストール検出部11bとを備える。電源コントローラ13は、BMC11によりリセットされるリセット部13aと、BMC11のストールを検出するストール検出部13bとを備える。

(もっと読む)

情報処理装置、半導体集積回路装置および異常検出方法

【課題】CPUの異常動作を検出する。

【解決手段】CPU(100)と、割り込みカウンタ(410)と、カウンタ異常値検出回路(430)とを具備する。割り込みカウンタ(410)は、CPU(100)への割り込みの要求を示す割り込み信号(INT)に応答して出力される割り込みを受け付けたことを示す割り込み開始信号(IRS)に基づいてカウント値をインクリメントし、割り込みに対応する処理が終了したことを示す割り込み終了信号に基づいてカウント値をデクリメントする。カウンタ異常値検出回路(430)は、カウント値(IRC)を所定の値と比較して異常を検出する。

(もっと読む)

コンピュータ、コンピュータの障害検知方法、及びプログラム

【課題】

コンピュータに生じた障害を、異常終了等に至る前に迅速に検知することを可能とする。

【解決手段】

コンピュータ1は、実行するプログラム132を構成する各プロセス132A、BがCPU110によって処理開始されてから処理終了するまでにわたって、プロセッサ使用時間とプロセッサ不使用時間とを順次複数回計測して取得し、所定の統計処理に従って、遷移時間802及び状態待機時間803を算出して記憶する。CPU110により前記プロセスのいずれかが処理されているときに、当該プロセスについて、前記プロセッサ使用時間及び前記プロセッサ不使用時間を計測して、逐次当該プロセスについて記憶されている遷移時間802及び状態待機時間803と比較し、当該比較結果が所定の判定基準を満たしていないと判定した場合に、当該プロセス処理中に障害が発生したと判定する。

(もっと読む)

CPU監視装置およびCPU監視プログラム

【課題】動作異常が発生したと判断する基準を変更することができる。

【解決手段】暴走監視装置1は、複数のプログラムと書き換え可能なデータファイル6とデータを記憶する領域とを有する記憶部3と、プログラムを実行する実行処理部21およびプロセスのタスク量を測定する測定処理部22を有する制御部2と、時刻を得るタイマ部4とを備え、同時期に複数のプログラムを実行可能なマルチプロセス機能を有する装置であって、測定処理部22が測定したプロセス毎のタスク量を記憶部3に記憶させる暴走監視処理部12と、データファイル6に記録された暴走監視周期値61の周期で暴走監視処理部12を機能させる周期実行処理部11と、データファイル6に記録された暴走閾値62と、記憶部3に記憶されたタスク量81とその1周期前のタスク量82との差分値である判定タスク量とを比較し、動作異常を判定する暴走判定処理部13とを備える。

(もっと読む)

マルチCPU構成装置及びその監視制御方法

【課題】マルチCPU構成装置及びその監視制御方法に関し、カードファームウェアが異常、又はMCUとカードファームウェアとの間の通信機能が異常になった場合でも、MCUによる該異常カードの監視制御を可能にする。

【解決手段】装置全体のメイン制御を司るメインCPU(MCU)と、装置内の各カードに実装され各カード固有の機能の処理を各カードのCPUで実行する各カードファームウェアとを有するマルチCPU構成装置において、MCUは、各カードファームウェアの異常を検出すると、該異常が検出されたカードファームウェアを、該MCUに割り当てられた空きメモリ領域にロードし、該異常が検出されたカードの警報処理312、パフォーマンス監視322、環境設定(Config)処理332、実装処理422、アクセス処理432を代行し、MCUで異常カードファームウェアの監視制御を代行処する。

(もっと読む)

情報処理システム及びその評価方法

【課題】モードを変更してもシステムを停止する必要がなく、システムの評価を効率的に行うことが可能な情報処理システムを提供する。

【解決手段】命令バッファ3のリタイヤカウンタ10を監視し、リタイヤカウンタ10が所定のしきい値11を超えたことを検知する手段、リタイヤカウンタ10が所定のしきい値11を超えた時には動作モードを通常モードから安定モードに変更する手段、安定モードに変更後に新規にコンテキストスイッチ7が発生した時に動作モードを通常モードに戻す手段を具備する。また、リタイヤカウンタ10が所定のしきい値11を超えた時にフェッチICをリタイヤIC15に更新してプログラムをリタイヤICから再開させる。

(もっと読む)

処理装置

【課題】処理部からのWDパルスなしに、処理部の動作状態の変化に対応して適切に異常を検出して安全性を高めることができる処理装置を提供する。

【解決手段】CPU10が機器を制御するために周期的に出力する制御パルス信号が、CPU10の動作を監視して異常を検出する監視回路13へも入力される。監視回路13では、CPU10からの制御パルス信号が、監視時間が経過するまでに出力されるか否かが判断され、出力される場合には正常、出力されない場合には異常と判断し、異常と判断した場合にはリセット出力部からCPU10へリセット信号を入力させる。CPU10は、制御パルス信号の周期が変化するような状態遷移を行なう場合、状態遷移を知らせる通知をASIC101へ出力し、監視回路13にて状態遷移に応じて監視時間を変更する。

(もっと読む)

情報処理装置、メモリダンプシステムおよびメモリダンプ方法

【課題】 装置が備えるオペレーティングシステムが正常に機能しない状態においても、当該装置の異常を検出し、異常に関する情報を装置の外部に退避させることができる情報処理装置、メモリダンプシステムおよびメモリダンプ方法を提供する。

【解決手段】 実施形態によれば、ウォッチドッグタイマのタイムアップにより情報処理装置10の異常を検出した場合、情報処理装置10のBMCコントローラ110はSMI/SCI割り込みを発生し、複数のCPUのうち動作する1つのCPUを選択し、選択された1つのCPUと協働してメモリダンプデータをネットワーク11に接続されているメモリダンプ受信サーバ30に送信する。

(もっと読む)

1 - 20 / 112

[ Back to top ]