Fターム[5B042JJ27]の内容

デバッグ、監視 (27,428) | 動作監視、異常又は誤りの検出 (3,508) | 異常又は誤りの検出方法 (1,125) | 単一計時手段で複数事象を監視 (14)

Fターム[5B042JJ27]に分類される特許

1 - 14 / 14

時間監視装置及び方法

【課題】1つのタイマ手段にて複数の処理の実行時間を監視する際に、その監視自体に異常が生じていないかを検知する。

【解決手段】既に獲得したリソースの獲得時間を監視している最中に新たなリソースの獲得を行うとき、タイマ回路18のカウンタ値と、新たなリソースの獲得時間の上限制約時間との差分時間を算出し、RAM16に退避させる。リソースの解放時には、差分時間の符号を判定した加算時間をカウント値に加算して、タイマ回路18が新たにカウントすべきカウント値を算出する。そして、タイマ回路18において、差分時間及び加算時間を計測し、計測した差分時間の合計時間と計測した加算時間の合計時間とが一致するか否か、および差分時間の計測回数と加算時間の計測回数とが一致するか否かを判定する。

(もっと読む)

処理装置

【課題】処理部からのWDパルスに基づき、より正確に処理部の動作異常を検出して安全性を高めることができる処理装置を提供する。

【解決手段】CPU10が正常時に周期的に出力するパルス信号が、複数の端子から出力され、CPU10の動作を監視して異常を検出する監視回路14へ入力される。監視回路14は、異常を検出した場合にCPU10を再起動させる再起動部として動作する。監視回路14は、CPU10の複数の端子からのパルス信号が、周期的に出力されているか否かを判断し、いずれも周期的に出力される場合には正常、いずれも出力されない場合には異常と判断してリセット信号を入力し、一部が出力されて他の一部は出力されない場合には断線が発生したことを検知して出力する。

(もっと読む)

電子機器の通信システム

【課題】マスタ制御部と複数のスレーブ制御部とがシリアル通信で接続された構成において、複数のスレーブ制御部毎にウォッチドッグタイマを設けなくとも、シリアル通信の異常時の保護を可能とする通信システムを提供する。

【解決手段】シリアル通信を制御するマスタ制御部101との間でシリアルデータの送受信を行なう複数のスレーブ制御部102と、複数のスレーブ制御部102に同時にリセットをかけるウォッチドッグタイマ105を備えた通信システムにおいて、複数のシリアル通信ラインのうち、少なくとも1系統を介して、マスタ制御部101からのウォッチドッグ信号をウォッチドッグタイマ105に入力する構成とした。

(もっと読む)

電子制御装置

【課題】

同一パッケージ内に複数のコアを持つマイコンであっても、1個の監視部のみで、マイコンの暴走を正しく監視する。

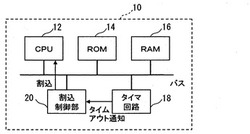

【解決手段】

WDC監視部19は、マイコン10から入力される周期的な出力に基づくWDC信号の周期性が崩れると、前記マイコンの異常発生を判定する。また、前記マイコン内の処理は、各々のコアからアクセス可能なRAM14内に各コア毎の更新領域を予め確保し、タイマ部16より複数のコアに対して一定周期でタイミングを通知する機能をもっている。前記タイマ部から通知されるタイミングに従って、全てのコアが各々のRAMを更新履歴が判るように更新する処理と、少なくとも一つのコアがRAMの更新履歴を判定し、前記WDC監視部19への出力処理を交互に行うことにより、前記WDC監視部19に対して一定周期のWDC信号の出力を行う。

(もっと読む)

シミュレーション方法、システム及びプログラム

【課題】 複数の異種ECUをもつシステムを、ソフトウェア的に効率的にシミュレートすること。

【解決手段】 各ECUエミュレータは、投機的にエミュレートされる。すなわち、ここで、ECUエミュレータや各物理装置シミュレータを論理プロセスと呼ぶことにすると、本発明によれば、クリティカル・パスを作らずに、各論理プロセスをできるだけ並列に実行させるために、各論理プロセスにおいて、入力イベントが届いていない場合でも、入力を予測して処理が進められる。このような投機的実行により、他の論理プロセスの出力を待つことなく、先行して処理を行うことにより、処理の並列性が高められる。そうして、もし遅れて受信する実際の入力と、予測して投機実行したときの入力が一致していない場合には、投機実行が失敗だったとして、その前の時刻に状態が戻され、その実際の入力に基づき、処理が再実行される。

(もっと読む)

異常検出方法および異常検出装置

【課題】より実用的な異常検出方法、およびその異常検出方法を実施する異常検出装置を提供する。

【解決手段】対象時系列データを取得し、取得した対象時系列データの各サンプルごとの距離を標準時系列データに基づいて算出する。各サンプルごとの距離を総距離で除して影響度を算出して、その影響度が所定の閾値を越えたときに警告表示する構成にする。この警告表示をグラフにして可視化することで、より分かり易くプロセスの異常の発生時期をプロセスを管理する側の人に伝えることができるようにする。

(もっと読む)

プログラムの暴走検出システムおよびプログラムの暴走検出方法

【課題】複数の基板を持つシステムにおいて、一つの基板にウォッチドッグタイマ機能を持たせるだけで、その他の基板のプログラムの暴走を簡単かつ低コストにて検出することができるようにする。

【解決手段】個別のプログラムを実行する複数の基板1,2を有するシステムにおいて、複数の基板1,2はそれぞれ基板制御手段11,12を備え、一方の基板2におけるプログラムの暴走を監視する基板監視手段を他方の基板制御手段11に設け、一方の基板2は、暴走を検出するプログラムよりも処理の優先度が低い周期起動タスクを周期的に起動させて、起動する毎に所定の情報変化が他方の基板1に伝達し、前記基板監視手段は、一定時間の間に一方の基板2から前記所定の情報変化が伝達されたか否かを監視し、前記一定時間の間に前記所定の情報変化が伝達されなかった場合を、一方の基板2のプログラムの暴走として検出する。

(もっと読む)

CPU監視装置及び電子制御装置

【課題】三つ以上のCPUを備えるマイクロコンピュータシステムであっても、監視回路の数を増やすことなく適切にCPUの暴走監視でき、さらには、監視回路を共用したときに何れのCPUに異常が発生しているのかを容易に判別することができるCPU監視装置を提供する。

【解決手段】CPU15から周期的に出力されるウォッチドッグタイマクリア信号の周期が監視周期を超えると前記CPU15にリセット信号を出力する監視部41を備えて構成されるCPU監視装置40であって、複数のCPU15が前記監視部41に対して設定周期内で前記ウォッチドッグタイマクリア信号を時分割して出力し、各ウォッチドッグタイマクリア信号を合成した一つのウォッチドッグタイマクリア信号が前記監視部41に入力されるように構成されている。

(もっと読む)

コンピュータの異常監視装置

【課題】OSやアプリケーションの異常動作を早期に検出でき、またシステムのCPU負担を下げながら、異常動作したアプリケーションを特定できる。

【解決手段】各アプリケーション1A〜1Cは、自アプリケーションを特定する情報と、アプリケーション別の監視タイムアウト時間を記載したアプリケーション情報を、ウオッチドッグ機能を有効にする要求として発行し、これをオペレーティングシステム2を通してFIFOメモリ4に順次記憶し、ローカルCPU5はアプリケーション情報を順次読み出し、アプリケーション別のタイムアウト時間についてウオッチドッグ監視を行う。

アプリケーション別の個々の動作確認により異常の有無を監視し、これら監視を監視エージェントとオペレーティングシステムを通したローカルCPUで行う。

(もっと読む)

異常検出方法及び処理装置

【課題】カーネルのロード前の段階においてもシステム起動時の異常を検出する。

【解決手段】オペレーションシステムの起動時における異常を検出するためのWDTが、ブートローダーの起動からカーネルがロードされるまでの間の該ブートローダーの実行段階において起動される。

(もっと読む)

タイマー回路及びそれを備えた信号処理回路

【課題】CPUの負担を軽減し、一定でない周期で割り込み信号を繰り返し発生させるタイマー回路を提供する。

【解決手段】計測すべき時間に応じたリロード値を設定し、その設定した前記リロード値に基づいてカウント動作を行うタイマー回路において、複数のリロード値を記憶するメモリと、前記複数のリロード値それぞれの前記メモリ上での格納先を示すリロード値アドレスを生成するリロード値アドレス生成回路と、前記リロード値アドレス生成回路において生成されたリロード値アドレスを参照して前記メモリから読み出された前記リロード値に基づいてカウント動作を行うカウンターと、前記リロード値アドレス生成回路における前記リロード値アドレスの更新、及び、前記メモリから前記カウンターへの前記リロード値の読み出しを制御するタイマー制御回路と、を有する。

(もっと読む)

マイクロプログラム暴走検出方法、暴走検出プログラム、及びマイクロプログラム暴走検出システム

【課題】ウォッチドッグタイマの機能をソフトウェアで拡張し暴走検出精度を上げることにより、システムの障害検出率を上げることができる方法を提供する。

【解決手段】マイクロプログラム暴走検出方法は、プログラムを実行する中央演算装置とタイマとを有するマイクロプログラム暴走検出システムにおいて、タイマを制御管理する第1のプログラムと第2のプログラムとを用意する。第2のプログラムが第1の設定時間として第1のプログラムへ通知するステップと、第1のプログラムが第1の設定時間をタイマに設定するステップと、第2のプログラムが第1の設定時間を通知してから当該第1の設定時間が経過する前に第2の設定時間を通知するステップと、第1のプログラムが第2の設定時間をタイマに設定するステップと、第1の設定時間と第2の設定時間との通知状況に基づいて、中央演算装置をリセットするステップとを中央演算装置に実行させる。

(もっと読む)

動作ログ管理システム及び動作ログ管理方法

【課題】この発明は、時刻合わせのための通信を定期的に行うことなく、メインシステムの動作ログ情報とサブシステムの動作ログ情報との時間的整合性をより高めることができる動作ログ管理システムを提供することを目的とするものである。

【解決手段】駅システムコントローラ3は、命令IDと基準時刻情報とメイン動作ログとを関連付けてメイン動作ログ情報を作成する。プラットホームドアコントローラ4は、命令IDと経過時間情報とサブ動作ログとを互いに関連付けてサブ動作ログ情報を作成する。動作ログ管理装置6は、同じ命令IDに関連付けられた基準時刻情報と経過時間情報とから、サブ動作ログ情報の作成時刻を求め、メイン動作ログ情報とサブ動作ログ情報とを作成時刻順に整列させ格納する。

(もっと読む)

ウォッチドッグタイマ

【課題】 汎用性を向上させるとともに、電子制御装置の動作状態を確実に監視することができるウォッチドッグタイマを提供する。

【解決手段】 電子制御装置2は、通常動作モードにおいてはキャンセルパルスを定期的に出力し、スタンバイモードにおいてはスタンバイ信号を出力する。ウォッチドッグタイマ3は、切換スイッチ4から第3入力端子INCを介して監視無効信号が入力され、且つ電子制御装置2からスタンバイ信号が出力されていることを条件として機能制限信号を出力する機能制御部6を備えている。また、ウォッチドッグタイマ3は、電子制御装置2からのキャンセルパルスに基づいて該電子制御装置2の動作状態を監視する一方、機能制御部6から機能制限信号が出力されている間においては、キャンセルパルスの入力有無にかかわらずリセット信号の出力を禁止する出力禁止処理を行う動作判断部5を備えている。

(もっと読む)

1 - 14 / 14

[ Back to top ]