Fターム[5B045EE11]の内容

Fターム[5B045EE11]の下位に属するFターム

優先順位によるもの (23)

先着順によるもの (14)

フラグ、識別子によるもの (17)

時間割当方式 (4)

領域を分割するもの (20)

待ち行列の管理 (7)

複合方式 (2)

占有の解除 (12)

Fターム[5B045EE11]に分類される特許

1 - 8 / 8

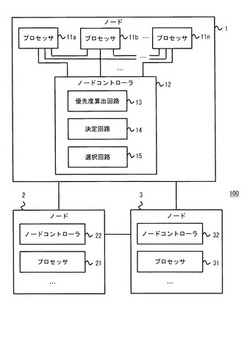

ノードコントローラ、リクエストの出力順序決定方法及びノード間通信システム

【課題】ノード間通信により他のノードへのアクセスする際の複数のリクエスト全体の処理性能を向上すること。

【解決手段】本発明にかかるノードコントローラは、複数のノードと接続され、自己のノード内の複数のプロセッサから複数のノードのいずれかに属するプロセッサへの複数のリクエストを受け付け、当該複数のリクエストのそれぞれについて、リクエストの要求先のノードに応じた優先度を算出する優先度算出回路と、算出された優先度に基づいて、受け付けた複数のリクエストのうち出力すべきリクエストを決定する決定回路と、決定されたリクエストを選択して要求先のノードへ出力する選択回路と、を備える。

(もっと読む)

データ転送システム、スイッチ及びデータ転送方法プロセッサ間ネットワーク

【課題】プロセッサ間で転送するパケットの転送時間の偏りを低減することができるデータ転送システム、スイッチ及びデータ転送方法を提供すること。

【解決手段】本発明にかかるデータ転送システムは、複数のプロセッサと、複数のプロセッサに含まれる一のプロセッサから他のプロセッサに対するデータ転送を複数の入力及び出力ポートを介して実行する複数のデータ転送部20を備える。データ転送部20は、次の転送先が同じ競合データについて調停を実行する調停手段259と、調停を行った競合データの競合数を示す強度情報を次の転送先に送信する強度情報通知手段260を有する。調停手段259は、調停を実行する場合には、複数の入力ポートの中でそれぞれの入力ポートを選択し、その入力ポートから競合データを入力する割合を示す選択割合を、各入力ポートから受信した強度情報が示す競合数の多さに関する入力ポート間の割合に応じて決定する。

(もっと読む)

共有キャッシュメモリ装置

【課題】2個のプロセッサに、より高速に連携した処理を行わせることが可能な共有キャッシュメモリ装置を提供する。

【解決手段】共有キャッシュメモリ装置を、第1プロセッサが生成して第2プロセッサが利用するデータを記憶するための幾つかの監視対象記憶領域をデータメモリ部33に確保する機能、管理対象記憶領域毎に第1プロセッサによるデータの書き込みが行われたか否かを管理する機能、データの書き込みが完了していない監視対象記憶領域上のデータを要求するリード要求を受信したときに、その監視対象記憶領域へのデータの書き込みが第1プロセッサにより行われるのを待機してから、当該リード要求に応答する機能を有する装置として構成しておく。

(もっと読む)

インターコネクト内のバリアトランザクション

データ処理装置のためのインターコネクト回路機構が開示される。このインターコネクト回路機構は、少なくとも1つのイニシエータデバイスが、少なくとも1つの受信デバイスにアクセスする際に経由することができる、データルートを提供するように構成され、このインターコネクト回路機構は、少なくとも1つのイニシエータデバイスからトランザクション要求を受信するための、少なくとも1つの入力と、少なくとも1つの受信デバイスにトランザクション要求を出力するための、少なくとも1つの出力と、少なくとも1つの入力と少なくとも1つの出力との間でトランザクション要求を送信するための、少なくとも1つの経路と、受信されたトランザクション要求を、少なくとも1つの入力から少なくとも1つの出力へルーティングするための制御回路機構とを含み、この制御回路機構が、バリアトランザクション要求に応答して、少なくとも1つの経路のうちの1つに沿って通過するトランザクション要求のストリーム内部のバリアトランザクション要求に対しての、少なくとも一部のトランザクション要求の順序付けを、トランザクション要求のストリーム内のバリアトランザクション要求の後に発生する少なくとも一部のトランザクション要求に対しての、トランザクション要求のストリーム内のバリアトランザクション要求の前に発生する少なくとも一部のトランザクション要求の順序変更を許可しないことによって、維持するように構成され、このバリアトランザクション要求は、トランザクション要求のストリーム内部のトランザクション要求のうちのいずれが、順序付けが維持されるべき少なくとも一部のトランザクション要求を含むかを指示する、指示子を含む。  (もっと読む)

(もっと読む)

分散システム内の種々のコンポーネントの活動を同期させること

インターコネクトを介して受信側デバイスにトランザクション要求を発行するイニシエータデバイスが開示される。イニシエータデバイスは、前記インターコネクトから要求を受信し、前記インターコネクトに要求を発行する少なくとも1つのポートと、バリアトランザクション要求を生成するバリア発生器とを備え、バリアトランザクション要求は、インターコネクトを通過するトランザクション要求のストリーム内の少なくともいくつかのトランザクション要求の順序付けが、バリアトランザクション要求に関してトランザクション要求のストリームにおいてバリアトランザクション要求の前に発生するトランザクション要求の少なくともいくつかの再順序付けを可能にしないことによって維持されるべきであることを、インターコネクトに示し、トランザクション要求の少なくとも部分集合の進捗を問い合わせる同期要求の受信に応答して、イニシエータデバイスは、トランザクション要求の少なくとも部分集合内の任意の保留中のトランザクション要求を実行し、バリア発生器においてバリアトランザクション要求を生成し、少なくとも1つのポートを介してインターコネクトにバリアトランザクション要求を発行し、バリアトランザクション要求に対する応答を受信することに応答して、同期要求に対する応答としてアクノリッジ信号を発行するように応答する。  (もっと読む)

(もっと読む)

マルチプロセッサシステム

【課題】マルチプロセッサシステムが同時に実行できるサービスの上限数の制限を緩和し、且つ、マルチプロセッサシステムの処理効率を向上させる。

【解決手段】ホストプロセッサ12と、ホストプロセッサ12のアクセラレータとして動作して、サービスを実行するコプロセッサ14と、ホストプロセッサ12とコプロセッサ14とを接続するバス16と、を備える。ホストプロセッサ12は、第1通信方式に基づいて、ユーザアプリケーション18aによって発行されたアプリケーションデータをコプロセッサ14にバス16を介して転送する第1通信管理部123と、第1通信方式よりもバストラフィックが少ない第2通信方式に基づいて、ユーザアプリケーション18aによって発行されたアプリケーションデータをコプロセッサ14にバス16を介して転送する第2通信管理部124と、第1及び第2通信管理部123,124を選択的に制御する制御部121と、を備える。

(もっと読む)

バス調停方式およびマルチCPU構成のプログラマブルコントローラ

【課題】マルチCPUシステムにおいて、各CPUが、共有メモリにアクセス中でも、それぞれの内部バスに接続されている各種メモリの使用を可能として、また、各CPU自体はバス調停を行う必要性をなくす。

【解決手段】本方式は、CPU21に内部バスB21を介してFPGA26を接続し、FPGA16,26それぞれを外部バスB13,B23を介してモジュールバス30に共通接続すると共に、FPGA26にメモリバスB22を介して共有メモリ27を接続し、FPGA26は、CPU21が共有メモリ27にアクセス中でメモリバスB22を占有中のときに、CPU11からアクセス要求があると、CPU21のアクセス優先、アクセス先着順、CPU11アクセス優先かの判断により、共有メモリ27にCPU11がアクセスするためのバス調停を行う。

(もっと読む)

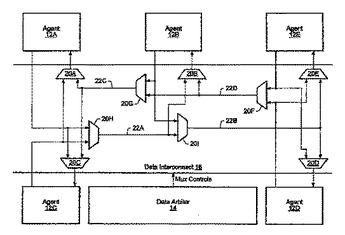

部分的にポピュレートされる階層型クロスバ

様々な実施形態で、装置は、複数のエージェントと相互接続を備える。一実施形態では、複数のエージェントは第1から第4までのエージェントを含む。相互接続は、エージェント間で通信パスを形成するように切換え可能な(例えば複数の選択回路を使用して)複数のセグメントを備え、第1セグメントは、第1エージェントから第2エージェントへの第1通信パスに含まれ、また第3エージェントから第4エージェントへの第2通信パスにも含まれる。別の実施形態では、各セグメントは選択回路によって駆動される。少なくとも1つの選択回路は、少なくとも1つのセグメントと、少なくとも1つのエージェントからの出力とを、入力として有する。さらに別の実施形態では、アービタが、セグメントを介した宛先エージェントへの通信パスを、各要求に対して相互接続上で決定するように構成される。アービタは、対応する通信パス中の各セグメントが利用可能であるような要求のサブセット間で、調停するように構成される。  (もっと読む)

(もっと読む)

1 - 8 / 8

[ Back to top ]