Fターム[5B047EA05]の内容

Fターム[5B047EA05]に分類される特許

1 - 20 / 243

演算方法、演算装置、画像処理装置およびプログラム

【課題】 遅延メモリの省容量化を実現しつつも、ある一定のメモリ帯域の中でさまざまな形態の画像処理を実現するため、データの解像度と参照枚数が変化しても柔軟に対処できる画像処理方法及びその装置を提供する。

【解決手段】 画像データの転送単位を設定し、該転送単位の画像データを処理するために必要な参照用データの転送単位を取得する。バッファの容量に収まるように、画像データの転送単位と参照用データの転送単位とから、画像データの転送量を取得する。画像データの転送量と画像データの転送単位とに基づいて、バンド領域の高さを取得する。

(もっと読む)

情報処理装置及び情報処理方法

【課題】シリアルバスを介してデータが転送される場合であっても、メモリを増加することなく、レイテンシの発生を防止することが可能な情報処理部100aを提供する。

【解決手段】前記CPU201からの要求が、前記第一のDMAコントローラ206に前記第二のRAM210のデータを読み取らせて前記第一のRAM209に書き込ませる間接リード要求であるか否かを判定する要求判定手段302と、前記要求が前記間接リード要求である場合に、当該間接リード要求を、前記第二のDMAコントローラ207に前記第二のRAM210のデータを前記第一のRAM209に書き込ませる直接ライト要求に変換する要求変換手段303と、前記直接ライト要求を前記第二のDMAコントローラ207に送信する要求送信手段304とを備える情報処理部100aを提供する。

(もっと読む)

情報絞り込み検出機能を備えたメモリ、その使用方法、このメモリを含む装置。

【課題】

パターン認識など情報検出の最大の課題は検索時間でありメモリの逐次比較処理が不要な非ノイマン型情報検出メモリを実現する。

【解決方法】

メモリアドレスごとに情報を記憶しその情報を読み出し可能なメモリで、このメモリは、外部から与えられる第1のデータは記憶されたメモリのデータを比較するためのデータ、第2のデータはアドレス同士を比較するためのデータ、の双方の入力データの入力手段と、この入力手段から与えられた上記双方の入力データにより記憶された情報のデータと、そのアドレスと、の双方を二重並列に合否判定し、その双方の合否判定結果をさらに並列に論理演算する手段と、上記論理演算に合格するこのメモリの上記アドレスを出力する手段と、を具備することを特徴とする情報絞り込み検出機能を備えたメモリであるのでインテリジェンスな情報検索はもとより人工知能等に広く利用可能である。

(もっと読む)

画像処理装置および画像処理プログラム

【課題】並列処理される画像処理の一部をハードウェア処理する複数のアクセラレータを用いて画像処理を行う際に、複数設けられたアクセラレータの利用効率を向上させる。

【解決手段】DMAバッファ50の実アドレスを連続した論理アドレス空間上の共通バッファ領域70にマッピングし、RIP処理部90は共通バッファ70にて空いたDMAバッファをDMA転送制御ライブラリ30に問い合わせて獲得し、任意のアクセラレータ80に処理を引き継ぐ中間データを書き込み続く処理をデバイス選択部20に要求する。デバイス選択部20は、RIP処理部90から通知される論理DMAバッファ33の共通バッファ領域70におけるオフセットを任意の空いているアクセラレータ80を制御するドライバ60に通知してアクセラレータ80に対する中間データのDMA転送および転送した中間データの処理を指示する。

(もっと読む)

画像回転装置及び画像形成装置

【課題】画像の回転に利用される記憶部の容量を小さく抑えることが可能な画像回転装置及び画像形成装置を提供する。

【解決手段】画像回転装置1は、画像データの書込み方向と画像データの読み出し方向が同一の方向であり、且つ、第1方向における所定のバースト長に対応する画素数と、第1方向に直交する第2方向の画素数とが同一である第1記憶部11と、第3方向の画素数が第1記憶部11における第1方向の画素数と同一であると共に、第3方向に直交する第4方向の画素数が第1記憶部11における第2方向の画素数よりも少ない第2記憶部12と、第1記憶部11に記憶される画像データを所定のバースト長に対応する画素数のデータ毎に読み出して第2記憶部12に書き込むことと、第2記憶部12に記憶されるデータを所定のバースト長に対応する画素数のデータ毎に読み出して第1記憶部11に書き込むことと、を行う読出書込部20と、を備える。

(もっと読む)

画像処理装置、画像処理システム、及びバンク管理方法

【課題】様々な動作周期及び動作開始タイミングに適切に対応できるようにバンク管理を行なう画像処理装置、画像処理システム、及びバンク管理方法を提供する。

【解決手段】画像処理装置は、3つのバンク領域を示す3つのアドレスを格納する第1乃至第3のアドレスレジスタと、フラグと、入力画像切り替わりのタイミングで第1のアドレスレジスタと第2のアドレスレジスタとの間で格納アドレスを入れ替えるとともにフラグをセットし、第1のアドレスレジスタの格納アドレスを入力画像書き込みアドレスとして供給する画像入力バンク管理部と、フラグがセット状態の場合、処理画像切り替わりのタイミングで第2のアドレスレジスタと第3のアドレスレジスタとの間で格納アドレスを入れ替えるとともにフラグをリセットし、第3のアドレスレジスタの格納アドレスを処理画像読み出しアドレスとして供給する画像処理バンク管理部とを含むことを特徴とする。

(もっと読む)

画像形成装置及び方法

【課題】スキューずれ角度がプリントヘッドの取り付け精度により一定の場合に、補正に必要となるラインバッファの容量を削減する。

【解決手段】スキューずれ角度に対応して主走査方向の画像データをスキュー補正対象のブロック数に分割するスキュー画像処理部5と、主走査方向にライン毎に入力される画像データを一時的に保存するラインバッファ2と、分割されたブロック数に基づいてラインバッファ2から出力データを読み出すアドレスを生成するラインバッファリードアドレス制御部3と、出力データを読み出したリードアドレスからその読み出したアドレスへ入力データを書き込むアドレスを生成するラインバッファライトアドレス制御部4とを備え、スキュー画像処理部5はラインバッファ2の一部を用いてスキューずれ角度に応じたアドレス領域内で制御し既に出力として読み出されたデータが格納されていたアドレスに画像データを書き込みスキュー補正を行う。

(もっと読む)

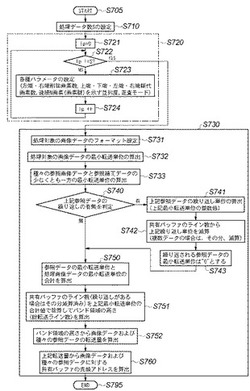

データ処理装置

【課題】分割ブロック毎の処理に必要なデータが、データ転送の切れ目をまたいでいる場合でも、バッファの記憶容量を増大させることなく、各ブロックの処理間のロス時間を低減することができるデータ処理装置を提供する。

【解決手段】予め定められたデータ取得単位毎にデータを取得するデータ取得部と、1つのデータ取得単位よりも少ない記憶容量の複数の分割バッファを具備し、合計の記憶容量が2つのデータ取得単位以上であるバッファ部と、データが有効であるか否かの有効データ情報を出力する有効データ領域判定部と、分割バッファにデータが格納されているか否かの管理情報を出力するバッファ状態管理部と、管理情報に基づいて、少なくとも有効データ情報に示された有効なデータを含む、分割バッファの記憶容量の単位のデータを分割バッファに書き込むデータ書き込み制御部と、管理情報に基づいて有効なデータを読み出すデータ読み出し制御部とを備える。

(もっと読む)

画像メモリ制御装置および画像処理装置

【課題】バースト転送が可能な画像メモリを用いた場合に、成分数の多いカラー画像データに対しても成分数の少ないモノクロ画像データに対しても画像回転処理などを内部メモリの増加を抑えて効率よく実行できる画像メモリ制御装置を提供する。

【解決手段】CMYKAの5成分のカラー画像を順次入力するときは、成分別に8ラインずつの入力バッファを5個形成して8ライン分の画像データを一時保存した後、入力バッファから同一領域に対応する各成分の画像データを8×8画素単位のブロックで読み出し、これらのブロックを同一行アドレス内の連続する列アドレスにバースト転送で格納する。K,Aの2成分のモノクロ画像データを入力するときは、前記入力バッファを2個ずつ組み合わせて16ラインの入力バッファを2個形成し、ブロックサイズを16×16画素に拡張して同様の処理を行う。

(もっと読む)

グラフィック演算処理チップ

【課題】 負荷が抑制された簡易なアルゴリズムによって記憶領域の断片化を抑制するができるグラフィック演算処理チップチップを提供することを目的とする。

【解決手段】 オンチップメモリ104は,互いに隣接し,それぞれが同じタイプのデータ種別を有するように区分された複数のサブ領域Sに分割されている。サブ領域S内における各データはそれぞれ連続する順列データとして記憶されるとともに,同順列データはそれぞれが他の順列データと隣接する態様にて記憶される。そして,各サブ領域Sに記録されるデータは,オンチップメモリ104に記録されている期間であるライフサイクル値がそれぞれ異なっており,ライフサイクル値が短いデータを含むサブ領域Sが,ライフサイクル値が長いデータを含むサブ領域Sと隣接して設けられている。

(もっと読む)

画像処理装置及び画像処理プログラム

【課題】不要なメモリを早急に解放することができる。

【解決手段】ワークフロー管理部46Aは、画像処理モジュール38から自モジュールの消去通知が出力された場合において、該画像処理モジュール38の前段のバッファモジュール40の消去が可能と判断したときに、消去要求を該バッファモジュール40の前段の画像処理モジュール38に入力する。バッファモジュール40は、自モジュールに連結された全画像処理モジュール38が消去されると自モジュールを消去し、画像処理モジュール38は、画像処理部を構築する画像処理モジュール38の全ての処理が終了した場合、自モジュールの全処理が終了した場合、並びに消去要求が入力された場合又は消去要求が入力され且つ自モジュールの消去が可能と判断した場合に、消去通知をワークフロー管理部46Aに出力し自モジュールを消去する。消去されたモジュールに割り当てられていたメモリは解放される。

(もっと読む)

画像処理装置及び画像形成装置

【課題】低消費電力化を図れる画像処理装置を提供する。

【解決手段】書込読出制御部53は第1及び第2のラインメモリ51a,51bの中から読み出し可能なラインメモリと書き込み可能なラインメモリとを交互に切り換える制御する。1ラインの画像データが上記ラインメモリに書き込まれる際に、白ライン判定部31はそのラインの画像データに対応する画像が白ラインか否か判定する。白ラインであれば、画像処理制御部23はそのラインの画像データをラインメモリから読み出す読出クロックCLK3及び画像処理部27で使用される動作クロックCLK4の生成を停止する。

(もっと読む)

メモリ制御方法、メモリ制御装置、および画像形成装置

【課題】シリアル−パラレル変換とパラレル−シリアル変換を効率的に実行する。

【解決手段】画像処理前のラインデータを記憶するラインメモリと画像処理後のラインデータを記憶するラインメモリとを同一素子で構成し、シリアルデータ形式で入力されるラインデータをラインメモリで記憶する処理前・メモリ入力タイミング,記憶された処理前のラインデータをパラレルデータ形式で読み出す処理前・メモリ出力タイミング,処理後のパラレルデータ形式のラインデータをラインメモリで記憶する処理後・メモリ入力タイミング,記憶された処理後のラインデータをシリアルデータ形式で読み出す処理後・メモリ出力タイミング,の4タイミングで制御し、同一ライン周期内に処理前・メモリ出力タイミングの直後に処理後・メモリ入力タイミングを実行すると共に、同一ライン周期内に処理後・メモリ出力タイミングの直後に処理前・メモリ入力タイミングを実行する。

(もっと読む)

画像処理装置及び方法

【課題】画像メモリに対して無駄なアクセスをできるだけ省略し、効率の良いアクセスを行うことができ、画像処理速度の向上を図る。

【解決手段】SIMDプロセッサを用いて画像データに対して走査ライン方向で画像回転処理を繰り返し行う画像処理装置において、画像データに対して所定の回転角度だけ回転させるときに、上記回転角度に基づいてSIMD単位の必要ライン数を算出して、当該SIMD単位の必要ライン数の画像データを外部メモリから内部メモリに転送して保持して、当該内部メモリに保持された画像データに対して画像回転処理を実行する。

(もっと読む)

パターン識別装置及びその制御方法、プログラム

【課題】 メモリ容量を増大させずに累積画像を高速に読み書き可能とするための技術を提供する。

【解決手段】 配列に格納された複数のデータ要素を含む入力情報の複数のデータ要素の各々について、データ要素の配列における位置に対応する累積情報値を計算し、計算した累積情報値の各々を、対応するデータ要素の配列における位置に基づいて、予め設けられた複数の記憶手段のいずれか1つに書き込み、複数の記憶手段からそれぞれ1つずつ累積情報値を並列に読み出し、複数の記憶手段から読み出した累積情報値を用いて、当該累積情報値に対応するデータ要素の配列における位置により決定される、入力情報の局所領域の特徴量を算出し、算出した特徴量と、予め設定された辞書データとを比較して、局所領域に所定のパターンが存在するか否かを判定する。

(もっと読む)

データ処理装置およびデータ処理方法

【課題】複数データの夫々に対し、2次元パラメータの夫々を配列規則を損なうことなく対応させながら、大掛かりなキャッシュメモリを用いることなく、高速処理することが可能なデータ処理方法を提供する。

【解決手段】外部メモリ406に格納された2次元テーブルに、前回読み出したM行のパラメータに連続するM行のパラメータが存在する場合は、このM行のパラメータを新たなパラメータとしてキャッシュメモリ404の内容を更新する。また、2次元テーブルに、前回読み出したM行のパラメータに連続するM行のパラメータが存在しない場合は、2次元テーブルの先頭の行に戻って連続するM行のパラメータを、新たなパラメータとしてキャッシュメモリ404の内容を更新する。このような更新の規則を、処理の単位であるバンドが切り替わる場合であっても、またバンド処理の途中であっても維持する。

(もっと読む)

画像処理装置、画像形成装置、画像処理方法、画像処理プログラム及び記録媒体

【課題】本発明は、原稿の両面の画像を同時に読み取るとともに、長尺原稿を自動判別してメモリ容量を削減しつつ原稿両面画像データと長尺原稿の片面画像データを切り替えてメモリに保存する。

【解決手段】画像形成装置1は、原稿の表面と裏面をスキャナ部2aとスキャナ部2bで約同時に読み取って、所定のサイズの原稿の表面画像データ1ページ分を記憶する表面メモリ領域と該原稿の裏面画像データ1ページ分を記憶する裏面メモリ領域を備えているメモリ4の該表面メモリ領域と該裏面メモリ領域に、メモリ制御部3によって順次書き込み、表面画像データの画像データが、該表面メモリ領域の上限のデータ量になると、メモリ制御部3が、原稿の裏面のメモリ4への書き込みを停止するとともに、表面画像データを、該表面メモリ領域と該裏面メモリ領域を1つに結合した結合メモリ領域に連続して書き込む。

(もっと読む)

画像処理装置、画像処理方法、プログラム、及び電子装置

【課題】第1の画像と第2の画像との対応が損なわれないようにする。

【解決手段】LED25−1は、第1の波長の光を被写体に照射し、LED25−2は、第2の波長の光を被写体に照射し、カメラ26は、第1の波長の光が被写体に照射されているときの反射光に基づいて第1の画像を生成するとともに、第2の波長の光が被写体に照射されているときの反射光に基づいて第2の画像を生成し、FIFOフレームバッファ41は、第1及び第2の画像を保持し、入力された入力順序で出力画像として出力し、輝度比較器42は、出力される出力画像の画素値と入力順序とに基づいて、出力される出力画像を第1又は第2の画像のいずれかに特定する。そして、演算部46は、第1及び第2の画像に特定された出力画像に基づいて、肌領域を検出する。本発明は、例えば、撮像した画像から、肌領域を検出するコンピュータ等に適用できる。

(もっと読む)

画像処理装置およびプログラム

【課題】2種類の画像データを順次合成する際に、これらを格納する画像メモリのアドレス管理が簡易な画像処理装置およびプログラムを提供する。

【解決手段】画像処理装置は、画像メモリ3に設定したフォームデータ用リングバッファ31と可変データ用リングバッファ32に、PCから取得したフォームデータと可変データをそれぞれページ順に記憶させるとともに、合成処理部4によって、フォームデータ用リングバッファ31と可変データ用リングバッファ32からフォームデータと可変データを同期して読出して合成する。

(もっと読む)

多次元データをデータ競合なしで同時検索するための処理システム、データ構造およびデータ処理方法

【課題】多次元データをデータ競合なしで同時検索する。

【解決手段】1個のデータポートを有する単一の方形データアレイは、多次元ピクセルアレイを表すデータ要素セットを記憶できる。ロード/記憶ユニットはデータ要素セットを受取り、各別のアドレスポートを有する複数の個別アドレス指定可能データアレイの間で分割記憶できる。個別アドレス指定可能データアレイは、ピクセルアレイの多次元サブアレイを表すデータ要素サブセットからのデータ要素を記憶する単一行を含んでよい。1回の計算サイクルでデータ要素の完全なサブセットを検索するプロセッサは、個別アドレス指定可能データアレイのそれぞれに対応するそれぞれのアドレスポートにアクセスすることで、複数のアドレス指定可能データアレイそれぞれの単一行に同時アクセスできる。実行ユニットは、データ要素サブセットで命令実行できる。

(もっと読む)

1 - 20 / 243

[ Back to top ]