Fターム[5B047EB05]の内容

Fターム[5B047EB05]に分類される特許

1 - 20 / 70

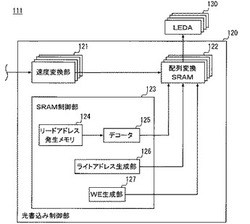

光書込み装置、画像形成装置及び光書込み装置の制御方法

【課題】アドレス変換テーブルを設けることにより異なる種類のLEDAに対応可能な光書込み装置の装置構成を効率化する。

【解決手段】形成すべき画像を構成する画素の情報である画素情報を取得する速度変換部121と、画素情報の配列を変換する配列変換SRAM122と、感光体を露光する光源に応じた画素情報の配列の変換態様を示すアドレス変換テーブルを取得して記憶するリードアドレス発生メモリ124と、画素情報の配列の変換を制御するためのライトアドレス信号を生成して出力するデコータ125とを含み、前記リードアドレス発生メモリ124は、同時にアクセス可能な複数の記憶領域に分割されており、アドレス変換テーブルを複数の記憶領域に分割して記憶する。

(もっと読む)

情報絞り込み検出機能を備えたメモリ、その使用方法、このメモリを含む装置。

【課題】

パターン認識など情報検出の最大の課題は検索時間でありメモリの逐次比較処理が不要な非ノイマン型情報検出メモリを実現する。

【解決方法】

メモリアドレスごとに情報を記憶しその情報を読み出し可能なメモリで、このメモリは、外部から与えられる第1のデータは記憶されたメモリのデータを比較するためのデータ、第2のデータはアドレス同士を比較するためのデータ、の双方の入力データの入力手段と、この入力手段から与えられた上記双方の入力データにより記憶された情報のデータと、そのアドレスと、の双方を二重並列に合否判定し、その双方の合否判定結果をさらに並列に論理演算する手段と、上記論理演算に合格するこのメモリの上記アドレスを出力する手段と、を具備することを特徴とする情報絞り込み検出機能を備えたメモリであるのでインテリジェンスな情報検索はもとより人工知能等に広く利用可能である。

(もっと読む)

画像処理装置、画像処理システム及び画像処理方法

【課題】シングルポートのSRAMを用いて画像処理装置の処理効率を改善する。

【解決手段】画像処理装置10は、複数の変換前画素値を記憶するメインメモリ30と、複数のキャッシュブロックを有するキャッシュメモリ20とに接続される。カウンタと、座標決定部と、メモリコントローラと、キャッシュアクセス部と、画素値計算部と、出力部とを備える。メモリコントローラは、メインメモリ30に記憶された複数の変換前画素値をそれぞれ、変換前座標に応じたキャッシュブロックへ転送する。キャッシュアクセス部は、複数のキャッシュブロックから、変換後画素値の計算に必要な全ての変換前画素値を1回のキャッシュアクセスで読み出す。画素値計算部は、キャッシュアクセス部が読み出した変換前画素値を参照して、変換後画素値を計算する。出力部は、変換後画素値を出力する。

(もっと読む)

データ処理装置およびデータ処理方法

【課題】データの転送効率を維持した状態で、データ転送に係る消費電力を低減することができるデータ処理装置およびデータ処理方法を提供する。

【解決手段】入力データを第1および第2の分離データに分離する第1のビット分離部と、n(nは1以上の自然数)回目とn+1回目の第1の分離データとを比較するビット比較部と、比較結果に基づいて第1の分離データを反転するか否かを判定した反転情報を出力するビット判定部と、反転情報に基づいて選択したデータを出力する第1のビット反転部と、選択したデータと第2の分離データとを配置し、反転情報を結合して出力する第1のビット結合部と、を具備し、順次入力された複数の入力データを転送データに変換して順次転送する際に、1つの転送データを1つの転送単位とし、予め定められた数の転送単位を1つの変換単位として、入力データを変換単位毎に配置するデータ変換部、を備える。

(もっと読む)

データ処理装置およびデータ処理方法

【課題】データの転送効率を維持した状態で、データ転送に係る消費電力を低減することができるデータ処理装置およびデータ処理方法を提供する。

【解決手段】入力データを予め定められたそれぞれの配置方法に基づいて配置した第1の変換データを生成する複数のデータ生成部と、対応するデータ生成部が出力したn(nは1以上の自然数)回目とn+1回目の第1の変換データ内の各ビットの値を比較し、該比較した結果に基づいたビットの数をビット変化数として算出する複数のビット変化数算出部と、それぞれのビット変化数の値を比較してデータ生成部を選択し、選択情報を出力するビット変化数比較部と、選択情報に基づいて選択した、いずれか1つの第1の変換データを選択データとして出力する第1のデータ選択部と、選択データを転送データとして出力する際に、予め定められた未使用ビットの位置に選択情報を結合して出力するビット結合部と、を具備する。

(もっと読む)

データ処理装置およびデータ処理方法

【課題】データの転送効率を維持した状態で、データ転送に係る消費電力を低減することができるデータ処理装置およびデータ処理方法を提供する。

【解決手段】入力データを順次データバスに配置した第1の転送データを生成するデータ生成部と、データバスのビット幅を、予め定められたビット数の複数の単位ビットに分割し、第1の転送データ内に配置されたデータの配置を、単位ビット毎に並べ替えた変更データを生成し、該生成した変更データと、並べ替えられたデータの配置を表す並べ替え情報とを、転送データとして出力する第1のデータ配置変更部と、を具備し、順次入力された複数の入力データを、予め定められたビット数のデータバスと同じビット数の転送データに変換して順次転送する際に、1つの転送データを1つの転送単位とし、予め定められた数の転送単位を1つの変換単位として、入力データを変換単位毎に配置するデータ変換部、を備える。

(もっと読む)

画像変形装置および命令付加装置

【課題】キャッシュミスのないアクセスを可能にする。

【解決手段】画像変形装置10は、画像を格納するフレームメモリ12と、フレームメモリ12に格納された画像に施す変形処理パラメータP1にプリフェッチ命令P2が付加されたプリフェッチ命令付変形処理パラメータP3を格納するパラメータメモリ13と、フレームメモリ12に格納された画像の画素データの一部を一時的に格納することで、フレームメモリ12からの画素データ読み込み効率を向上させるキャッシュメモリ14と、パラメータメモリ13に格納されたプリフェッチ命令P2に従ってフレームメモリ12からキャッシュメモリ14に画素データをロードするプリフェッチ制御部15と、パラメータメモリ13に格納された変形処理パラメータP1を使用してキャッシュメモリ14に格納された画像に変形処理を施す変形処理部16とを備える。

(もっと読む)

画像形成アレイ用ホストインタフェース

【課題】システムプロセッサがアクセスする画像形成データを直接的に受信することのできる画像形成アレイと共に累積可能なインタフェースを提供する。

【解決手段】画像形成アレイ12を有する画像センサとクロックジェネレータ1Aとからデータを受信し、このデータをプロセッサシステム10へ転送するインタフェース13は、画像形成アレイデータを、該クロック信号により決定された速度で記憶するメモリを備える。このメモリにおけるデータの量に応じて、信号ジェネレータが前記プロセッサシステム10へ伝送するための信号を生成し、また、回路が前記プロセッサシステム10により決定された速度で、前記メモリからのデータの転送を制御する。前記メモリは、先入れ先出し(FIFO)バッファ、または、アドレス可能メモリであり、このインタフェース13は、前記画像センサと同一のダイ上に集積される。

(もっと読む)

画像処理装置及び制御プログラム

【課題】画像の回転処理時に、キャッシュメモリのスペックに応じた矩形領域を設定することで、高速な回転処理を実施可能にする。

【解決手段】CPU20は、キャッシュメモリ22のデータ書き込み可能な領域の記憶容量に応じて得られる入力用メモリ空間11a上で特定される矩形形状の領域の大きさを、入力用メモリ空間11a上に記憶された画像を該領域を単位として分割したときにその分割された各領域の画像を構成するデータの幅が同等になるように調整し、入力用メモリ空間11aに記憶された画像を調整した矩形形状の領域を単位として分割しながら、分割した領域単位でデータを順次キャッシュメモリ22に書き込み、キャッシュメモリ22に書き込んだデータを、分割した領域単位で該キャッシュメモリ22から読み出し、出力用メモリ空間11bの予め設定した領域に書き込むことで回転した画像を生成する。

(もっと読む)

画像書込み装置および画像形成装置

【課題】注目画素を取巻く主・副走査の画素を格納機能から同時に取出して、注目画素に対してデータ識別できることにより、1画素単位での線画を忠実に認識するデジタル発光素子書込み装置を提供する。

【解決手段】注目ラインの副走査3ライン目の画素を順にマトリクス判断していく。主走査5の画素101では、マトリクスより縦線と判断できる。ここで2値データから4値のコード化に変換する場合、偶数画素か奇数画素かも判断し、縦パターンの奇数と判断すると画素101は、01bコードとなる。さらに画素102では、横線の奇数と判断し、11bコードとなり、画素103は、0データの奇数で00bコード、画素104では、1dot孤立点の偶数と判断し、10bコード、画素105では、斜め線の偶数と判断し11bコードとなる。注目画素を取巻く主・副の画素を格納機能から同時に取出すことで、1画素単位で忠実に線画を表現する。

(もっと読む)

パターン識別装置及びその制御方法、プログラム

【課題】 メモリ容量を増大させずに累積画像を高速に読み書き可能とするための技術を提供する。

【解決手段】 配列に格納された複数のデータ要素を含む入力情報の複数のデータ要素の各々について、データ要素の配列における位置に対応する累積情報値を計算し、計算した累積情報値の各々を、対応するデータ要素の配列における位置に基づいて、予め設けられた複数の記憶手段のいずれか1つに書き込み、複数の記憶手段からそれぞれ1つずつ累積情報値を並列に読み出し、複数の記憶手段から読み出した累積情報値を用いて、当該累積情報値に対応するデータ要素の配列における位置により決定される、入力情報の局所領域の特徴量を算出し、算出した特徴量と、予め設定された辞書データとを比較して、局所領域に所定のパターンが存在するか否かを判定する。

(もっと読む)

データ処理装置およびデータ処理方法

【課題】複数データの夫々に対し、2次元パラメータの夫々を配列規則を損なうことなく対応させながら、大掛かりなキャッシュメモリを用いることなく、高速処理することが可能なデータ処理方法を提供する。

【解決手段】外部メモリ406に格納された2次元テーブルに、前回読み出したM行のパラメータに連続するM行のパラメータが存在する場合は、このM行のパラメータを新たなパラメータとしてキャッシュメモリ404の内容を更新する。また、2次元テーブルに、前回読み出したM行のパラメータに連続するM行のパラメータが存在しない場合は、2次元テーブルの先頭の行に戻って連続するM行のパラメータを、新たなパラメータとしてキャッシュメモリ404の内容を更新する。このような更新の規則を、処理の単位であるバンドが切り替わる場合であっても、またバンド処理の途中であっても維持する。

(もっと読む)

多次元データをデータ競合なしで同時検索するための処理システム、データ構造およびデータ処理方法

【課題】多次元データをデータ競合なしで同時検索する。

【解決手段】1個のデータポートを有する単一の方形データアレイは、多次元ピクセルアレイを表すデータ要素セットを記憶できる。ロード/記憶ユニットはデータ要素セットを受取り、各別のアドレスポートを有する複数の個別アドレス指定可能データアレイの間で分割記憶できる。個別アドレス指定可能データアレイは、ピクセルアレイの多次元サブアレイを表すデータ要素サブセットからのデータ要素を記憶する単一行を含んでよい。1回の計算サイクルでデータ要素の完全なサブセットを検索するプロセッサは、個別アドレス指定可能データアレイのそれぞれに対応するそれぞれのアドレスポートにアクセスすることで、複数のアドレス指定可能データアレイそれぞれの単一行に同時アクセスできる。実行ユニットは、データ要素サブセットで命令実行できる。

(もっと読む)

画像処理装置及び画像撮像装置

【課題】安価なメモリ(フレームメモリ)でも原画像の自由な変形や歪補正等を行い、高画質な映像を容易に得られる画像処理装置を提供する。

【解決手段】メモリ220から画像データを読み出す際に座標変換により、画像の変形を反映した読出しアドレスを計算する手段230、入力された画像データをメモリ220に書込み、読出しアドレスに基づいてメモリ220から画像データを読み出す手段210、メモリ220から読み出される画像データの主走査方向の画素数を、出力画面の主走査方向の画素数に対して小さくなるように制限する手段212、出力画面の主走査方向の画素数に対して主走査方向の画素数が小さくメモリ220から読み出された画像データを、出力画面の主走査方向の画素数となるように伸張する手段240を備える。

(もっと読む)

画像処理装置、画像処理方法および画像処理プログラム

【課題】処理時間を短縮すること。

【解決手段】画像処理装置1は画素割り当て部2と書き込み部3を有している。画素割り当て部2は、変換対象画像4の一方向の4画素により形成される1×4画素領域の各画素を、変換対象画像4の任意の2×2画素領域の各画素がいずれも異なる記憶部に記憶されるように、記憶部a1、b1、c1、d1にそれぞれ割り当てる。書き込み部3は、記憶部a1、b1、c1、d1のうち、画素割り当て部2によって割り当てられた記憶部に画素の画素値を書き込む。

(もっと読む)

画像処理方法、画像処理装置およびプログラム

【課題】 遅延メモリの省容量化を実現しつつも、ある一定のメモリ帯域の中でさまざまな形態の画像処理を実現するため、データの解像度と参照枚数が変化しても柔軟に対処できる画像処理方法及びその装置を提供する。

【解決手段】 参照用画像データと補正データの少なくとも一方を参照して画像データを処理するときに、処理対象の画像データを複数バンド領域に分割し、分割したバンド領域毎に画像処理を行う場合、画像データの最小転送単位を設定し、その最小転送単位の画像データの処理のために必要な参照用画像データと補正データの少なくとも一方の最小転送単位を求め、画像処理に利用可能なバッファに収まるように前記画像データの転送量を定めて、この画像データの転送量と画像データ最小転送単位の比から、分割するバンド領域の高さを定める。

(もっと読む)

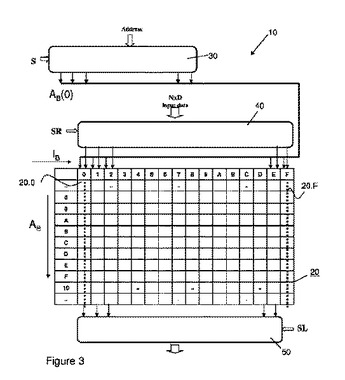

マルチモードアクセス可能な記憶装置

ブロックアクセスモードでのブロックアクセスおよび行アクセスモードでの行アクセスを可能にするマルチモードアクセス可能な記憶装置(10)を開示する。記憶装置は、各々がそれぞれのバンクインデックス(0、…、F)を有する複数のメモリバンク(20.0、…、20.F)を備えるメモリユニット(20)と、前記メモリバンクの各々について入力アドレスおよびシフトパラメータの関数として回転されたバンクアドレスを生成するアドレス発生器(30)と、入力ベクトルを回転させ、回転された入力ベクトルのベクトル要素をメモリユニットのそれぞれのバンクに供給する入力ベクトルデータ回転器(40)と、メモリユニットのそれぞれのバンクから取得されるベクトル要素を含むベクトルを逆回転させ、回転した出力ベクトルを供給する出力ベクトル回転器(50)と、を備える。  (もっと読む)

(もっと読む)

画像処理装置、プログラム

【課題】画像処理装置において、データ順序を変換させる場合に、特別な専用回路を設けることなく、できる限り処理速度の低下を防ぐ。

【解決手段】画像処理部10は、外部メモリー30と、プロセッサー部20とを備える。プロセッサー部20では、第1の処理部210および第2の処理部230が実現される。第1の処理部210は、外部メモリー30から第1の順序で画像データを読み出して処理し、第1の処理済データを内蔵メモリー22に書き込む。第2の処理部230は、内蔵メモリー22から第1の処理済データを読み出して処理し、第2の処理済データを第2の順序で外部メモリー30に書き込む。第1の順序から第2の順序への変更は、第2の処理部230が、第1の処理済データを第2の順序となるように内蔵メモリー22から読み出すことにより実行される。

(もっと読む)

画像処理回路、および印刷装置

【課題】回路サイズを抑制しつつ参照値を展開する記憶部の記憶容量を増加させることが可能な画像処理回路を提供する。

【解決手段】入力データに対して参照値を参照しつつ所定の処理を施す複数の処理部と、

参照値を記憶する記憶部と、を有し、記憶部は、直列に接続された複数の記憶素子により構成され、所定数の記憶素子毎に各処理部と接続し、同記憶素子に記憶された参照値を接続された各処理部に出力するシフトレジスタと、予め指定されたアドレスを受け付け、シフトレジスタに記憶された前記参照値を更新させるアクセス受信部と、を有する。

(もっと読む)

画像処理装置

【課題】回路の大規模化を防止又は抑制しつつ、不連続なアドレスに記憶された画像を短時間で読み出すことができる画像処理装置を提供する。

【解決手段】CPUは、不連続な記憶領域に格納された画像に対し、DMAコントローラにより画像処理を実施する場合のメモリからの読出し順を設定し、ディスクリプタ情報生成部は、この読み出し順において当該記憶領域に続く次の記憶領域についてのディスクリプタ情報が格納されているアドレスを示すディスクリプタアドレス情報と当該記憶領域のアドレス情報とを含むディスクリプタ情報を生成し、テーブル作成部は、ディスクリプタアドレス情報を用い、前記ブロック毎で且つバンド毎に、当該バンドに属する画像を記憶した記憶領域のうち、主走査方向において最も先頭側の画像を記憶した記憶領域と該領域のアドレス情報及びディスクリプタアドレス情報との対応関係を示すテーブルを作成する。

(もっと読む)

1 - 20 / 70

[ Back to top ]