Fターム[5B048DD10]の内容

デジタル計算機の試験診断 (4,118) | 試験手段 (1,073) | 内蔵試験回路 (80)

Fターム[5B048DD10]に分類される特許

1 - 20 / 80

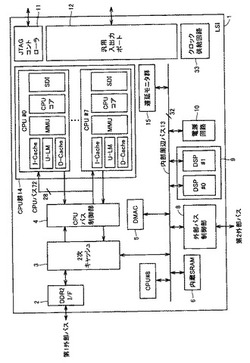

半導体装置

【課題】部分的な経年劣化の予兆を早期に発見することができる半導体装置を提供する。

【解決手段】LSI1は、複数のモジュールと、複数の遅延モニタを含む遅延モニタ群15とを備える。各遅延モニタは、複数段のゲート素子を有するリングオシレータを含む。各遅延モニタは、ゲート素子の遅延時間を測定する。CPU#0は、遅延モニタによって測定された遅延時間に基づいて、遅延モニタの近傍のモジュールの経年劣化を判定する。

(もっと読む)

演算装置及びエラー検出方法

【課題】エラーの検出効果を高くする。

【解決手段】演算装置1は、命令制御部100と、第1オペランド制御部200と、第2オペランド制御部300と、演算部400と、NOP検出部500と、エラー検出部600と、を備える。NOP検出部500が出力する制御信号に従って、命令制御部100、第1オペランド制御部200及び第2オペランド制御部300は、直前のクロックサイクルで受信した入力信号を試験信号として演算部400に出力する。エラー検出部600は、演算部400が求めた演算結果データと試験演算結果データとを比較し、エラーが発生しているか否かを判別する。

(もっと読む)

車両制御装置

【課題】外部起動信号がオフ状態になったときに演算装置がオフになることを確認する診断を、通常動作中に実施することのできる車両制御装置を得る。

【解決手段】本発明に係る車両制御装置は、外部起動信号がオフ状態になったときにメインリレー駆動回路がメインリレーをオフ状態にすることを確認するための診断処理を、外部起動信号がオン状態のときに実行する。

(もっと読む)

測定結果管理システム、管理サーバ、及び半導体集積回路装置

【課題】実際に稼動している半導体集積回路装置の実動作に影響を与える要因を解析し、更にその要因を低減することが可能な半導体集積回路装置を提供する。

【解決手段】測定対象である半導体集積回路131と、この半導体集積回路のジッタ又はノイズジッタ、ノイズ等の実動作に影響を与える物理量を測定する測定回路(半導体集積回路装置)130とを同一チップ上に構成する。測定回路の測定結果を解析し、測定対象の半導体集積回路を調整する回路にフィードバックさせる。

(もっと読む)

試験アクセス・ポート・スイッチ

【課題】選択されていないTAPの電源がオンまたはオフされているかに関わらず、選択されたTAPへ情報を転送することができる電子システムを提供する。

【解決手段】電子システム10は、それぞれTAPスイッチ12に接続されたTAP20,22,24を有している。TAPスイッチ12は、例えば、命令に追加または事前追加されたコードのように、シリアル命令に含まれる選択コードに応答して、TAPのうちの選択された1つへクロック信号を提供するように構成された第1の回路40を備える。このTAPスイッチは更に、TAPスイッチによって受け取られたシリアル命令を、選択されたTAPへ渡すように構成された命令レジスタ(IR)を備える第2の回路38と、選択コードに応答して、選択されたTAPから受け取ったシリアル命令を、TAPスイッチの出力へと転送するように構成された第3の回路42とを備える。

(もっと読む)

信頼性のあるマイクロコントローラ並びにその設計方法及びそのためのコンピュータプログラム

【課題】コンピュータ資源及び回路サイズを最適化し、完全な信頼性を実現する。

【解決手段】中央演算処理装置(50、51)と該中央演算処理装置(50、51)の動作のバリデーションの実行に適した欠陥処理装置(11)を含む信頼性のあるマイクロコントローラであって、欠陥処理装置(11)は、中央演算処理装置(51)に関して異なり、外部にあり、さらに、欠陥処理装置(11)は、少なくとも中央演算処理装置の動作のバリデーションを実行するモジュール、及び、マイクロコントローラ(10)の他の機能部分の動作のバリデーションを実行するように構成された1つ以上のモジュールを含んでいる。

(もっと読む)

演算制御装置、演算制御装置制御方法およびその制御用プログラム

【課題】複数のレジスタの値が一致したか否かをCPUのレジスタリード時に確認する。

【解決手段】レジスタ21乃至2nに保持された各テストデータが全て一致しているか否か比較判定部40で比較し比較結果を全比較結果Iとして出力すると共に、データ選択部30によって選択されたレジスタ21乃至2nのいずれか一つのレジスタの値とレジスタ21乃至2nの各値とがそれぞれ一致するか否か比較判定部40で比較し比較結果を個別比較結果J乃至Mとして出力し、選択されたリードデータと全比較結果Iとをビット連結部50で連結しリードデータ+全比較結果Fとして出力する。

(もっと読む)

回路試験装置

【課題】簡易な構成で論理回路を用いたシステムを停止させることなく論理回路の試験を行なう回路試験装置を得ること。

【解決手段】システムの動作の一部を実行する試験対象部と同じ機能を有した論理回路をFPGAを用いて再構成する試験対象機能代替部11を備え、試験対象入力選択部15は、試験対象部10の試験が行なわれる際には試験データ準備部16からの試験情報を選択して試験対象部10に出力し、且つ試験対象部がシステムの動作の一部を実行する際にはシステム前段P1からの入力情報を選択して試験対象部10に出力し、有効回路選択部14は、試験対象部の試験が行なわれる際には再構成後の試験対象機能代替部11による処理結果を選択してシステム後段Q1側へ出力し、且つ試験対象部10がシステムの動作の一部を実行する際には試験対象部10による処理結果を選択してシステム後段Q1側へ出力する。

(もっと読む)

データ転送システム,切替装置,診断方法及び診断プログラム

【課題】障害発生時の被疑箇所を容易に特定できるようにする。

【解決手段】情報処理装置20に対して、診断信号を送信させる診断信号送信制御部101と、切替装置10における診断信号の伝送経路上の複数の所定位置のそれぞれにおいて、診断信号を折り返して送信する複数の折り返し手段RE,ROと、各折り返し手段RE,ROに対して、診断信号を折り返させ折り返し信号として情報処理装置20に送出させる折り返し制御部103と、この折り返し制御部103によって送出させた折り返し信号に基づく診断結果に基づき、被疑箇所の特定を行なう特定部104とをそなえる。

(もっと読む)

自己診断システム及び検査回路判定方法

【課題】テスト対象回路の診断を実行する検査回路の正常性を判定することができる自己診断システム及び検査回路判定方法を提供すること

【解決手段】本発明にかかる自己診断システムは、テスト対象回路10におけるテストパタンの実行結果を用いて、テスト対象回路10の正常性を判定する診断コントローラ31及び32を有する検査回路30と、診断コントローラ31から出力されるテスト対象回路10の正常性判定結果と、診断コントローラ32から出力されるテスト対象回路10の正常性判定結果とを比較して、検査回路30の正常性を判定する検査回路判定部20と、を備えるものである。

(もっと読む)

集積回路装置及び集積回路装置の検査方法

【課題】集積回路装置の検査において、集積回路装置内部のレジスターの値読出しに掛かる時間を短くする。

【解決手段】集積回路装置が動作モード設定端子と読出しフラグを備えた第1のレジスターとを含み、前記読出しフラグは前記第1のレジスターに保存された値の読出しを許可するためのフラグであり、前記動作モード設定端子により第1の動作モードに設定されかつ前記読出しフラグが読出し許可に設定されているときは、外部からの読出し要求信号に対応して前記第1のレジスターの値が外部に出力されることを特徴とする。

(もっと読む)

解析システム及び半導体装置

【課題】LSI等の半導体装置内部の信号の遷移を容易に確認することが可能な解析システム及び半導体装置を提供すること。

【解決手段】半導体装置の内部において、解析対象となる内部信号が入力され、内部信号の遷移を検出すると所定のコードに変換して出力するとともに、内部信号の遷移を報知する報知信号を出力する符号化回路と、半導体装置の内部において、符号化回路から出力されるコードを格納する内部メモリと、半導体装置の外部において、符号化回路から出力される報知信号が入力され、内部信号の遷移タイミングを計時する計時回路と、半導体装置の外部において、計時回路で計時された時間情報を格納する外部メモリと、を備える。

(もっと読む)

電子回路装置および電子回路装置の動作検証支援方法

【課題】設計者が容易に動作検証をすることを可能にする。

【解決手段】電子回路装置100の検証支援処理回路22は、電子回路検証装置200から送信される検証指示情報に基づいて、機能ブロック回路1の検証を制御する検証制御情報を生成し、機能ブロック回路1へ送信する。機能ブロック回路1は、その検証制御情報を受信すると、遷移停止制御回路40、状態コード注入回路50およびエラー状態注入回路80を介して、その検証制御情報で指定される任意の状態コードおよびエラー状態を機能ブロック回路1の状態コードレジスタおよびエラー状態レジスタに注入した上で、機能ブロック回路1の動作を開始または停止させる。状態履歴記憶回路60には、そのときの状態コードおよび過去の最新の所定動作サイクル数の状態コードの履歴が記憶されている。検証支援処理回路22は、その状態コードの履歴を取得して、電子回路検証装置200へ送信する。

(もっと読む)

半導体集積回路、デバッグシステム、デバッグ方法、デバッグプログラム及び記録媒体

【課題】本発明は、デバッグを高精度に、かつ、効率的に行う半導体集積回路、デバッグシステム、デバッグ方法、デバッグプログラム及び記録媒体に関する。

【解決手段】MFPコントローラボード1の画像処理ASIC13は、I/F21から入力される画像データに対して、複数のアルゴ処理部22a〜22nが適宜の順序で所定の画像処理を施してI/F23から外部に出力するが、デバッグ時に、スキャナエミュレータ110から入力されて、I/F21及びアルゴ処理部22a〜22nから出力される画像データのハッシュ値をハッシュ計算部24a〜24n+1で生成して、それぞれ結果保存レジスタ25a〜25n+1に保持する。この結果保存レジスタ25a〜25n+1のハッシュ値をデバッガ端末100が取り出すことでデバッグすることができる。

(もっと読む)

マクロ検証方法

【課題】 システムLSIにおけるマスタブロックおよびスレーブブロックのマクロについてバス接続状態での動作上の不具合の早期検出を可能にする。

【解決手段】 複数の機能ブロックがバスを介して接続されるシステムLSIのマスタブロックおよびスレーブブロックのマクロに、マクロを制御するマクロ制御動作およびマクロの動作の正常/異常を判定するマクロ検証動作を実施するテスト回路を組み込み、テスト回路が組み込まれたマクロをバスに接続した検証環境を構築して、マスタブロックおよびスレーブブロックのマクロについてバス接続検証および機能検証を実施する。

(もっと読む)

半導体集積回路

【課題】 機能ブロックの出力を受けて動作する回路のテストを簡易なテストパターンを用いて実施し、テストコストを削減する。

【解決手段】 データ入力部は、外部データ入力端子に供給される入力データ信号を受ける。記憶部は、データ入力部で受けた入力データ信号を保持する。タイミング生成部は、出力要求信号に応答してタイミング信号を生成する。データ出力部は、記憶部に保持された入力データ信号をタイミング信号に同期して出力データ信号として出力する。テスト出力制御部は、データ入力部で受けた入力データ信号をタイミング信号に同期して出力する。データセレクタは、通常動作モード中に、データ出力部からの出力データ信号を外部データ出力端子に出力し、テストモード中に、テスト出力制御部からの入力データ信号を外部データ出力端子に出力する。

(もっと読む)

半導体集積回路およびその設計方法

【課題】ファンクション動作速度に影響を与えず、また回路面積増を抑えつつ、スキャンテストおよびロジックBIST動作中の消費電力を低減することができる半導体集積回路およびその設計方法を提供する。

【解決手段】スキャンテストのシフト動作時において消費電力に与える影響の大きいフリップフロップとして選択されたスキャンフリップフロップを、スキャンテストのシフト中に、組合せ回路101への出力値が固定されるように修正し、また、選択されるスキャンフリップフロップの数を、回路修正時に許容される面積の増分によって制限することで面積の増加を許容範囲に抑え、また、回路の動作速度を決定するフリップフロップ間経路の始点となるフリップフロップを選択しないことにより、回路のファンクション動作に影響を与えないようにする。

(もっと読む)

ディジタルシステムのパラメータ化け検出方法と該検出方法を備えたインバータ装置、並びに工作機械用及びロボット用御制装置

【課題】 制御基板における接続不良等のハードウェアの不具合によるパラメータ化けをも検出することができるディジタルシステムのパラメータ化け検出方法を提供する。

【解決手段】 RAM12に記憶されたパラメータ変更内容34と第1のEEPROM13に記憶されたパラメータ変更内容34をベリファイチェックし、RAM12と第1のEEPROM13の両記憶媒体に記憶されたパラメータ変更内容34に相違があればパラメータ化けが発生したとして検出し、相違がなければ、RAM12に記憶されたパラメータ変更内容34と第2のEEPROM22に記憶されたパラメータ変更内容34をベリファイチェックし、RAM12と第2のEEPROM22の両記憶媒体に記憶されたパラメータ変更内容34に相違があればパラメータ化けが発生したとして検出し、相違がなければパラメータ化けは発生していないと判断する。

(もっと読む)

半導体集積回路及びデバッグモード決定方法

【課題】本発明は、半導体集積回路及びデバッグモード決定方法に関し、パワーオンリセットが発生しない場合であっても、デバッグモードを適切に決定可能とすることを目的とする。

【解決手段】デバッグモードを指定するデバッグ信号を入力する端子と、電源投入時にリセット信号を生成するリセット回路と、デバッグ信号及びリセット信号に基づいてデバッグモードに移行させる制御信号を出力するデバッグモード制御回路とを有し、デバッグモード制御回路は、デバック信号をラッチして第1の信号を生成するラッチ回路と、許可コードが書き込まれると第2の信号を生成するレジスタ回路とを含み、第1の信号と第2の信号に基づいて前記制御信号を生成するように構成する。

(もっと読む)

外部インタフェースの機能性を検証するためのセルフテスト機構を備えた集積回路

本開示では、高周波外部インタフェースの機能性の検証のためのセルフテスト機構を備えた集積回路について説明する。外部インタフェースの実施例は、ペリフェラルコンポーネントインターコネクト(PCI)バス、アドバンスト高性能バス(AHB)、アドバンスト拡張インタフェース(AXI)バス、および高周波(例えば200MHz以上)で動作する他の外部インタフェースのような、メモリインターフェースおよびバスインタフェースを含んでいる。テストロジックは、集積回路上に組み込まれ、外部テスト機器から非テスト信号を受け取りながら外部インタフェースの機能性を検証するように構成されてもよい。故に、外部テスト機器が集積回路に高周波テスト信号を供給しない可能性がある。しかしながら、外部テスト機器は、集積回路のピンインタフェースの機能性を独自に検証することができる。その結果、集積回路は、外部インタフェースの機能性およびタイミングをベリファイするのに必要なコストと時間を削減することができる。  (もっと読む)

(もっと読む)

1 - 20 / 80

[ Back to top ]