Fターム[5B048DD18]の内容

デジタル計算機の試験診断 (4,118) | 試験手段 (1,073) | シミュレータ (206) | 疑似エラー (35)

Fターム[5B048DD18]に分類される特許

1 - 20 / 35

自己診断機能付き装置

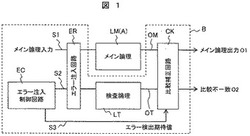

【課題】自己診断する論理の範囲を比較回路以外の検査論理、更にはメイン論理に広げ、検査論理、メイン論理に異常がある場合、比較回路が不一致を発生する前に検出し装置の交換ができるようにする。

【解決手段】同じ入力が与えられ、同じ論理演算を実施する第1と第2の論理部、第1と第2の論理部のいずれかにエラー信号を与えるエラー注入回路、第1と第2の論理部の出力を入力し選択した信号を与える選択回路と第1と第2の論理部の出力を比較し、比較不一致信号を与える比較回路とを備えた比較補正回路から構成され、比較補正回路は、第1と第2の論理部のいずれかにエラー信号を与えた時、第1と第2の論理部の出力が不一致にならない場合、または、第1と第2の論理部にエラー信号を与えないときに、第1と第2の論理部の出力が不一致になる場合に異常があると判断する。

(もっと読む)

フォールトトレラントシステム

【課題】可用性と信頼性を向上させるために必要なテスト機能を備えるフォールトトレラントシステムを提供する。

【解決手段】保守用計算機102は、指定した演算用計算機103に対し、演算用計算機103に組み込まれている擬似故障処理部302を実行させる命令を、プログラム起動制御部204から送信する。入出力制御部203は、同期検出部205が演算用計算機103の同期が外れたことを確認したことを受けて、演算用計算機103の再組み込み処理部303に再組み込みを指示する。その後、入出力制御部203は、同期検出部205が演算用計算機103の再組み込み処理が失敗したことを確認したら、ログ記録部305を通じてログファイル307からエラーログを収集する。以上の一連の動作は、テスト機能制御テーブル206に記載された内容に従って、各演算用計算機103に対して繰り返し実行される。このため、効率よくエラーログを収集できる。

(もっと読む)

擬似障害発生方法と装置

【課題】電子回路装置に対する擬似障害発生を容易化し、試験・評価等の作業を効率化する装置、方法の提供。

【解決手段】

電子回路装置(100)を構成する回路基板(105)上のIC(104)のON/OFF端子に接続部103を介して接続する制御部102が、ケーブルコネクタ部(101)を介してPC(110)の制御により、IC(104)のON/OFF端子に動作中の第1の値とは異なる第2の値を設定することで擬似障害を発生させる。

(もっと読む)

故障再現装置、故障再現方法

【課題】短時間でCPUコアの十分な検出率の故障を検出することが可能な故障再現装置を提供すること。

【解決手段】故障再現装置は、影響の現れる命令と影響が現れた後の命令が故障内容に対応づけて登録された故障ライブラリ11と、アプリを記憶したアプリケーション記憶手段36と、アプリをCPUが実行した際の動作を別々にシミュレートする第1のシミュレート手段55及び第2のシミュレート手段56と、第1のシミュレート手段が影響の現れる命令を実行したことを検出して、アプリの実行を中断させると共に第2のシミュレート手段に通知する実行検出手段12と、前記第2のシミュレート手段に影響の現れる命令と対応づけられた影響が現れた後の命令を実行させる命令置き換え手段13と、を有し、第1のシミュレート手段が第2のシミュレート手段が実行した影響が現れた後の命令の実行結果を引き継いでアプリの実行を再開する。

(もっと読む)

データ比較回路の故障診断装置

【課題】 2つのデータ列を比較して一致・不一致を判定するデータ比較回路10について、一致側への固定故障を診断可能とする。

【解決手段】 データ比較回路10は、比較するデータ列がそれぞれ所定ビット数ずつ複数のデータに分けられて入力される複数の排他的論理和回路(XOR回路)11−1、11−2、・・・と、これらの出力が入力されて比較結果を出力する論理和回路(OR回路)12とから構成される。ここにおいて、データ比較回路10の入力側で1つのデータ列をそのまま入力させるモードと、ビット反転処理などにより他のデータ列と不一致となるように変化させて入力させるモードとを切替え可能な切替回路13a−1、13a−2、・・・を設ける。そして、前記切替回路により1つのデータ列を変化させて入力させたときのデータ比較回路10の比較結果に基づいて、故障の有無を診断する。

(もっと読む)

二重化回路、半導体装置およびテスト方法

【課題】比較回路の故障検出が可能な二重化回路、半導体装置およびテスト方法を提供する。

【解決手段】実施形態の二重化回路は、本体回路1と、本体回路1と同じ回路機能を有する監視用回路2と、本体回路1の出力信号OUTと監視用回路2の出力信号MNTを比較し、比較結果が不一致であるときに故障検出信号ERRを出力する比較回路3と、を備える。また、この二重化回路は切り替え回路4を備えている。切り替え回路4は、通常動作モードとテストモードの切り替えを制御するテスト信号がテストモードを示すときは、監視用回路2への入力信号ITを、本体回路1への入力信号INとは異なる信号とする。

(もっと読む)

計算機の診断装置及び診断方法

【課題】 この発明は、計算機が通常動作の状態でも、エラー検出機能の検出結果からエラー検出機能を診断する、計算機の診断装置を提供する。

【解決手段】 この発明の計算機の診断装置は、診断用データを格納した診断用メモリ31と、この診断用メモリ31からCPU(中央演算処理装置)10が読み出したデータを基準データと比較し、その結果をメモリアクセスエラー情報格納部21に記憶するメモリアクセスエラー検出部20と、このメモリアクセスエラー情報格納部21を確認した後に消すメモリアクセスエラー検出部診断処理11と、を備えるものである。

(もっと読む)

周辺機器障害模擬システム、周辺機器障害模擬方法および周辺機器障害模擬プログラム

【課題】I/OポートやメモリマップトI/Oや割込みに関する障害を模擬し、システムの障害処理機能の正常性を確認できるようにすることを目的とする。

【解決手段】障害模擬設定部131は障害模擬定義情報121に指定されたI/O143やメモリ142内のアドレスにアクセスが発生したときに障害模擬実行部132を呼び出すアクセス呼出し設定を行う。また、障害模擬設定部131は障害模擬定義情報121に指定された割込みが発生したときに障害模擬実行部132を呼び出す割込み呼出し設定を行う。アクセスが発生したとき、障害模擬実行部132はビットセットにエラービットを設定する。また、割込みが発生したとき、障害模擬実行部132は割込みを遅延させる。試験対象システム110はエラービットに従って障害処理を実行する。また、試験対象システム110は遅延した割込みに対して障害処理を実行する。

(もっと読む)

電子回路装置および電子回路装置の動作検証支援方法

【課題】設計者が容易に動作検証をすることを可能にする。

【解決手段】電子回路装置100の検証支援処理回路22は、電子回路検証装置200から送信される検証指示情報に基づいて、機能ブロック回路1の検証を制御する検証制御情報を生成し、機能ブロック回路1へ送信する。機能ブロック回路1は、その検証制御情報を受信すると、遷移停止制御回路40、状態コード注入回路50およびエラー状態注入回路80を介して、その検証制御情報で指定される任意の状態コードおよびエラー状態を機能ブロック回路1の状態コードレジスタおよびエラー状態レジスタに注入した上で、機能ブロック回路1の動作を開始または停止させる。状態履歴記憶回路60には、そのときの状態コードおよび過去の最新の所定動作サイクル数の状態コードの履歴が記憶されている。検証支援処理回路22は、その状態コードの履歴を取得して、電子回路検証装置200へ送信する。

(もっと読む)

故障制御装置、プロセッサコア、演算処理装置、情報処理装置および擬似故障制御方法

【課題】擬似故障の発生にかかる信号の伝播遅延を考慮した故障制御装置、プロセッサコアおよび擬似故障制御方法を得ること。

【解決手段】故障発生対象回路40_1〜40_nの近傍に、擬似故障を発生させる擬似故障発生装置30_1〜30_nを配置する。擬似故障制御装置20は、擬似故障発生装置30_1〜30_nのいずれかを選択してローカル故障モードレジスタ31に故障の内容をセットする。擬似故障発生装置30_1〜30_nは、故障の内容に対応するイベントの発生を監視して擬似故障制御装置20に通知し、擬似故障制御装置20は、イベントの発生回数に基づいて擬似故障発生装置30_1〜30_nに故障の発生を指示する。

(もっと読む)

擬似障害発生装置及び擬似障害発生方法及び擬似障害発生プログラム及び試験システム

【課題】2つの装置間で送受信されるデータの内容に応じて擬似的に障害を発生させる。

【解決手段】サーバとディスクとの間に接続された障害シミュレータ11において、データ保存部A111は、データ受信部A101によりサーバから受信されたデータを複データ保持部172に順次保存する。コマンド解析部141は、複データ保持部172に保存されている、最先のデータから1フレーム分のデータを解析して、当該1フレーム分のデータが特定のコマンドであるかどうかを判定する。特定のコマンドでなければ、制御部131は複データ保持部172から最先のデータを取り出してデータ送信部A102によりディスクA14へ送信する。特定のコマンドであれば、制御部131は予め定められた時間が経過するまで待機してから当該1フレーム分のデータをデータ送信部A102によりディスクA14へ送信することで擬似障害を発生させる。

(もっと読む)

計算機装置及び情報処理方法及びプログラム

【課題】試験対象計算機上にログを収集する手段を設けず、かつ、試験対象計算機状態に関わらずログを収集可能とする。

【解決手段】試験対象計算機(仮想マシン)109は、仮想マシンディスク121をログの書き込み先としており、検証端末101からの指示に基づき、模擬故障発生部115が模擬故障を発生させると、試験対象計算機(仮想マシン)109は模擬故障に対する動作状態を表すログを仮想マシンディスク121に書き込み、管理ホスト112の仮想マシンディスクアクセス部114が仮想マシンディスク121にアクセスして、試験対象計算機(仮想マシン)109により書込まれたログを取得し、試験対象状態判定部113が検証端末101にログを送信する。

(もっと読む)

障害監視回路、半導体集積回路及び故障個所特定方法

【課題】故障情報がシステムを安全な状態に保つ回路まで確実に伝達され、システムとしての安全性を確保できる障害監視回路、半導体集積回路及び故障個所特定方法を提供すること

【解決手段】本発明にかかる障害監視回路は、周辺回路の障害により当該周辺回路を監視する周辺監視回路100から出力される障害信号を第1の経路を介して取得する。さらに、取得した障害信号を外部監視装置へ出力する障害信号出力部12を備えている。また、周辺監視回路100から出力される障害信号を第1の経路とは異なる第2の経路を介して取得し、取得した障害信号に基づいて半導体集積回路の動作制御を行う制御部14を備えるものである。

(もっと読む)

エミュレータ

【課題】ユーザーシステム上のデバッグ対象CPUの仕様の変更に柔軟に対応可能なエミュレータを提供する。

【解決手段】エミュレータ(30)は、デバッグ対象とされるユーザシステムに結合可能なユーザインタフェース(40)と、上記ユーザシステムに搭載されるCPU論理機能を代行するためのCPU論理(80)と、上記ユーザシステムのデバッグを可能とするデバッグ論理機能を有するデバッグ論理(90)とを含む。上記CPU論理と、上記デバッグ論理とを、それぞれ任意の論理を書込み可能なFPGAによって形成し、且つ、それらが互いに協調して動作可能に結合することで、ユーザーシステム上のデバッグ対象CPUの仕様の変更に柔軟に対応できるようにする。

(もっと読む)

疑似障害発生装置

【課題】任意のタイミングにて複数のユニットに障害が発生したことを電子機器が検出する状況を再現することが可能な疑似障害発生装置を提供すること。

【解決手段】疑似障害発生装置110は、複数のユニット101,102,…を備える電子機器100に適用される。疑似障害発生装置110は、ユニット101,102,…を特定するためのユニット特定情報と、障害を発生させるタイミングを表すタイミング情報と、を含む障害発生情報を受け付ける。疑似障害発生装置110は、受け付けた障害発生情報に含まれるタイミング情報が表すタイミングにて、その障害発生情報に含まれるユニット特定情報により特定されるユニットに疑似的に障害を発生させる。これによれば、任意のタイミングにて複数のユニット101,102,…に障害が発生したことを電子機器100が検出する状況を再現することができる。

(もっと読む)

異常通報システム及び診断方法

【課題】情報処理装置の有する異常通報機能が全体として正常に動作するか否かを確認できるようにすること。

【解決手段】管理サーバマシン20は、監視対象サーバマシン10のシステム監視機構15に対し、定期的に、疑似エラーコードを引き渡し、システム監視機構15が、疑似エラーコード通知プログラム10bに従って、オペレーティングシステム10cに疑似エラーコードを通知することによって、オペレーティングシステム10cより上流に対して擬似的な故障の発生を認識させる。管理サーバマシン20は、その疑似エラーコードの引き渡しの応答として、監視対象サーバマシン10からエラーメッセージを受信すると、そのエラーメッセージの内容とシステム監視機構15に引き渡した疑似エラーコードとに基づいて、異常通報機能の経路のうち管理サーバマシン20までの経路の動作が正常であるか否かを判定し、判定結果を保守員マシン30に通知する。

(もっと読む)

情報漏洩防止保守システム、方法、端末

【課題】 情報通信機器の保守時の情報漏洩を防止して、運送中の機器の盗難や修理中の部品の盗難などの問題にも対応することが可能な情報漏洩防止保守システムの実現を課題とする。

【解決手段】 保守ツール50は、保守対象のネットワーク機器から記憶されている設定情報を吸い上げる吸上げ機能と、吸い上げた設定情報を客先に搬送した保守用ネットワーク機器に投入する設定情報投入機能と、保守対象ネットワーク機器を保守用ネットワーク機器と入れ替えて正常に動作した場合に保守対象ネットワーク機器の設定情報を消去する設定情報消去機能と、セキュリティー面での安全に配慮されたネットワーク10を介して通信する通信機能とを備え、保守対象ネットワーク機器を保守用ネットワーク機器と入れ替えて正常に動作した時点で設定情報を含めた保守作業報告をリペア部品修理サーバ60に送信する。

(もっと読む)

擬似障害状況発生装置

【課題】情報処理装置間を接続するインターフェースケーブルに実際に発生する障害の状況を擬似することができて評価に利用可能な擬似障害状況発生装置を提供する。

【解決手段】情報処理装置2A,2Bに接続するインターフェースケーブル1の障害を擬似的に発生させるために、装置本体に信号入力部3及び信号出力部4とを設け、装置本体内には、信号入力部3に接続する第1の信号線11と、信号出力部4に接続する第2の信号線12とを設け、両者は係合部20で係合させる。この係合部20にはアクチュエータ5を接続し、このアクチュエータ5によって第1と第2の信号線11,12を係合状態を保ちながら相対的に移動させれば、両者の係合状態を変更できる。

(もっと読む)

データ処理装置、システム、プログラム、及び、方法

【課題】 動的プログラム検証を行う場合、検出された障害を発生させるための入力値に対する条件を人手により検証しなければならない。

【解決手段】 障害検出時の実行トレース上の障害発生命令と障害内容と障害判定ルールから障害判定条件式を生成し、障害検出時の実行トレース上の障害発生命令を前記障害判定条件式で置換した修正トレースを生成する実行トレース修正手段と、前記修正トレース中の分岐命令の条件式乃至は前記障害判定条件式を、同修正トレース中の代入式に基づいて書き換え、障害発生となる入力値の値域を定義する障害発生条件式として抽出する障害発生条件抽出手段とを有する。

(もっと読む)

論理検証装置、論理検証方法

【課題】シミュレーション時のパリティエラーの発生をプロセッサ内のリソースを増やすことなく実現し、動作の検証を行うことを容易にする。

【解決手段】エラー制御用メモリ領域をCPUの外、エラー発生制御回路とエラー発生回路をCPU内部のハードマクロ(メモリ)論理シミュレーション用機能モデル内に設ける。これらを一つの論理シミュレーション環境内に設けることで、CPUコアからハードマクロ(メモリ)論理シミュレーション用機能モデルへのアドレスをフルに利用したシミュレーション実行中にパリティエラーの発生をプログラム上でコントロールできる。

(もっと読む)

1 - 20 / 35

[ Back to top ]