Fターム[5B054BB02]の内容

Fターム[5B054BB02]に分類される特許

1 - 17 / 17

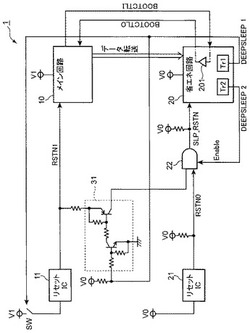

電子回路

【課題】複数の電源のうち何れかの電源が瞬断したときに、確実に回路全体をリセットすること。

【解決手段】電源V1に瞬断が発生すると、リセット信号RSTN1がローレベルになりメイン回路10は動作が停止する。AND回路22はローレベルの信号SLP_RSTNを出力する。信号SLP_RSTNがローレベルになると、省エネ回路20は動作を停止し、記憶部201の記憶内容もリセットする。電源V1が復帰すると、リセット信号RSTN1はハイレベルになり、メイン回路10は信号BOOTCTLIを出力する。省エネ回路20は記憶部201の記憶内容が初期状態であるため、信号BOOTCTLOをループバックすると共に、記憶部201の記憶内容を起動処理済みであることを示す内容に書き換える。メイン回路10は、この信号BOOTCTLOを受け取ると、省エネ回路20に対して起動処理を実行する。

(もっと読む)

リセット回路および電子機器

【課題】リセット対象部を良好にリセットさせる。

【解決手段】実施形態のリセット回路および電子機器は、入力部と、リセット部と、を備える。前記入力部には、BIOSを実行する実行部を有するリセット対象部に設けられた異常検出部から出力された異常検出信号が入力される。前記リセット部は、前記入力部に前記異常検出信号が入力された場合、前記リセット対象部をリセットさせる。

(もっと読む)

電子機器装置

【課題】電子機器装置において、電源供給が瞬間的に断たれたときに、マイコンが異常状態にならないようにする。

【解決手段】電子機器装置1は、マイコン6と、リセットIC7と、電圧低下回路8とを備える。マイコン6は、ハイレベルの信号が入力されている状態からローレベルの信号が入力される状態に変化すると、動作をリセットし、ローレベルの信号が入力されている状態からハイレベルの信号が入力される状態に変化すると、起動処理を実行し、その後、通常処理を実行する。リセットIC7は、所定電圧値未満の電圧が入力されているときには、マイコン6にローレベルの信号を入力し、所定電圧値以上の電圧が入力されているときには、マイコン6にハイレベルの信号を入力する。電圧低下回路8は、商用AC電源10から電子機器装置1への電源供給が瞬間的に断たれたときに、リセットIC7に入力される電圧を一時的に所定電圧値未満に低下させる。

(もっと読む)

データプロセッサ及びデータ処理システム

【課題】POR/LVD検出回路によるリセット信号の外部出力と外部リセット信号の入力を同一端子で兼用でき、外部出力するリセット信号が外部からのリセット信号の入力系に回り込むことを抑制する。

【解決手段】リセット信号の外部出力と外部からのリセット信号の入力に外部リセット端子(RESION)を兼用させ、電源電圧の安定状態では外部リセット端子からのリセット入力を許可し、検出回路(3)により電源電圧の投入又は電源電圧のレベル低下のリセット要因を検知したときはその検出信号を利用して、入出力バッファ(4)にリセット信号を外部リセット端子に出力させると共に入出力バッファからその入力経路への当該リセット信号の回り込みをマスクする制御を行う、リセットコントローラ(10)を採用する。外部へのリセット信号の出力より早く前記マスクを行い、マスク期間は、リセット指示から解除までの期間よりも長い期間とする。

(もっと読む)

電子機器

【課題】 電源が遮断された場合に、揮発性の記憶装置内のデータを不揮発性の記憶装置に退避させ、リセット処理を行うことができる電子機器を提供することを目的とする。

【解決手段】 電源遮断時に電源電圧Vddが閾値電圧V1以下になれば第1リセット信号を出力するリセット生成部101と、電源電圧Vddが閾値電圧V1より低い閾値電圧V2以下になると第2リセット信号を出力するリセット生成部201と、第1リセット信号の出力の終了に基づいて、復帰時リセット信号を出力する復帰時リセット生成部103を設ける。データの退避を行う退避部203は、第1リセット信号によりデータの退避を開始し、第2リセット信号に基づいてリセットされる。また、退避部203は復帰時リセット信号に基づいてリセットされるので、電源電圧Vddが電圧V1以下になれば、データの退避部203はリセットされることになり、低電圧状態による異常動作を防止できる。

(もっと読む)

通信制御装置、画像形成装置、通信制御方法及び通信制御プログラム

【課題】SDカード等のカード型メモリに対する不要な初期化処理を行わないように制御することが可能な通信制御装置を提供する。

【解決手段】カード型メモリ(5)との間のインターフェイスを制御する通信制御装置であって、第1の条件のリセット処理(例えば、電源リセット)が行われた場合には、カード型メモリ(5)の初期化を行い、第2の条件のリセット処理(例えば、省エネリセット)が行われた場合には、カード型メモリ(5)の初期化を行わないことを特徴とする。

(もっと読む)

電子回路

【課題】大容量のコンデンサを使用することなく、電源の瞬断が発生した場合に制御回路の誤動作を防止できる電子回路を提供する。

【解決手段】シーケンサ8の動作用電源を、主電源VDDからダイオード6を介して充電されているコンデンサ7より供給し、クロック生成回路1には、主電源VDDを供給して動作させ、シーケンサ8に対してはレベルシフト回路2によりクロック信号のレベルをシフトさせて出力する。そして、低電圧検出回路5が主電源電圧が検出閾値VPOR1よりも低下したことを検出すると、レベルシフト回路2は、シーケンサ8に対するクロック信号の供給を停止する。

(もっと読む)

システムリセット回路

【課題】CPUシステムが正常に動作するまで、連続でリセット信号を出力することにより、システムの誤動作を解消したシステムリセット回路を提供する。

【解決手段】ロジックシステム1に供給される電源2の投入、電圧低下を監視する電源監視回路3と、CPU4の動作を監視するウォッチドッグタイマー回路5とを有する。電源監視回路3からは、電源投入、電圧低下時にリセット信号が出力される。ウォッチドッグタイマー回路5は、CPU4の動作を監視し、CPUの異常時には、CPU4が正常に動作するまでの間、連続的にロジックシステム1に対してリセット信号を出力するので、CPU4がリセット状態から正常に立ち上がるまでの間、ロジックシステム1が起動されることがなく、そのリセット状態が継続する。

(もっと読む)

電子制御ユニットのリセット回路

【課題】 2つのCPUを備える電子制御ユニットのリセット回路において、CPUのリセットの原因を判別できるようにする。

【解決手段】 メインリセット発生部13は電源回路15出力の電圧低下検知時とメインCPUからのWDT信号監視による暴走検知時とで異なるパルス幅のリセット信号RSaを出力する。サブリセット発生部14も電源の低電圧検知機能を有する。メインリセット発生部13における低電圧検知用の閾値Vthaはサブリセット発生部14における低電圧検知用の閾値Vthbよりも高く設定され、電源の電圧低下はまずメインリセット発生部13が検知してメインCPU11をリセットする。サブリセット発生部14はメインリセット発生部13が出力したリセット信号RSaを監視して、そのパルス幅に基づいてリセットの原因が電源の電圧低下であるかメインCPU11の暴走であるかを判別する。

(もっと読む)

半導体装置のシングルイベント補償回路

【課題】 半導体装置の耐放射線を向上すると共に、半導体装置への汎用部品の採用を可能にした半導体装置のシングルイベント補償回路を提供する。

【解決手段】 放射線環境下で使用される半導体装置10のシングルイベント補償回路において、半導体装置10におけるシングルイベントの発生を検出する検知手段3、5を備え、当該検知手段3、5の検出結果により半導体装置10の電源2をオフ/オンする。シングルイベント発生時に半導体装置10への電源供給をオフ/オンすることにより、半導体装置10に搭載されるCPU等のICチップをリセットすることができ、これによりシングルイベントにより喪失した装置機能を復帰させることができる。

(もっと読む)

半導体集積回路

【課題】 電源電圧が低下した場合に、内部回路の誤動作を正確に検知して確実にリセット信号を生成することが可能な半導体集積回路を提供する。

【解決手段】 モニタ用ラッチ回路4a,4b,・・・は、周辺回路に含まれるラッチ回路と同等の構成を有する。瞬停時において、電源電位VCCが低下してモニタ用ラッチ回路4a,4b,・・・のうちのいずれかの保持データが反転すると、誤動作検出回路3からの副リセット信号/POR2が活性化レベルの「L」レベルにされ、論理回路2からのリセット信号/POR3が活性化レベルの「L」レベルにされる。したがって、周辺回路の誤動作を正確に検知して確実にリセット信号を生成することが可能となる。

(もっと読む)

複数のマイコンのパワーオンクリア動作の制御方法

【課題】 複数のマイコンのPOC動作を一つのPOC回路により一括して確実に行う複数のマイコンのパワーオンクリア動作の制御方法を提供する。

【解決手段】 パワーオンクリア信号出力部1Cの制御を行うマスタマイコン1と、パワーオンクリア信号出力部1Cの制御を行わないスレーブマイコン2〜Nとを備えた電子回路において、電子回路の電源電圧が所定値以下となった後に該所定値以上になった際は、パワーオンクリア信号出力部1Cが出力したパワーオンクリア信号によりマスタマイコン1とスレーブマイコン2〜Nがパワーオンクリア動作を行う一方、パワーオンクリア動作が終了した際は、スレーブマイコン2〜Nはマスタマイコン1に動作開始信号を出力し、マスタマイコン1はスレーブマイコン2〜Nすべてから動作開始信号を受け取った場合にパワーオンクリア信号出力部1Cにパワーオンクリア信号を停止するクリア信号を出力する。

(もっと読む)

リセット回路

【課題】 リセットシーケンスを電源ON時および電源OFF時において確実に守ることができるリセット回路を提供する。

【解決手段】 リセットIC2は、電源端子Vddへ電源V1が加えられた時、一定時間t1の間第1のリセット信号R1を出力した後リセットを解除し、電源端子Vddの電源V1がOFFとされた時リセット信号を”L”レベルとする。第2のリセットIC9は、電源端子Vddへ電源V2が加えられた時、一定時間t2の間第2のリセット信号R2を出力した後リセットを解除し、電源端子Vddの電源がOFFとされた時、リセット信号R2を”L”レベルとする。トランジスタ5、8は、第1のリセット信号R1のリセット状態が解除された時、第2の電源V2を第2のリセットIC9に加える。

(もっと読む)

画像形成装置

【課題】 停電などの瞬断でハードディスクの動作中にハードディスクの電源が止まってしまうとハードディスクの記憶領域が壊れてしまう。

【解決手段】 停電時にはハードディスクの書き込みを終了させる最小構成の電源をバックアップしハードディスクのライトアクセス時のエラーを防止する。

(もっと読む)

電子機器

【課題】 電源スイッチにトグルスイッチを用いた電子機器において、或る回路の異常でCPUのハードウェアリセットがかかった場合、異常回路を確実に停止させ得るようにする。

【解決手段】 ユーザが電源スイッチ(トグルスイッチ)104をターンオフした時、CPU112は、主電源回路102がターンオフする前に、起動判定フラグ128を値0にリセットしてEEPROM126に格納する。その後、主電源回路102がターンオンしてCPU112が起動する時、CPU112はEEPROM126内の起動判定フラグ128を調べ、その値0であれば、それを値1に変更してプリンタ100を正常に起動し、そうでなければ、エラー表示をして、ハードウェアリセットの原因となる所定回路を停止させる。これにより、回路異常でハードウェアリセットがかかった場合、電源スイッチがオンのままでも通常起動が回避される。

(もっと読む)

電力障害の検出及び応答

パーソナル・コンピュータ・アセンブリ(マザーボード)、データを格納するメモリ、印加された電力の損失を検出する手段、及び当該検出する手段に応答して、パーソナル・コンピュータのプロセッサ及びメモリによるデータ転送を禁止する手段を備えるコンピュータ・システムである。本発明に従って、メモリは、不揮発性メモリを備え、そして当該禁止する手段が、信号をメモリに印加して、メモリのデータ転送動作を禁止する。印加された電力の損失を検出する手段が、稼動している電力をパーソナル・コンピュータ・アセンブリに供給するための電源の電力幹線接続における損失を検出する。機械制御装置は、本発明に従ったコンピュータ・システムを備える。  (もっと読む)

(もっと読む)

電気機器

【課題】 省エネモード中にメイン制御基板の電源をオフにしつつ他の制御基板にはリセットがかからない電気機器において、特別な制御用構成部品を新たに設けずに済む機器を提供することにある。

【解決手段】 この画像形成装置1は、節電のための省エネモードによる制御が可能な機器であって、電源部3と、エンジンPCB5と、画像処理PCB9とを備えている。エンジンPCB5は、エンジン部の制御を行う。画像処理PCB9は、エンジンPCB5に接続され、画像形成部の制御を行うとともに、省エネモードに移行する際に電源部3のエンジンPCB5への電源供給を停止するための電源オフ信号を出力し、電源オフ信号によって自身がリセットされるのを防止するための電源オフリセット防止回路32を有する。

(もっと読む)

1 - 17 / 17

[ Back to top ]