Fターム[5B056CC01]の内容

Fターム[5B056CC01]に分類される特許

1 - 9 / 9

集積回路デバイスにおける離散フーリエ変換

離散フーリエ変換を行う回路。回路は、固定論理デバイス内に提供することができる、またはプログラム可能論理デバイス等のプログラム可能集積回路デバイス内に構成することができる。回路は、離散フーリエ変換演算の入力値の仮数を加算するための浮動小数点加算段と、浮動小数点加算段の出力を回転因子で乗算するための固定小数点段と、を含む。固定小数点段は、複数のセットの回転因子を記憶するためのメモリを含み、それらのセットはそれぞれ、異なる量だけシフトされた個別の回転因子のコピーと、浮動小数点段の出力の指数間の差分を判定し、その差分をセットのそれぞれ内のその個別の回転因子のそれらのコピーから選択するためのインデックスとして使用するための回路と、を含む。  (もっと読む)

(もっと読む)

演算装置及び演算方法

【課題】 浮動小数点積和演算あるいは固定小数点乗算がそれぞれ実行される場合に、無効な電力消費が発生するという問題点がある。

【解決手段】 通知された演算命令に基づいて選択した入力データを構成する複数の部分データそれぞれについて最上位ビットから連続している0の数を計数して第1のリーディングゼロカウントとし、第1のリーディングゼロカウントに基づいて入力データについて最上位ビットから連続している0の数を計数して第2のリーディングゼロカウントを出力するリーディングゼロ手段と、第1のリーディングゼロカウントを入力して演算命令に基づいた演算を行うとともに、第2のリーディングゼロカウントを入力して演算命令に基づいた演算を行う第1の演算手段と、第1の演算手段及びリーディングゼロ手段と連携して演算命令に基づいた演算を行う第2の演算手段とを有する。

(もっと読む)

浮動小数点積和演算装置、浮動小数点積和演算方法、及び浮動小数点積和演算用プログラム

【課題】IEEE754R規格に準拠した浮動小数点積和演算を行う。

【解決手段】浮動小数点演算器において、浮動小数点乗算器と浮動小数点加算器を個別に有し、通常はそれぞれが独立で動作するが、浮動小数点積和命令時には、浮動小数点乗算器は、浮動小数点乗算の中間結果を浮動小数点加算器に受け渡し、浮動小数点加算器は、中間結果幅に対応した桁合わせシフト(左右シフト)と仮数部絶対値加算と正規化シフトを行い、浮動小数点加算を行う。

(もっと読む)

浮動小数点ユニットにおけるオーバーシフトの高速検出のためのメカニズム

【解決手段】

浮動小数点ユニットは、各々が指数及び仮数を有する第1及び第2の浮動小数点数の間で浮動小数点加算動作を実行する浮動小数点加算器を含む。浮動小数点ユニットはまた、第2の指数の値が第1の指数の値と同一になるように第2の仮数をシフトするビット位置の数に対応するシフト値を計算し得るアライメントシフト器を含む。アライメントシフト器はオーバーシフト状態を検出してよく、オーバーシフト状態においては、シフト値は、選択されたオーバーシフトスレッショルド値以上である。選択されたオーバーシフトスレッショルド値は、最小オーバーシフトスレッショルド値及び最大オーバーシフトスレッショルド値を含むオーバーシフト値の範囲内の2進数を備えると共に最下位ビットで始まる最多数の連続するゼロのビットを有している。

(もっと読む)

融合型積和演算機能ユニット

【課題】倍精度のサポートを加えることによる、チップ面積に対する影響が低減する融合型積和演算機能ユニットを提供する。

【解決手段】グラフィックスプロセッサに、レンダリングに使用される単精度の機能ユニットに加えて、倍精度の算術演算の直接的なサポートを提供する機能ユニットが追加される。倍精度の機能ユニットは、融合型積和演算を含む複数の異なる演算を、少なくとも倍精度の幅であるデータ経路及び/又は論理回路を使用して、実行することができる。倍精度の機能ユニット及び単精度の機能ユニットは、共通の命令発行回路によって制御することができ、コアに含まれている倍精度の機能ユニットの複製の数を、単精度の機能ユニットの複製の数よりも少なくすることができる。

(もっと読む)

演算装置、逆数の近似計算プログラムおよび近似計算方法

【課題】逆数または平方根逆数の近似計算をニュートンラフソン法によって行う際、同程度の大きさの浮動小数点数の減算処理に伴ってプロセッサで生じるビットシフト処理に起因するストールを回避でき、計算速度を向上できる演算装置を提供する。

【解決手段】演算装置1は、初期近似精度を持つ初期近似逆数に対して近似計算を行う。まず、中間値演算部15が、ニュートンラフソン法の1段近似計算により、中間近似精度を持つ中間近似逆数を計算し、そして、目標値演算部17が、ニュートンラフソン法の多段近似計算によって目標精度まで精度を高める。中間近似精度は、プロセッサでの浮動小数点数の減算処理に伴う仮数部のビットシフトによるストールが生じない上限ビットシフト量に対応する非ストール誤差を残すように設定されている。この中間近似精度が得られるように、中間値演算部15では、故意に誤差を拡大した1段近似計算が行われる。

(もっと読む)

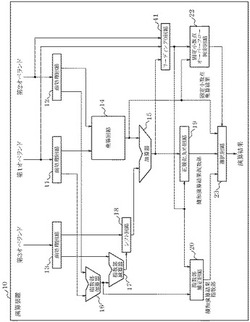

演算処理装置

【課題】数学関数の値を求めるテーラー級数演算処理を、従来よりも高速に実行可能な演算処理装置を提供する。

【解決手段】任意の数学関数のテーラー級数演算の係数データを格納する係数テーブルのセットを、専用のメモリである係数テーブルセット10に記憶する。ある数学関数の値をテーラー級数演算で求める際には、テーラー級数の次数番号21、係数テーブルのセット番号22を用いて、係数テーブルセット10から所望の係数データを取得し、それを、マルチプレクサ27を介して浮動小数点積和演算器1050に供給する。浮動小数点積和演算器1050は、該係数データを用いて積和演算を実行し、任意の数学関数の値をテーラー級数演算により求める。

(もっと読む)

計算装置、および、計算方法

【課題】浮動小数点数の演算(内積演算、総和演算)において、高精度の結果を算出すること。

【解決手段】本発明は、浮動小数点形式で表現された複数の被演算子の入力を受け付ける入力部104と、入力部104に入力されたデータを記憶する記憶部と、記憶部に記憶された複数の被演算子の加算処理において、各被演算子を整数配列を使用して表現し、整数配列の値どうしを加算し、加算した結果を浮動小数点数形式に変換する演算部と、演算部の演算結果を出力する出力部105と、を有することを特徴とする。また、入力部104は、内積演算におけるベクトルの乗算結果を被演算子として入力を受け付けることを特徴とする。

(もっと読む)

ベクトル積和演算回路

【課題】 ベクトルレジスタの各要素の書換えを行うことなく、2つのオペランドの演算を容易に行うことが可能なベクトル積和演算回路を提供する。

【解決手段】 マスクレジスタ31〜33は各オペランド毎にデータの有効/無効を示すマスクビットを格納する。制御回路11〜13は演算モードと各オペランドに付随するマスクビットとから選択信号を生成する。機能セレクタ1〜3は各オペランドを入力とし、オペランドデータと予め設定された所定値(“0”または“1”)とのうちのいずれかを制御回路11〜13からの選択信号にしたがって選択し、積和演算回路の各回路に出力する。

(もっと読む)

1 - 9 / 9

[ Back to top ]