Fターム[5B057CH03]の内容

画像処理 (340,757) | 処理部 処理装置、処理システム (15,018) | 演算器 (6,373) | マルチプロセサ (674) | マトリックス型 (21)

Fターム[5B057CH03]に分類される特許

1 - 20 / 21

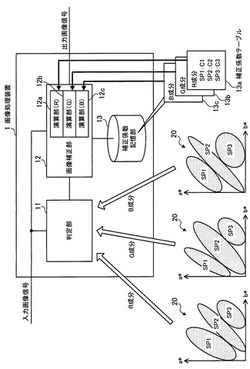

画像処理装置、撮像装置、画像処理方法および画像処理プログラム

【課題】画像の補正精度を向上させる。

【解決手段】判定部11は、入力画像信号の値が、色分布において分割された複数の分割領域SP1〜SP3のいずれに含まれるかを判定する。これらの複数の分割領域はRGBの色成分ごとに定義されており、判定部11は、入力画像信号の値が複数の分割領域のいずれに含まれるかを色成分ごとに判定する。画像補正部12は、色成分ごとかつ分割領域ごとに補正係数が登録された補正係数記憶部13から、入力画像信号の値が含まれると判定された色成分ごとの分割領域にそれぞれ対応する補正係数を読み出し、出力画像信号におけるRGBの各出力値を、補正係数記憶部13から読み出した対応する色成分についての補正係数を用いて算出する。

(もっと読む)

画像認識プロセッサ

【課題】各方式の演算を網羅して画像認識に必要な幅広い機能変更に対応しつつ、回路効率を最大にした画像認識プロセッサを提供する。

【解決手段】画像認識プロセッサは、第1の演算器アレイと、第2の演算器アレイとを備え、前記第1の演算器アレイは、再構成可能な回路として、ビット連接機能を有する第1回路(concat)、および、シフトと減算機能とを有する第2回路(shift&sub)を含み、ルックアップテーブル機能を有する第3回路(LUT)、積和演算機能を有する第4回路(MAC)、および、多入力加算機能を有する第6回路(addtree)を含まず、前記第2の演算器アレイは、再構成可能な回路として、前記第3回路、前記第4回路、前記第5回路および前記第6回路を含み、前記第1回路および前記第2回路を含まない。

(もっと読む)

画像データ圧縮装置および印刷システム

【課題】画像データの性質に適した圧縮回路を設ける場合よりもハードウエア規模の増大を抑制した画像データ圧縮装置を提供することを目的とする。

【解決手段】動的再構成可能プロセッサ30は、その動作制御を行う制御部38、複数の演算処理要素42を含む回路構成部40、および、制御部38が実行する回路構成プログラムを記憶する回路メモリ36を備える。演算処理要素42は、その演算機能の設定状態に応じた演算処理を実行する。回路構成部40では、各演算処理要素42の演算機能の設定および演算処理要素42間の接続状態を変更することで複数種の回路を構成可能である。制御部38は、回路構成プログラムに従い、各演算処理要素42の演算機能設定および演算処理要素42の接続処理を処理対象のデータに応じて実行し、回路を構成する。

(もっと読む)

情報処理装置及び並列動作制御方法

【課題】実行する処理の負荷に応じて処理時間を短縮するよう並列処理を制御できる情報処理装置を実現する。

【解決手段】スケジューラ311は、画像処理プログラム162内の画像解析モジュール21、固定演算モジュール22、及び変動演算モジュール23のタスクを、実行順序に従って演算コア110へ割り当てる。負荷算出部33は、画像解析モジュール21による入力画像の解析が完了したことに応答して、この解析結果に基づいて画像処理プログラム162の処理負荷を算出する。負荷制御部32は、算出された画像処理プログラム162の処理負荷がしきい値以上である場合、変動演算モジュール23に対応するタスクを演算コア110に割り当てる処理を中断する。負荷制御部32は、算出された画像処理プログラム162の処理負荷がしきい値以上でない場合、変動演算モジュール23に対応するタスクを演算コア110に割り当てる処理を続行する。

(もっと読む)

画像処理装置、撮像装置およびプログラム

【課題】 比較的簡易な構成でRAW画像のデータの色変換をより高い精度で行うための手段を提供する。

【解決手段】 画像処理装置は、RAW画像と、RAW画像を撮影した撮像装置の各色の画素の画素値と複数種類の色変換マトリクスとの対応関係を示した色再現特性情報とを取得する取得部と、所定の色空間を規定する1組の変数群から選択される2種類の変数を用いて、RAW画像の処理対象画素の画素値の座標と、複数の参照画素の画素値の座標とを共通の2次元平面に写像する写像処理部と、2次元平面での前記処理対象画素の画素値の座標と各々の参照画素の画素値の座標との位置関係から色再現特性情報のうちから選択された、複数の色変換マトリクスを演算して、RAW画像の色変換処理で適用する現像用色変換マトリクスを求めるマトリクス演算部と、を備える。

(もっと読む)

3次元コンピュータグラフィック用プロセッサ

【課題】 本発明は,複数のプログラムを1つのプロセッサで同時に処理することができる3次元コンピュータグラフィックに特化したプロセッサを提供することを目的とする。

【解決手段】 本発明のプロセッサの制御ユニット11は,n個のプロセスコントローラ21を含む。そして,本発明のプロセッサの実行ユニット13a〜13hは,n個のプロセスコントローラ21に対応したレジスタ領域を有する。よって,本発明は,複数のプログラムを1つのプロセッサで同時に処理することができる3次元コンピュータグラフィックに特化したプロセッサを提供することができる。

(もっと読む)

データ処理方法および画像データ処理方法ならびにデータ処理装置および画像データ処理装置

【課題】データ処理が高速化されたメディアン取得手法を提供する。

【解決手段】9個のデータのメディアンを得るデータ処理方法において、前記9個のデータを6個のデータのUnitAと3個のデータのUnitBに分け、各データの大小比較、UnitAからUnitBへの移動、UnitAおよびUnitBからのデータの除去の操作によりメディアンを得る。

(もっと読む)

画像データ出力装置、画像処理装置、および画像形成装置

【課題】互いに異なるサイズの画像データを用いた複数種類の画像処理を行う画像処理装置の回路規模を縮小する。

【解決手段】空間フィルタ処理部17に画像データを出力する場合には、各シフトレジスタSRn0〜SRn6およびこれら各シフトレジスタに備えられる各フリップフロップを選択し、選択した各フリップフロップに入力される画像データおよび選択した各シフトレジスタにおける最終段のフリップフロップから出力される画像データから画素データを抽出する。また、膨張処理を行う場合には、シフトレジスタSRn0〜SRn2を選択し、選択したシフトレジスタSRn0〜SRn2のうち入力側から3個目までのフリップフロップを選択し、選択した各フリップフロップに入力される画像データおよびシフトレジスタSRn0〜SRn2における入力側から3個目のフリップフロップから出力される画像データから画素データを抽出する。

(もっと読む)

画像生成システム、プログラム及び情報記憶媒体

【課題】複数の領域担当処理装置を有効活用して高品質な画像を生成できる画像生成システム、プログラム及び情報記憶媒体等の提供。

【解決手段】画像生成システムは、複数の領域担当処理装置の各領域担当処理装置が、仮想3次元空間を分割した複数の領域の各領域のオブジェクトの制御処理及び仮想カメラから見える各領域の画像の描画処理を行い、描画処理により得られた描画画像データを送信した場合に、描画画像データを受信する通信処理部と、受信した描画画像データに基づいて画像合成処理を行って、仮想カメラから見える表示画像を生成する画像合成部を含む。

(もっと読む)

地図表示装置及び地図表示プログラム、並びにこれを用いたナビゲーション装置

【課題】複数のプロセッサコアを効率的に使用して画像表示が完了するまでの処理時間を短縮させ、応答性に優れた地図表示装置及びナビゲーション装置を提供する。

【解決手段】情報の演算処理を行うプロセッサコアを複数有する地図表示装置であって、地図を構成する区画毎に表示範囲に含まれる割合である区画範囲割合を取得する区画範囲割合取得手段と、区画毎に地図情報を構成する区画情報を取得する区画情報取得手段と、複数のプロセッサコアを用いて区画情報を処理して表示範囲に含まれる区画毎の描画画像を生成する描画画像生成手段と、生成した区画毎の描画画像を組み合わせて生成される表示画像を表示する表示手段と、描画画像生成手段による描画画像の生成に際して、それぞれのプロセッサコアが演算処理を行う区画範囲割合の和である処理面積を均等とするように、区画情報をそれぞれのプロセッサコアに割り当てる処理面積調整手段と、を備える。

(もっと読む)

ウエハ用永続的データの作成と、永続的データを検査関連機能に使用するためのシステムと方法

【課題】

【解決手段】ウエハの永続的データを生成して検査関連機能に永続的データを使用する様々なシステムと方法を提供する。1つのシステムは検査システムの検出器に接続される一組のプロセッサノードを含む。各プロセッサノードはウエハの走査中に検出器によって生成された画像データの一部分を受信する。システムはまた、各プロセッサノードに別々に接続される記憶媒体のアレイを含む。プロセッサノードは、ウエハの走査中に検出器によって生成された画像データの全てまたは画像データの選択された部分が記憶媒体のアレイに記憶されるように、プロセッサノードによって受信された画像データの全てまたは選択された部分を記憶媒体のアレイに送るように構成される。

(もっと読む)

視覚装置

【課題】視覚装置における計算データを効率よく転送することを目的とする。

【解決手段】

第77図に示すように、本発明の視覚装置2の1実装形態では、配列演算ユニット100が備える2個以上のコントローラ103に対して0〜3の連続した番号が割り当てられ、さらに全ての配列演算ユニット100の各々における番号が割り当てられた全てのコントローラ103の各々が、隣接する上側の配列演算ユニット100の4個のコントローラ103のうち、番号が1つだけ小さいコントローラ103に計算データを送信できるように、複数の信号線が配線される。0番のコントローラ103が受信した計算データは破棄されるものとする。これにより、各々の配列演算ユニット100のプロセッサ101が複数のコントローラ103へアクセスする回数を低減する。

(もっと読む)

画像出力機器の色変換定義の作成方法、そのプログラム及び記録媒体、ならびに画像出力機器および画像処理装置

【課題】同じ出力結果を異なる照明光下で見た場合に、違和感なく見えるようにする。

【解決手段】画像出力機器の出力結果を観察するための異なる照明光を有する複数の観察環境下でのそれぞれの色の見えの違いが小さくなる照明光による観察環境を想定し、それぞれの色の見えの違いが小さくなる照明光による観察環境下での画像出力機器のデバイスカラーの測色値を求め、求めた画像出力機器のデバイスカラーの測色値から色変換定義を作成する。

(もっと読む)

ローカル・レジスタを有する処理要素のアレイ

【課題】 ローカル・レジスタを有する処理要素のアレイを提供すること。

【解決手段】 特殊化された画像処理回路が、通常、単一命令複数データ(SIMD)アーキテクチャとして超並列方式でハードウェア中に実装される。公知の実装形態は一般に、処理要素とメモリ・サブシステムとの間の接続パスが長く複雑であり、その結果、最大動作周波数が制限されるという難点がある。最適化された画像処理用アーキテクチャは、2次元構造に配列された処理要素(PE00,...,PE77)を有し、各処理要素は、複数の参照ピクセルを含むローカル・ストレージ(X0,...,X8)を有するが、参照ピクセルは参照画像中の近隣ではない。そうではなく、参照ピクセルは参照画像の異なるブロックに属し、これは種々の符号化方式で様々である場合がある。

(もっと読む)

データ処理装置及びそのプログラム

【課題】利用者にプログラムの設計の過度の負担を強いることなく、各種画像処理を行うべく複合機に搭載されるダイナミックリコンフィギュラブルプロセッサを高速に動作させること。

【解決手段】データ処理装置1のコントローラプロセッサ14は、ある連携状態のセルアレイによる画像処理の処理対象となっているバンド画像データの上、下、上下に隣接するバンド画像データについて前段の画像処理の実行結果が得られているか否か判断し、得られていない場合はその隣接するバンド画像データを先に実行してその実行結果が得られてから連携状態を遷移させる。

(もっと読む)

データ処理ハードウェア

本発明は、一般に、データ処理ハードウェアに関し、より詳細には、行列因数分解、特に非負行列因子分解(NMF)のためのハードウェアアクセラレータおよび関連の方法に関する。本発明の実装形態は、特に、OLEDディスプレイなどの電子発光ディスプレイの駆動に有用である。掛け合わせると対象の行列に近づく1対の因子行列(R;C)を決定する行列因子分解ハードウェアアクセラレータであって、前記対象の行列を表す入力データ行列を受信する入力と、第1の因子行列(R)の行および列のデータを格納する第1の因子行列メモリであって、ブロックに格納されている第1の因子行列の列データにアクセスするための、前記第1の因子行列メモリのそれぞれのブロックにそれぞれ関連付けられている複数の第1のデータバスを有する第1の因子行列メモリとを備える。  (もっと読む)

(もっと読む)

画像モーメントセンサ、画像モーメント計測装置、画像モーメントセンサの演算方法及び画像モーメント計測方法

【課題】画素回路の構成を簡易にする。

【解決手段】信号処理部3は、画像処理部1にクロック信号φ[0]を供給し、列選択信号xpi[0]〜xpi[N-1]を供給する。遅延回路(delay)11_1〜11_(N-2)は、クロック信号φ[0]を順次遅延させる。FIFO12_1〜12_(N-1)は、信号処理部3から供給された列選択信号xpi[0]〜xpi[N-1]を各処理要素13_xyに供給する。値“1”の列選択信号が供給された処理要素は、行方向に、入力画像の部分和を演算して、演算結果を列加算部2に供給する。信号処理部3は、この列加算部2に行選択信号yjを供給し、列加算部2は、供給された行選択信号yjに従って、加算演算を行い、信号SOUTを外部に出力する。

(もっと読む)

信号処理装置及び方法、並びにプログラム

【課題】 ハードウェアの規模を抑え、且つ、DPマッチングにおける評価値の計算を効率よく高速に行うことが可能な信号処理装置及びその方法、並びにプログラムを提供する。

【解決手段】 信号処理装置1は、第1及び第2の要素列の要素同士の対応関係を求める際に、第1の要素列を横軸、第2の要素列を縦軸として、左上端の要素と右下端の要素とを結ぶ対角線に平行な各列について、要素同士が対応する各対応点における評価値を、各列上の対応点を所定数毎に分割した対応点群毎に並列計算する。特に、評価値計算部14は、3つの評価値列記憶部の何れか2つから1列前及び2列前の対応点群についての評価値列を読み出して現在の対応点群についての評価値列を計算し、その評価値列を、同一列で隣接する対応点について得られた評価値と共に、上記1列前及び2列前の評価値列を読み出したものとは異なる評価値列記憶部内の同一アドレスに書き込む。

(もっと読む)

ストリームプロセッサ及び情報処理装置

【課題】アレイ型プロセッサの処理効率を向上させることができる、該アレイ型プロセッサを備えたストリームプロセッサ及び情報処理装置を提供する。

【解決手段】メモリに格納されたデータを読み出し、指定された処理を実行するストリームプロセッサであって、処理を実行するデータパス部、及び該データに対して実行する処理を指定するコマンドにしたがってデータパス部の状態を制御する状態管理部を備えたアレイ型プロセッサと、メモリから処理対象のデータ及び該データに対応するコマンドを含む情報をそれぞれ読み出し、該コマンドを状態管理部へ先に送信し、その後、処理対象のデータを前記データパス部へ送信する入力DMA回路とを有する構成とする。

(もっと読む)

画像解像度変換装置

【課題】解像度変換後の新規な画素に関わる元画像の画素群の選定を、回路規模を抑えつつ行うことが可能な画像解像度変換装置を提供すること。

【解決手段】複数の画素からなる元画像を、設定された解像度変換倍率を乗じた解像度を有する画像に変換する画像解像度変換装置であって、画素値記億部101と、領域決定部102と、画素値読み取り制御部103と、補間演算部104とを備える。画素値記億部は、前記元画像の各画素の画素値を格納する。領域決定部は、前記設定された解像度変換倍率に基づき、新規に画素を設ける領域を、前記新規画素のラスタ配列順に従って順次決定する。画素値読み取り制御部は、前記決定結果に応じて、前記領域に対応する画素群の画素値を前記画素値記億部から出力させる出力制御信号を生成する。補間演算部は、前記画素群の画素値から、前記設定された解像度変換倍率に対応する、前記新規の画素の画素値を補間演算する。

(もっと読む)

1 - 20 / 21

[ Back to top ]