Fターム[5B060CA04]の内容

Fターム[5B060CA04]の下位に属するFターム

パイプライン制御、オーバーラップ制御 (27)

アクセスの先行制御 (61)

Fターム[5B060CA04]に分類される特許

1 - 20 / 46

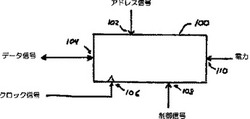

同期式バーストメモリ

【課題】本発明は、一般的にはランダムアクセスメモリ装置の方法、及び/又は、アーキテクチャに関し、より詳細には、バースト転送能力を持つ同期式ランダムアクセスメモリ装置に関する。

【解決手段】一般にメモリアレー及びバーストシーケンス発生器を備える装置。該メモリアレーは、データを記憶するように形成することができる。該バーストシーケンス発生器は、該装置によって受信されたアドレス情報に応答してバーストシーケンスを生成するように形成することができる。該バーストシーケンスは、該メモリアレーにデータを記憶するための複数の位置を識別するように形成することができる。該装置は、50ミリアンペアの最大作動電流、及び/又は、約25マイクロアンペアの最大待機電流を持つことができる。

(もっと読む)

画像メモリ制御装置および画像処理装置

【課題】バースト転送が可能な画像メモリを用いた場合に、成分数の多いカラー画像データに対しても成分数の少ないモノクロ画像データに対しても画像回転処理などを内部メモリの増加を抑えて効率よく実行できる画像メモリ制御装置を提供する。

【解決手段】CMYKAの5成分のカラー画像を順次入力するときは、成分別に8ラインずつの入力バッファを5個形成して8ライン分の画像データを一時保存した後、入力バッファから同一領域に対応する各成分の画像データを8×8画素単位のブロックで読み出し、これらのブロックを同一行アドレス内の連続する列アドレスにバースト転送で格納する。K,Aの2成分のモノクロ画像データを入力するときは、前記入力バッファを2個ずつ組み合わせて16ラインの入力バッファを2個形成し、ブロックサイズを16×16画素に拡張して同様の処理を行う。

(もっと読む)

メモリ装置、メモリ制御回路及びメモリ制御システム

【課題】画像データの矩形アクセスを効率的に行うメモリ装置、メモリ制御回路及びメモリ制御システムを提供すること。

【解決手段】メモリ装置は、Mビットのデータ入出力バスを備え入力クロックに同期してバンクアドレスとロウアドレスとコラムアドレスに対応した記憶セルに対してデータの読み書きを行い、入力クロックの1サイクル毎に2つのアクセス入力と読み出しバースト長フラグを受信し、第1の制御アクセスコマンドと第2の制御アクセスコマンドと読み出しバースト長信号とを出力する。制御アクセスコマンドが読み出し要求の場合に、読み出しバースト長信号で指定されたバースト長で指定する期間に、記憶セルからのデータ読み出し後にデータ入出力バスに読み出しデータを出力する。2バースト長の場合は、制御アクセスコマンドそれぞれに対応する記憶セルからの2つのMビットの読み出しデータを2サイクルの期間データ入出力バスに出力する。

(もっと読む)

マイクロコンピュータ及びデータ処理システム

【課題】マイクロコンピュータにおいてメモリアクセスコマンドの生成などの点でシリアルアクセスメモリに対するアクセスのオーバーヘッドを減らす。

【解決手段】 CPUが出力するアクセス要求に含まれるアドレス及びコマンドに基づいて、シリアルフラッシュメモリに、チップ選択信号及びクロック信号を供給し、前記クロック信号に同期してメモリアドレス及びメモリコマンドを出力してシリアルアクセスメモリのアクセス制御を行うシリアルメモリインタフェースコントローラ(60)をマイクロコンピュータに搭載し、このシリアルメモリインタフェースコントローラには、前記アクセス要求に応答するメモリアドレス及びメモリコマンドに基づくデータリードを完了したとき、そのリードデータの最後のメモリアドレスに続くアドレスへのリードアクセス要求以外のアクセス要求を検出するまで前記チップ選択信号の活性状態を維持する動作モードを採用する。

(もっと読む)

SIMDプロセッサのためのメモリコントローラ

【課題】外部メモリ上のデータの並列度が低い場合であってもSIMDプロセッサによるSIMD演算の効率を向上させ、高速なデータ処理を実現する。

【解決手段】メモリコントローラ20は、DDRメモリ30におけるアドレスを格納するアドレスメモリ22と、各アドレスからデータが連続して格納される長さをそれぞれ表すバースト長を格納するバースト長メモリ23とを備える。メモリコントローラ20は、第1のグループのプロセッサエレメントと、アドレスメモリ及びバースト長メモリに格納された第1のアドレス及び対応する第1のバースト長によって特定されるDDRメモリ30の領域との間で、第1のデータを転送し、第1のデータの転送後、第2のグループのプロセッサエレメントと、アドレスメモリ及びバースト長メモリに格納された第2のアドレス及び対応する第2のバースト長によって特定されるDDRメモリ30の領域との間で、第2のデータを転送する。

(もっと読む)

半導体装置及び制御方法

【課題】メモリの出力バッファの平均電流値を低減し、消費電流を抑制すること。

【解決手段】本発明に係る半導体装置は、メモリリードアドレスDの連続性を判定し、判定結果Hを出力するアドレス連続性判定回路23と、判定結果Hに基づいて、メモリリードアドレスDに対応するリードデータを出力するメモリの出力バッファ22の駆動能力を制御する駆動能力切り替え制御回路24と、CPUの要求リードアドレスAに対応するリードデータが当該CPUへ到達するまでの期間に、CPU要求リードアドレスAに連続する予想アドレスを生成するアドレス生成部12と、予想アドレスに対応するリードデータを格納するプリロードバッファ14を備える。

(もっと読む)

メモリー制御装置、メモリー制御システム、記録装置及びメモリー制御方法

【課題】ダイナミックRAMにアクセスする際のレイテンシーを改善することができるメモリー制御装置、メモリー制御システム、記録装置及びメモリー制御方法を提供する。

【解決手段】複数のマスターM1〜MnとDRAMとの間に介在するメモリーコントローラー37は、メモリーシーケンス制御回路64とレイテンシー改善回路67等を備える。レイテンシー改善回路67は、マスター数判定回路71と、ページヒット率判定回路72と、ページ制御回路73とを備える。マスター数判定回路71は特定時間におけるアクセスマスター数が有効バンク数(例えば「8」)以下であるか否かを判定し、ページヒット率判定回路72はページヒット率が設定値Q(本例では50%)以上であるか否かを判定する。ページ制御回路73は両条件成立時にページオープン制御信号Sopenを出力し、一方の条件でも不成立であるとページクローズ制御信号Scloseを出力する。

(もっと読む)

メモリアクセスシステムおよびメモリアクセス制御方法

【課題】アクセス効率の高いメモリアクセスシステムを提供することである。

【解決手段】本発明にかかるメモリアクセスシステムは、第1乃至第4のメモリ10、20、30、40と、メモリコントローラ1とを備える。メモリコントローラ1は、第1のチップセレクト信号(CS0)を活性化する第1のタイミングにおいて、互いに異なる第1および第2の固有アドレス(ADA、ADB)を供給することで、第1および第2のメモリ10、20に格納された第1のブロック群のブロックにアクセスする。また、第2のチップセレクト信号(CS1)を活性化する第2のタイミングにおいて、互いに異なる第1および第2の固有アドレス(ADA、ADB)を供給することで、第3および第4のメモリ30、40に格納された第2のブロック群のブロックにアクセスする。

(もっと読む)

データアクセス制御装置およびデータアクセス制御方法

【課題】優先度の異なる複数のモジュールを備えるシステム構成において、優先度の高いモジュールのデータ転送を確実に行うことができるようにする。

【解決手段】メモリ制御部により、高速モジュール1の設定に従い、該高速モジュール1に対して複数バンクA〜Dへのアクセス要求を、該高速モジュール1に対する連続したアクセス要求の処理後に低速モジュール2に対するバンクへのアクセス要求を行うようにした。この際、高速モジュール1が、アクセスする先頭アドレスを低速モジュール2とは異なるバンクにアクセスするアドレス位置に設定するようにした。

(もっと読む)

情報処理システム及びデータ転送方法

【課題】初期アクセスレイテンシによるデータ処理速度の低下を低減するとともに無駄なメモリアクセスの発生しない情報処理システムを提供する。

【解決手段】情報処理システムは、連続する複数回のデータ読み出し命令を出力する際に転送状態信号を合わせて出力し、ある1つのデータ読み出し命令に対して少なくとも1つのデータ読み出し命令が後続することを転送状態信号により示すマスタモジュールと、上記ある1つのデータ読み出し命令と転送状態信号とをマスタモジュールから受信すると、転送状態信号に応答して、上記ある1つのデータ読み出し命令に後続する少なくとも1つのデータ読み出し命令に対応するデータをメモリから読み出して保持するとともに、上記ある1つのデータ読み出し命令に対応するデータをマスタモジュールに供給するメモリコントローラを含むことを特徴とする。

(もっと読む)

シンクロナスDRAMアクセス装置

【課題】 シンクロナスDRAMに対して、転送語数が複数であるデータや転送語数が1であるデータを切り替えて転送する場合に、効率的にデータ転送を行うための制御を簡単な回路で実現する。

【解決手段】 転送語数が2以上の場合、第1の制御器4を起動し、アクティブ、リード/ライト、プリチャージの順番にコマンドを出力する。転送語数が1の場合、第2の制御器5を起動し、アクティブ、リード/ライトの順にコマンドを出力し、次の転送要求を待つ。次の転送要求のデータ転送語数が1であれば、第2の制御器5はリード/ライトコマンドを出力し、再び転送要求を待つ。次の転送要求のデータ転送語数が2以上であればプリチャージコマンドを出力して第1の制御器4を起動し、バースト転送を行う。これにより、データ転送語数が1の場合の転送の際、不必要なアクティブコマンドやプリチャージコマンドを出力しないので、データ転送効率が改善された。

(もっと読む)

メモリアクセス判定回路、メモリアクセス判定方法および電子機器

【課題】キャッシュメモリのヒット率を向上させ、処理を高速化すること。

【解決手段】第1の変化値に基づいて値をカウントするカウンタ1と、カウンタ1の出力に対応するアドレスに基づいて、キャッシュメモリ6におけるキャッシュ判定をする制御部2と、を有する。制御部2がキャッシュミスであると判定した場合に、カウンタ1は、第1の変化値mを第1の変化値mと異なる第2の変化値nに切り替えてカウントする。制御部2、第2の変化値nに基づくカウント値に基づいてキャッシュ判定をする。

(もっと読む)

メモリアクセス装置

【課題】複数のマスターからのリード要求を同時にさばくと共に、メモリリードアクセスの頻度が高いマスターに対してより効率的にデータを返す。

【解決手段】優先順位の高い1個の第1マスター及びこれより優先順位の低い少なくとも2個の第2マスターからのメモリリード要求を受けるアービターのアービトレーション結果に基づいてメモリにアクセスする装置において、前記メモリに対するブロックリード要求並びに前記第1マスターまたは前記第2マスターからのメモリリード要求がある場合に、第1優先順位に設定された前記第1マスターからのメモリリード要求、若しくは、この第1マスターがアクセスする前記メモリのバンクとは異なるバンク対して前記第2マスターからのメモリリード要求があるときに、前記第1マスターのメモリリード要求と同時に、この第1マスターがアクセスするバンクと同一バンクの別データにアクセス可能な、先行リード指令を発行する。

(もっと読む)

ハブベースのシステムメモリにおける書込みコマンドを終了させる方法とシステム

【課題】ハブベースのシステムメモリにおける書込みコマンドを終了する方法とシステムが開示されている。

【解決手段】メモリハブはダウンストリームメモリコマンドを受け取り、受け取った各ダウンストリームメモリコマンドを処理して、そのメモリコマンドがメモリハブに向けられた書込みコマンドを含んでいるかどうかを決定する。メモリハブは、書込みコマンドがハブに向けられているときは、メモリデバイスに適用するように適応されたメモリアクセス信号を発生するように第1モードで動作する。メモリハブは、書込みコマンドがハブに向けられていないときは、ダウンストリームメモリハブに結合されるように適応されたダウンストリーム出力ポート上にコマンドの書込みデータを提供するように第2モードで動作する。

(もっと読む)

プログラムを実行する方法およびシステム

【課題】ブート・コードのサイズがランダムアクセス可能なバッファの記憶容量を超える場合でもCPUが直接読み込んで実行可能とする。

【解決手段】NAND型フラッシュ・メモリ100のストレージ部110から、このフラッシュ・メモリ100に設けられCPU200からランダムアクセス可能なバッファ部120に、コードB0を読み込む。そして、バッファ部120に読み込まれたコードB0を実行することにより、コードB1をキャッシュ・メモリ210に保持する。そして、キャッシュされたコードB1を実行することにより、ブート・コードであるコードAPPをストレージ部110からバッファ部120に読み込み、ベース・アドレスを変更してキャッシュ・メモリに保持する。そして、コードB1からコードAPPにジャンプし、キャッシュされたコードAPPを順次実行する。

(もっと読む)

インターフェース回路

【課題】シリアルフラッシュメモリに対するデータアクセスを可及的に高速に行うことが可能なインターフェース回路を提供する。

【解決手段】プログラムを実行するCPUコアの要求に基づいて、前記プログラムを格納するシリアルフラッシュメモリにアクセスするインターフェース回路であって、

前記CPUコアから出力されたリード信号及びアドレス信号に基づいて、前記シリアルフラッシュメモリに発行するためのリードコマンド及びアドレスセットを生成する、自動コマンド生成回路と、

前記リードコマンド及びアドレスセットを前記シリアルフラッシュメモリに発行する、制御部と、

前記リードコマンド及びアドレスセットに応じて前記シリアルフラッシュメモリから読み出されたデータを格納する、ワードレジスタと、

を備え、

前記制御部は、さらに、前記シリアルフラッシュメモリから読み出され前記ワードレジスタに格納されたデータを、前記CPUコアに出力するものとして構成されている。

(もっと読む)

メモリ制御回路、電子機器制御装置、および、複合機

【課題】簡易な方法で、メモリへのアクセス効率を向上させる技術を提供する。

【解決手段】本出願のメモリコントローラ123は、SDRAM113を制御するメモリコントローラであって、マスタからSDRAM123内のページへのアクセス要求を受け付ける受付手段と、各マスタのアクセス要求周期を記録する記録手段と、受け付けたアクセス要求を出したマスタに応じて、記録手段に記録されたアクセス要求周期に基づくページのオープン期間を設定し、設定されたオープン期間の間、アクセス要求がされたページをオープンにする処理を行うページオープン手段と、を備える。

(もっと読む)

メモリアクセスシステム、メモリ制御装置、メモリ制御方法、および、プログラム

【課題】複数のデータ処理装置(バスマスタ)から1つの記憶装置にアクセス要求が発行されてバスが競合するメモリアクセスシステムにおけるアクセス効率を改善する。

【解決手段】メモリ制御装置におけるアクセス要求受付手段22は、DRAM10の連続したアドレスに配置されているデータに対する連続する複数のアクセス要求、または、DRAM10の不連続なアドレスに配置されているデータに対する連続する複数のアクセス要求を、連続した複数のアクセス要求として受け付ける。アクセス要求並べ替え手段24は、アクセス要求受付手段22が受け付けた連続するアクセス要求について、1つのデータ処理装置から出力された、データの書込み要求、または、データの読み出し要求のいずれか一方の連続したアクセス要求の範囲内でDRAM10のバンク順に連続したアクセス要求を並べ替えてDRAM10のアクセスを制御する。

(もっと読む)

半導体メモリコントローラおよび半導体メモリシステム

【課題】書き込み速度の速い半導体メモリコントローラ2、および半導体メモリシステム1を提供する。

【解決手段】1個のメモリセルに2ビットデータを記憶可能な多数のメモリセルから構成されている2つのチップ21、22からなる半導体メモリ部20に、メモリインターリーブ方式によりデータを書き込むプログラムを制御する、半導体メモリコントローラ2において、書き込みプログラムが、プログラム時間の異なるUpperページ書き込みプログラムとLowerページ書き込みプログラムから構成されており、一のチップのUpperページおよびLowerページ書き込みプログラムの実行の後に、他のチップのUpperページおよびLowerページ書き込みプログラムを実行する。

(もっと読む)

メモリ制御装置

【課題】行アドレスの変更が必要な連続した複数のデータを繰り返して読み出す場合であっても、短時間でそのデータを読出すことができるようにする。

【解決手段】繰返リード制御部5の繰返リード回数レジスタに格納された回数およびリードアドレス領域レジスタに格納されたSDRAM2のアドレスに基づいてSDRAM2に格納された連続する複数のデータを繰り返して読み出すとき、1回目にSDRAM2から読み出した連続する複数のデータをプリチャージが不要なデータバッファ4に記憶させ、2回目以降に読み出すときはそのデータバッファ4から連続する複数のデータを読み出すようにした。

(もっと読む)

1 - 20 / 46

[ Back to top ]