Fターム[5B060KA04]の内容

Fターム[5B060KA04]の下位に属するFターム

複数のバンクから構成されるもの (28)

Fターム[5B060KA04]に分類される特許

1 - 20 / 163

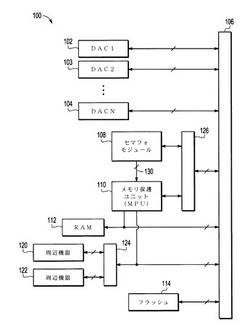

共有システムリソースのセマフォベースの保護のためのシステムおよび方法

【課題】共有システムリソースのセマフォベースの保護のためのシステムおよび方法を提供する。

【解決手段】データアクセス構成要素は、各々が共有システムリソースに対するアクセスを要求するアクセス要求を発行するように構成される。データアクセス構成要素は、前記共有システムリソースに領域記述子が関連付けられる。セマフォモジュールは、前記共有システムリソースについてのセマフォを実装するように、および、前記複数のデータアクセス構成要素のいずれかが前記共有システムリソースについての前記セマフォをロックした場合、いずれのデータアクセス構成要素が前記共有システムリソースについての前記セマフォをロックしたかを示すセマフォ信号を生成するように構成される。メモリ保護ユニットは、前記セマフォ信号および前記領域記述子に基づいて前記アクセス要求を認可または拒否するように構成される。

(もっと読む)

セマフォ予約をクリアする方法および装置

【課題】共有メモリへの排他的アクセスのためにセマフォ予約をクリアする方法を提供する。

【解決手段】セマフォ116の動作は、複数の処理要素によって共有されるメモリ114への排他的アクセスを管理する。処理要素による排他的アクセスのためのセマフォ予約状態は、メモリ制御装置によって監視される。古い予約状態をクリアするために、コマンド信号が、メモリへの書き込み動作のために送信され、一方でメモリの内容を更新するのを妨げる。制御装置104の予約状態は、コマンド信号の受信に応答して、予約状態から非予約状態に変更される。

(もっと読む)

動的ポート優先割当能力を有しているメモリコントローラー

【課題】動的ポート優先割当能力を有しているメモリコントローラーを提供すること。

【解決手段】メモリにアクセスするように動作可能な集積回路であって、該集積回路は、メモリアクセスリクエストを生成するように動作可能なプログラマブルマスター回路と、メモリコントローラーであって、該メモリコントローラーは、該メモリアクセスリクエストを該プログラマブルマスター回路から第1および第2のポートにおいて受信するように動作可能であり、該メモリーコントローラーは、該メモリアクセスリクエストを実行するために、該メモリにアクセスするように動作可能であり、該メモリコントローラーは、該メモリアクセスリクエストを順番に実行するように動作可能である、メモリコントローラーと、該メモリコントローラーが該メモリアクセスリクエストを実行する順番を制御するように動作可能である制御回路とを含む、集積回路。

(もっと読む)

情報処理システム、調停方法

【課題】精度の良い調停を行うことができる情報処理システム、及び調停方法を提供する。

【解決手段】イニシエータIP1−1は、ターゲットIP5に対し、一定処理を行うために必要なデータ転送に応じて複数のアクセスリクエストを順次生成して発行する。算出装置2−1は、データ転送の総データ量と、予め設定された転送許容時間と、から第1の転送レートを算出する。算出装置2−1は、所定の設定タイミング毎に、イニシエータIP1−1に転送済みのデータ量と、イニシエータIP1−1がデータ転送を開始してからの経過時間と、から第2の転送レートを算出する。算出装置2−1は、第1の転送レートと、第2の転送レートと、の比較結果に基づいて、イニシエータIP1−1が発行前のアクセスリクエストに対応付ける重みづけを設定する。調停回路4は、アクセスリクエストに対応付けられた重みづけに基づいて、転送処理の調停を行う。

(もっと読む)

マルチプロセッサシステム、メモリ管理方法、および、メモリ管理プログラム

【課題】システム全体として、メモリアクセスのレイテンシを小さくすることのできるマルチプロセッサシステムを提供する。

【解決手段】あるプロセッサ8が別のノードのメインメモリ9にアクセスしたのをトリガとして、プロセッサ8がアクセスしたデータをそのメインメモリ9から取得して、アクセスしたプロセッサ8と対になったメインメモリ9に移動するアクセスデータ移動手段と、アクセスデータを格納するメインメモリ9から一部データを廃棄してアクセスデータを格納するための容量を確保する格納容量確保手段と、廃棄したデータを替わりに格納するためのメインメモリ9を複数のメインメモリ9の中から選択する格納メモリ選択手段と、選択したメインメモリに廃棄したデータを格納する廃棄データ格納手段を有するメモリ管理機構10をプロセッサ8とメインメモリ9の間に設置する。

(もっと読む)

メディアメモリシステム

【課題】親プロセッサアドレス変換をメディアプロセッサのアドレス変換に整合させ、複数のメディアプロセッサに別々の変換テーブル情報によって同時共有メモリアクセスを与えるための方法および装置を提供する。

【解決手段】所定メディアアプリケーションに対するページディレクトリは、メディアアプリケーションが親プロセッサおよびメディアプロセッサ上で実行されるメディアアプリケーションによって共有されるべきメモリを割り当てる場合にメディアプロセッサのページディレクトリにコピーされる。

(もっと読む)

アクセス管理装置、情報処理装置、アクセス管理方法

【課題】複数のプロセッサが共有リソースにアクセスする際の調停頻度を、キャッシュやバッファを抑制するアクセス管理装置、情報処理装置及びアクセス管理方法を提供すること。

【解決手段】複数のプロセッサ11から要求された共通のリソース16へのアクセス要求を制御するアクセス管理装置100であって、複数のプロセッサ11から受け付けたリードアクセスの複数のアドレスを比較するアドレス比較手段13と、複数のアドレスのうち一致したアドレスのデータをリソース16からリードするデータリード手段14と、データリード手段14がリードしたデータを、一致した複数のアドレスを出力した複数のプロセッサ11に同じタイミングで出力するデータ出力手段15と、を有することを特徴とする。

(もっと読む)

アクセスレイテンシを低減するバスアービトレーション技法

メモリー制御装置、メモリー制御システム、記録装置及びメモリー制御方法

【課題】ダイナミックRAMにアクセスする際のレイテンシーを改善することができるメモリー制御装置、メモリー制御システム、記録装置及びメモリー制御方法を提供する。

【解決手段】複数のマスターM1〜MnとDRAMとの間に介在するメモリーコントローラー37は、メモリーシーケンス制御回路64とレイテンシー改善回路67等を備える。レイテンシー改善回路67は、マスター数判定回路71と、ページヒット率判定回路72と、ページ制御回路73とを備える。マスター数判定回路71は特定時間におけるアクセスマスター数が有効バンク数(例えば「8」)以下であるか否かを判定し、ページヒット率判定回路72はページヒット率が設定値Q(本例では50%)以上であるか否かを判定する。ページ制御回路73は両条件成立時にページオープン制御信号Sopenを出力し、一方の条件でも不成立であるとページクローズ制御信号Scloseを出力する。

(もっと読む)

データ転送装置、データ転送方法、データ転送プログラム及び記録媒体

【課題】優先順位の異なる複数のDMACからのメモリへのアクセス要求を優先順を変更して適切に調停するデータ転送装置、データ転送方法、データ転送プログラム及び記録媒体を提供する。

【解決手段】ライン同期信号LSYNCと画像先端同期信号FSYNCに基づいて1ライン分の画像データをメモリから読み取って転送するRDMAC134を含む複数のDMAC123、124からのメモリへのリクエストを予め設定されている優先順位に基づいてリクエスト調停部112が調停する場合、画像処理部11の転送データ量監視部136が2つのラインバッファ132がフル状態か否か監視して、該監視結果に基づいて必要転送量計算部105が、上記優先順位の変更の要否を判定し、優先順位制御部111が該判定結果に基づいてリクエスト調停部112の優先順位を制御する。

(もっと読む)

マルチプロセッサシステムおよびマルチプロセッサシステムのプログラム

【課題】 マルチプロセッサシステムの計算処理の効率を向上させる。

【解決手段】 マルチプロセッサシステムは、第1メモリと、第1メモリに接続され、第1メモリに記憶されたデータを用いて処理を実施する処理部とを有している。処理部は、第2メモリと、データおよび処理の結果である処理データの少なくとも一方を第1メモリと第2メモリとの間で転送するデータ転送を実施する第1プロセッサと、第1メモリと第2メモリとの間でのデータ転送と処理とを切り替え可能に実施する第2プロセッサと、第2メモリに転送されたデータを用いて、処理を実施する第3プロセッサとを有している。

(もっと読む)

コンピュータシステム及びその制御方法

【課題】システムマネージメント機能を高速に実行可能なコンピュータシステム及びその制御方法を提供する。

【解決手段】本発明に係るコンピュータシステムは、プロセッサコア11〜18のうちプロセッサコア11についてマネージメントモードであるか否かが設定され、プロセッサコア11は、マネージメントモードであると設定された場合には、マネージメント用プロセッサとしてマネージメントファームウェアを実行し、マネージメントモードではないと設定された場合には、他のプロセッサコアと同様にシステムのプロセッサの一部として動作を行う。また、メインプロセッサ10のメインメモリコントローラ19は、メインメモリ40の領域のうち指定された一部のメモリ領域を、マネージメントモードであると設定されたプロセッサコア11からのみアクセス可能な領域として設定する。

(もっと読む)

調停装置

【課題】高速な連続データ転送を行うデータ転送回路にバスの使用権を優先的に付与し、データの転送時間を短縮する。

【解決手段】複数のデータ転送回路2からの要求に応じてSDRAM1のバス使用権の調停を行う調停装置3において、一のデータ転送回路2から転送要求信号211とともに連続要求信号212を入力したとき、該転送要求信号211に応じたデータ転送が終了した後、他のデータ転送回路2に優先して前記一のデータ転送回路2にバス使用権を継続して付与する。

(もっと読む)

計算機システム

【課題】 高密度実装するサーバモジュールのメモリ容量の増設を容易にする。

【解決方法】 メモリ容量を追加するためのメモリ増設モジュールをサーバシステムに備えることにより、サーバブレードのCPUには通常のメモリと認識可能な外部メモリの増設手段を持ち、複数のサーバブレードで1つのモジュールを共有することにより、複数のサーバブレードのメモリ容量を増設が可能なサーバシステム。

(もっと読む)

データ転送システム

【課題】1つのメモリコントローラに対して複数のコントロールマスタを設けたデータ転送システムにおいて、リードコマンドに対する処理効率を向上させる。

【解決手段】メモリコントローラを介して接続された複数のコントロールマスタとメモリとの間でデータリード処理を行なうデータ転送システムであって、メモリコントローラは、リードコマンドを受け付けると、そのリードコマンドに係るコントロールマスタの識別子をFIFO形式で格納するルートセレクタと、メモリから読み出したリードデータをFIFO形式で格納するリードデータバッファとを備え、コントロールマスタは、ルートセレクタに格納されている識別子のうち、最先に格納された識別子が自身の識別子であって、リードデータバッファにリードデータが格納されている場合に、リードデータバッファからリードデータを読み出す。

(もっと読む)

データフロー及びプロセッサのメモリ共有化ための装置、方法及びプログラム

【課題】情報装置のデータフローのためのバッファとプロセッサのためのメインメモリとを共有化させるためのメモリアクセス装置を提供する。

【解決手段】アービタ手段は、複数の機能ブロックからのメモリのアクセス要求を順にラウンドロビン方式で所定の転送長で割当て、(a)所定の転送長で部分転送に分割し、データ転送の帯域に応じて1回のラウンドロビン・サイクルの中で複数の部分転送をし、(b)複数の部分転送は異なる優先度を有し、異なる機能ブロックからの部分転送の交互の転送により全ての機能ブロックからのデータ転送の必要帯域を満たすように優先度をプログラマブルに設定し、(c)プロセッサからのメモリへのアクセス回数が、最優先で所定の転送長(CPU転送長)で部分転送間の所定の間隔において、機能ブロックからのデータフローの転送帯域への影響が小さくなるように、プロセッサ・アクセスを行う。

(もっと読む)

情報処理システム

【課題】メモリ装置をアクセスする複数のマスタに対して、必要なデータを円滑に転送する。

【解決手段】情報処理システムは、メモリ装置(MEM0)と、上記メモリの動作を制御可能なメモリ制御装置(SL0)と、それぞれ上記メモリ制御装置を介して上記メモリ装置へアクセス可能な複数のバスマスタ(MS0〜MS3)とを含む。上記メモリ制御装置は、上記バスマスタからのアクセス要求を保持可能なバッファを含み、上記バッファの利用権を上記バスマスタ毎に設定可能である。

(もっと読む)

メモリシステム

【課題】リアルタイム性の要求が高い機能ブロックのリアルタイム性を確保するとともに、リアルタイム性の要求が低い機能ブロックの性能を低下しないようにする。

【解決手段】バスマスタとして動作し、所定の処理を行う複数の機能ブロックと、メモリコントローラと、前記複数の機能ブロックと前記メモリコントローラとを接続するバスとにより構成されるメモリシステムであって、前記機能ブロックは、メモリアクセスを発行する時に前記メモリアクセスが終了する時間情報を付加し、前記バスは、メモリアクセス情報に前記メモリアクセスが終了する時間情報を付加して転送する。さらに、前記メモリコントローラは、複数のメモリアクセスを保持し、前記バスマスタより受信したメモリアクセスが終了する時間情報に基づき、前記保持されたメモリアクセスの発行順序を制御する。

(もっと読む)

メモリアクセス処理装置及び方法

【課題】メモリアクセス装置の各ポートのキャッシュ装置とメモリとの間で、各ポートの命令のリクエストの調停を行うメモリアクセス処理装置で、調停が混雑している場合に、メモリアクセスを最適化して、メモリアクセス効率を向上できるようにする。

【解決手段】調停制御部4は混雑判定部8を有し、混雑判定部8により調停の混雑が判定される。命令発行制御装置3a〜3dでは、調停が混雑している場合には、ストア命令をバッファに退避させ、ロード命令がストア命令を追い越すように制御している。このように、調停が混雑している場合には、ロード命令をストア命令に優先させるように、命令のリクエストの出力順を変更することで、メモリアクセスの最適化を図ることができる。

(もっと読む)

プロセッサシステム及びその制御方法

【課題】 マルチCPUのプロセッサシステムにおいても適用可能な、メモリコントローラの消費電力を抑制する技術を提供する。

【解決手段】 外部メモリに接続されたプロセッサシステムは、メインプロセッサと、内部メモリ及び通信インタフェースを備えた通信プロセッサと、メインプロセッサ及び通信プロセッサが共通にアクセス可能な、外部メモリの使用の可否を制御するメモリ制御手段と、を備える。ここで、メモリ制御手段は、メインプロセッサと通信プロセッサとのいずれからもアクセスがない場合は省電力状態をとり、通信プロセッサの通信インタフェースを用いる処理が内部メモリの使用だけでは実行できない場合に、起動状態となり、通信プロセッサによる外部メモリの使用を可能にする。

(もっと読む)

1 - 20 / 163

[ Back to top ]