Fターム[5B060MM11]の内容

メモリシステム (7,345) | メモリモジュール構成、管理技術 (856) | メモリモジュールに対するアドレス設定 (55)

Fターム[5B060MM11]の下位に属するFターム

アドレスデコーダ等に設定するもの (11)

設定アドレスの変更 (23)

Fターム[5B060MM11]に分類される特許

1 - 20 / 21

複数の記憶装置を備えるシステム及びそのためのデータ転送方法

【課題】複数の記憶装置を備えるシステムにおいて正確かつ高速にデータ転送を行うこと、及び、データ転送時の消費電流を低減すること。

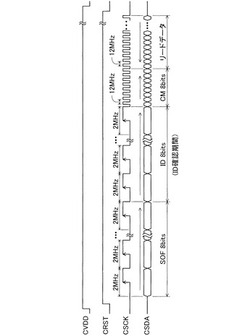

【解決手段】複数の記憶装置は、制御部に接続された1本のクロック信号線と1本のデータ信号線とにそれぞれバス接続される。複数の記憶装置のうちの各記憶装置は、他の記憶装置と識別するための識別情報を予め格納している。制御部は、

(i)複数の記憶装置のうちの1つの記憶装置の識別情報を、データ信号線を介して複数の記憶装置に送信して1つの記憶装置を選択する識別情報送信期間と、

(ii)選択された1つの記憶装置との間でデータ転送を実行するデータ転送期間と、を利用してデータ転送処理を行う。また、制御部は、識別情報送信期間におけるクロック信号の周波数を、データ転送期間におけるクロック信号の周波数よりも低く設定する。

(もっと読む)

半導体記憶装置及びこれを備える情報処理システム

【課題】複数のコアチップとインターフェースチップからなる半導体記憶装置において、I/O構成の切り替えを容易とする。

【解決手段】互いに異なるチップ識別情報LIDが割り当てられた複数のコアチップCC0〜CC7と、コアチップCC0〜CC7を制御するインターフェースチップIFとを備える。インターフェースチップIFは、外部との間で同時に入出力する単位外部データのビット数が可変であり、チップ識別情報LIDと比較するためのチップ選択情報SELを、単位外部データのビット数に応じて可変とする。これにより、I/O構成の変更に伴うページ構成の切り替えを不要とすることが可能となる。

(もっと読む)

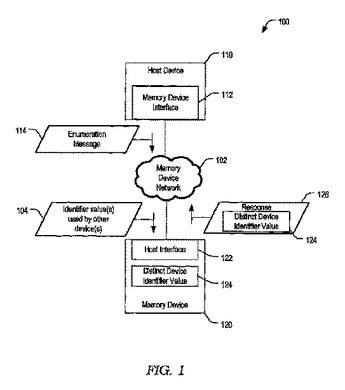

デバイス識別子選択

デバイス識別子を選択するシステムおよび方法が開示される。1つの特定の実施形態では、1つの方法は、ホストデバイスおよび1つ以上の他のデバイスに動作可能に結合されるデバイスのホストインターフェイスを介して計数メッセージを受け取ることと、ホストデバイスにより発せられたコマンドまたは他のデバイスのうちの1つからの応答メッセージであると、計数メッセージを識別することとを含む。この方法は、計数メッセージをコマンドであると識別したことに応答して、計数応答メッセージをホストデバイスに選択的に送ることを含む。計数応答メッセージは特有デバイス識別子値を示す。この方法は、計数メッセージを他のデバイスのうちの1つからの応答メッセージであると識別したことに応答して、そのような他のデバイスにより使用されている識別子値を応答メッセージから読み出し、かつデバイスが特有デバイス識別子値を選択できるようにこの識別子値をデバイスに少なくとも一時的に記憶することをも含む。  (もっと読む)

(もっと読む)

デバイス識別子選択

デバイス識別子を選択するシステムおよび方法が開示される。1つの特定の実施形態において、1つの方法は、第1のポート、第2のポート、および第3のポートを含む複数のポートを有するハブデバイスにおいて、ホストデバイスから第1のメッセージを受け取ることを含む。第1のメッセージはブロードキャストインジケータを含む。この方法は、第1のメッセージが計数を要求していると判定したことに応答して、計数インジケータを含むメッセージを第1のポートを介して第1のデバイスに、また第2のポートを介して第2のデバイスに、逐次伝播させることによってリング通信トポロジーをエミュレートすることをも含む。この方法は、第1のメッセージが計数を要求していないと判定したことに応答して、第1のメッセージを第2のデバイスに送るのと実質的に同時に第1のメッセージを第1のデバイスに選択的に送ることをさらに含む。リング通信トポロジーをエミュレートすることにより、ハブデバイスは第1のデバイスの第1の特有識別子値および第2のデバイスの第2の特有識別子値をホストデバイスに提供することができる。  (もっと読む)

(もっと読む)

積層装置識別割り当て

いくつかの実施形態は、スタック内に配列されるダイを有する装置および方法を含む。ダイは、少なくとも第1のダイおよび第2のダイ、ならびにそのダイに結合される接続部を含む。接続部は、第1の識別の第1のダイへの割り当ての間に第1のダイに制御情報を転送し、第2の識別の第2のダイへの割り当ての間に第1のダイから第2のダイに制御情報を転送するように構成されてよい。 (もっと読む)

メモリモジュール、および、メモリ用補助モジュール

【課題】メモリモジュールにおいて、メモリコントローラから出力されるバンクアドレスのビット数と、ロウアドレスのビット数と、カラムアドレスのビット数とが、それぞれ、アクセス対象となるメモリセルを特定するためのバンクアドレスのビット数と、ロウアドレスのビット数と、カラムアドレスのビット数と整合していない場合でも、メモリモジュールのすべてのメモリセルにアクセス可能にするとともに、メモリモジュールを正常に動作させる。

【解決手段】メモリモジュール100は、SDRAM110と、アドレス生成回路120とを備える。アドレス生成回路120は、メモリコントローラ12から出力されたロウアドレスの最上位ビットを用いて、アクセス対象となるメモリセルを特定するために不足する最上位ビットのバンクアドレスB2を生成し、生成されたバンクアドレスB2をSDRAM110に出力する。

(もっと読む)

データ複写装置及びデータ複写方法

【課題】コストを削減しつつ、確実、適切に新旧両基板の不揮発性メモリのアドレスを決定し、接続間違い状態等、データの複写状況を通知して効率的な基板交換作業を可能とする。

【解決手段】複写元から複写先の不揮発性メモリにデータの複写を行うためのデータ複写装置1であって、不揮発性メモリが設けられた複写元基板4aと、不揮発性メモリが設けられた複写先基板4zと、複写先基板4zと複写元基板4aに接続し、データ複写状況を通知する状態通知部81を有する治具8で構成され、データの複写を制御する制御部が基板に設けられ、不揮発性メモリのアドレスを複写元又は複写先と設定するアドレス設定部を複写元、複写先の両基板は含み、制御部は、アドレス設定部の設定アドレスに基づき、複写元から複写先の不揮発性メモリにデータ複写を行い、その状況を状態通知部81に表示させる。

(もっと読む)

半導体記憶装置

【課題】記憶容量を増加することができるUSBメモリを提供する。

【解決手段】ホスト機器2と接続するためのUSB規格の第1のインターフェイス部14と、NANDメモリ部10と、それぞれが第2の半導体メモリ部3a〜3dを有する1以上の小型メモリカード3A〜3Dが接続可能な第2のインターフェイス部28とを有するUSBメモリ1であって、NANDメモリ部10および1以上の第2の半導体メモリ部3a〜3dを、ひとつのリニアアドレスで管理可能であるコントローラ19を有する。

(もっと読む)

情報機器

【課題】所定のアドレス値を拡張アドレス空間の先頭番地としても、主実装基板上のFeRAMのアドレス空間と拡張用記憶デバイスのアドレス空間とが重ならないようにする。

【解決手段】複数個のFeRAM21を搭載した拡張用FeRAMボード2を標準装備FeRAM12が1個搭載されたメインボード1に実装したとき、拡張用FeRAMボード2上のFeRAM21aに与えるCS信号を切り替えスイッチ16によりCS1からCS5に切り替えるとともに、CS5のカバーするアドレス空間をCS4のカバーするアドレス空間の後に続くアドレス空間とする。

(もっと読む)

半導体記憶装置および半導体記憶装置の制御装置

【課題】半導体記憶装置から出力される信号を用いて、制御装置に対する半導体記憶装置の装着位置が正しいか否かを判定すること、制御装置における半導体記憶装置の装着位置の判定処理に用いられる半導体記憶装置を提供すること。

【解決手段】半導体記憶装置10は、電源端子VT、リセット端子RT、クロック端子CT、データ端子DT、接地端子GT、検出信号入力端子CIT、検出信号出力端子COT、内部回路20を備えている。検出信号入力端子CITおよび検出信号出力端子COTは、それぞれ、検出信号入力信号線CILおよび検出信号出力信号線COLを介して、内部回路20と接続されている信号切替回路30に接続されている。

(もっと読む)

フラッシュメモリ制御インターフェース

【課題】 フラッシュメモリ制御インターフェースを提供する。

【解決手段】 ピンカウントを増やすことなく、マルチデバイスシステムが備える複数のフラッシュメモリデバイスを制御するインターフェース、装置および方法を開示する。一実施形態に係るシステムは、第1および第2のフラッシュメモリデバイスと、メモリコントローラとを備える。第1のメモリデバイスは、メモリコントローラから設定信号を受信して、設定信号から記録信号を第2のメモリデバイスのために生成する。当該記録信号はさらに、複数のメモリデバイスのうち最後のメモリデバイスからメモリコントローラに供給されるとしてもよい。メモリコントローラは、インターフェースを介して複数のメモリデバイスと通信する。当該インターフェースは、各メモリデバイスに接続されている複数のパラレル入出力(I/O)端子と、シリアルに接続されている制御端子とを有する。パラレルI/O端子は通常、データ(パラメータデータを含む)およびコマンドを送信する1以上のデータI/O端子と、クロック信号を受信するクロック端子と、ライトプロテクト信号を受信するライトプロテクト端子とを含む。

(もっと読む)

記憶制御装置及び記憶制御方法

【課題】既に搭載されているメモリモジュールと素子構成において異なるメモリモジュールが増設される場合においてもメモリアドレスを制御可能な記憶制御装置を提供する。

【解決手段】複数のメモリモジュールで構成され得る記憶装置を制御する記憶制御装置が、メモリモジュールの基本搭載単位及び増設単位毎にメモリモジュール構成情報を記憶するレジスタ32と、前記レジスタに格納されたメモリモジュール構成情報に基づいて、前記基本搭載単位のメモリモジュールのメモリアドレス空間と前記増設単位のメモリモジュールのメモリアドレス空間とが異なる場合にも、前記記憶装置にアクセス可能なアドレスを生成するアドレス変換手段38、42と、を具備するように構成される。

(もっと読む)

半導体記憶装置

【課題】貫通ビアによって共通接続された積層メモリチップのメモリチップを別々に動作させる。

【解決手段】制御パッド12に入力される信号は、それぞれメモリチップ2が有するRSTバッファ25、CEバッファ26、WEバッファ27、REバッファ28、CLEバッファ29、及びALEバッファ30に出力される。チップアドレス比較器24は、ヒューズ23に記憶された自己のチップアドレスINTCAiとアドレスバッファ17から入力されたチップアドレスEXTCAiとを比較し、一致するか否かをアドレスフラグ信号CAFLGとしてCEバッファ26に出力するよう構成されている。アドレスフラグ信号CAFLGが“H”の状態において、CEバッファ26からチップイネーブル信号CE’が出力され、メモリチップ2への書き込みや読み出しなどの動作が行われる。

(もっと読む)

メモリモジュール

【課題】高速且つ低コストで、メモリ容量の拡張性を確保できる使い勝手の良い情報システム装置を提供する。

【解決手段】情報処理装置、揮発性メモリおよび不揮発性メモリを含む情報処理システムを構成する。情報処理装置、揮発性メモリおよび不揮発性メモリは直列接続させ、接続信号数を少なくすることにより、メモリ容量の拡張性を保ちつつ、高速化を図る。不揮発性メモリのデータを揮発性メモリへ転送させる際は、エラー訂正を行い、信頼性の向上を図る。これら複数のチップからなる情報処理システムを、各チップが相互に積層して配置され、ボールグリッドアレイ(BGA)やチップ間のボンディングによって配線された情報処理システム・モジュールとして構成する。

(もっと読む)

メモリ装置

【課題】揮発性メモリを介してホストと記憶媒体との間でのデータのリード/ライトを制御する記憶媒体コントローラに対し、T13に準拠する不揮発性メモリを、ピン数の増加やサイズの増大を伴うことなく、付設することを課題とする。

【解決手段】インタフェース制御機能部10をさらに導入する。該機能部10は、揮発性メモリ(SDRAM)4と互換性を有するインタフェース制御を行う、不揮発性メモリ(フラッシュメモリ)8に対する不揮発性メモリ制御機能を、前記コントローラ2内の揮発性メモリ制御部6を介してサポートするように構成する。

(もっと読む)

集積回路装置

【課題】 複数のチップセレクト信号を受け取ることなく、上位装置から内蔵のレジスタへのアクセスを受け付け、かつ、上位装置とメモリとの仲介を行うことができる集積回路装置を提供する。

【解決手段】 画像処理LSI10には、レジスタ12と制御部11が設けられている。制御部11は、チップセレクト信号CSがアサートされており、かつ、アドレス信号が非開放領域42のアドレスを指定するものである場合には、CPU20によるレジスタ12へのアクセスの仲介を行い、チップセレクト信号CSがアサートされており、かつ、アドレス信号が開放領域41のアドレスを指定するものである場合には、CPU20による画像メモリ40へのアクセスを仲介する。

(もっと読む)

シリアルメモリインターコネクトを介して複数のメモリモジュールに接続されたホストを含むシステム

メモリモジュール(150A〜B)のシリアル接続されたチェーンに結合されたホスト(100)を含むシステム(50)。1つの実施形態において、メモリモジュールの各々は、メモリモジュール上の複数のメモリチップ(261)へのアクセスを制御するためのメモリ制御ハブ(160)を含む。メモリモジュールは、複数のメモリリンク(110)を介してホストへチェーン状にシリアル結合される。各メモリリンクは、ホストの方向へトランザクションを伝達するためのアップリンク(211)と、ホストで生じたトランザクションをチェーンの次のメモリモジュールに伝達するためのダウンリンク(212)とを含んでもよい。アップリンクおよびダウンリンクは、制御およびコンフィギュレーションパケットと、メモリアクセスパケットとを含むパケットを用いて、トランザクションを伝達してもよい。メモリ制御ハブは、トランザクションの復号とは関係なく、第2のメモリリンクの第2のダウンリンク上で、第1のメモリリンクの第1のダウンリンク上で受信したトランザクションを伝達してもよい。  (もっと読む)

(もっと読む)

マルチチップパッケージデバイス

【課題】2以上のメモリチップを含み、優先処理命令を実行するブートコードを効果的にアクセス可能であるマルチチップパッケージデバイス及びその駆動方法を提供する。

【解決手段】マルチチップパッケージデバイスは、制御信号及びアドレスを共有する第1及び第2メモリチップを含む。第1及び第2メモリチップのそれぞれはメインメモリとバッファメモリを備える。メインメモリは、所定の優先処理命令による動作を行うブートコードを記憶する。バッファメモリは、前記ブートコードを一時的に記憶するブートラムを含む。第1及び第2メモリチップのそれぞれは、アドレス及び制御信号に応答して、メインメモリのアクセスを駆動するメインアクセス信号及びバッファメモリのアクセスを駆動するバッファアクセス信号を発生するアクセス信号発生ブロックを含む。前記バッファアクセス信号は、所定のブート組合せのアドレスに応答して、一方向遷移が実行される。

(もっと読む)

記憶装置

【課題】限られた転送相手の数に関係なく、制御装置が少種類の多数のデバイスとデータ転送することを可能にする記憶装置を提供することを目的とする。

【解決手段】制御装置と複数のデバイスとを中継部を介して接続する。中継部は、制御装置の転送相手となる分岐部と、上記デバイスを特定するセレクト信号が入力されると、上記分岐部を介して、入力されたセレクト信号にて特定されるデバイスと上記データ転送部との間でデータ転送を行うための転送経路を確保する転送制御部を備える。

(もっと読む)

低電力マルチチップ半導体メモリ装置及びそれのチップイネーブル方法

【課題】低電力マルチチップ半導体メモリ装置及びそれのチップイネーブル方法を提供する。

【解決手段】低電力マルチチップ半導体メモリ装置及びそれのチップイネーブル方法は、外部から入力されたチップイネーブル信号と、外部から入力されたアドレス、及び前記半導体チップの識別情報に応答して、内部チップイネーブル信号を発生して、前記内部チップイネーブル信号に応答して前記複数個の半導体チップの中の一つを活性化させる。その結果、実際動作されない半導体チップが非活性化されて、電流消耗を効果的に減らすことができる。

(もっと読む)

1 - 20 / 21

[ Back to top ]