Fターム[5B061FF05]の内容

バス制御 (3,799) | バスアダプタ(バス結合装置) (397) | バス間接続用バスアダプタの作用効果 (343) | アドレス変換のため (20)

Fターム[5B061FF05]に分類される特許

1 - 20 / 20

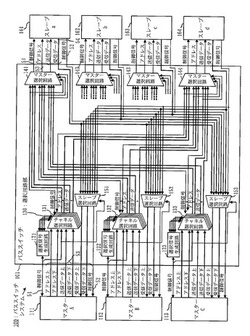

バススイッチ装置及びバススイッチシステム及びバススイッチ方法及びプログラム

【課題】マスター装置からスレーブ装置に対する操作要求と操作情報とを入力して、操作が要求されたスレーブ装置に操作要求と操作情報とを出力するバススイッチがあったが、スレーブ装置が増加すると、マスター装置からスレーブ装置へ出力する操作情報のトラフィックに対応できなかった。

【解決手段】バススイッチ101は、複数の操作情報チャネルに出力された操作情報を、操作が要求されたスレーブ装置に対応したチャネル選択回路に入力させるリクエスト信号とチャネル選択信号とを生成する選択信号生成回路121と、選択信号生成回路121が生成したリクエスト信号をもとに、上記スレーブ装置に対応したチャネル選択回路を選択する選択回路部130とを備え、選択されたチャネル選択回路が、複数の操作情報チャネルのうち、チャネル選択信号が表す操作情報チャネルから操作情報を入力する。

(もっと読む)

通信機器および通信システム

【課題】使い勝手の悪化を招くことなく適切なホスト間通信を実現することができる通信機器および通信システムを提供する。

【解決手段】第1の機器Cに設けた第1のPCI Expressスイッチ20のNTポート23と、第2の機器Dに設けた第2のPCI Expressスイッチ30のNTポート33と通信可能に接続する。第1の機器Cと第2の機器Dとの間で通信を行う際、第1のPCI Expressスイッチ20は、第1の機器Cが使用するアドレスとNTポート23が使用するアドレスとの間のアドレス変換を行い、第2のPCI Expressスイッチ30は、第2の機器Dが使用するアドレスとNTポート33が使用するアドレスとの間のアドレス変換を行う。

(もっと読む)

エンドポイント共有システムおよびデータ転送方法

【課題】サーバと記憶装置をPCIeで接続し、複数のサーバの中の特定のサーバと統合エンドポイントの間のデータ転送の高速化を図ったエンドポイント共有システムおよびデータ転送方法を得ること。

【解決手段】統合エンドポイントにおける所定のエンドポイントから現用系の主サーバにPCIeパケットが送信されると、このパケットを処理するサーバが決定され、そのサーバ名がPCIeパケットに挿入される。2次共有メモリ転送手段16は、サーバとの間のデータの個別伝送に使用する2次共有メモリのうちの該当するものに転送する。サーバ側から統合エンドポイントへのデータの転送も行われる。

(もっと読む)

エンドポイント共有システム、代理アクセス方法および代理アクセスプログラム

【課題】CPUの処理が増減した場合に、サーバの数を調整可能なエンドポイント共有システム、エンドポイント代理アクセス方法およびプログラムを得ること。

【解決手段】第1および第2のエンドポイントアクセス手段21、22は、現用系、待機系の主サーバ11、13および任意の台数の拡張サーバ12、14に代理して共通したエンドポイントにアクセスする。マッピング手段17は、主サーバ11、13からエンドポイントに対するアドレスをマッピングする。差分検出手段18は現用と予備の両系のアドレスの差分を求め、各サーバからエンドポイントにアクセスする際のアドレス変換手段19によるアドレス変換を可能にする。

(もっと読む)

リンクブリッジ

【課題】複数のバス間での情報転送のために改善されたシステムを提供する。

【解決手段】ホストプロセッサによりアクセスできるブリッジであって、第一バスと第二バスのインターフェース手段とともにリンクを持つ。第一インターフェースと第二インターフェースは、(a)第一バスと第二バスフォーマットと異なるフォーマットのリンクを介して情報をシリアルに出力する、(b)ブリッジを交差する宛先を表す特徴を持つペンディングのトランザクションに応答して第一バスと第二バスで初期交換を認めること、(c)該第一バスを介して通信するホストプロセッサは、(i)該第二バスの装置にアクセスするのに使用されるのと実質的に同じアドレスタイプを該第一バス上で使用するものであり、(ii)第一バスは、第二バスを使用することなく、該第二バス上のバスコンパティブルな装置の一つを調停する。

(もっと読む)

コンピュータシステム

【課題】圧縮されたプログラムを保存する記憶部に依存しない汎用性のある解凍装置を実現する。

【解決手段】プロセッサ1と、圧縮されたプログラムを保存する記憶部2とを接続するバス12,13中に、解凍装置15が設けられる。記憶部2に、プログラムの圧縮に関する圧縮情報が保存される。解凍装置15は、記憶部2から圧縮情報を収集する。解凍装置15は、圧縮されたプログラムのアドレス情報に基づいて、周辺バス13を流れるアドレス信号を検出し、解凍が必要なプログラムのデータが周辺バス13を流れているかを判断する。解凍装置15は、圧縮されたプログラムであると判断すると、データを解凍して、解凍したデータをプロセッサバス12を通じてプロセッサ1に送る。

(もっと読む)

情報処理装置、ブリッジ装置および情報処理方法

【課題】DMA転送先の読み出し速度の速い記憶媒体に対してプロセッサからの読み出し処理を可能とし、処理速度の向上を行う情報処理装置、ブリッジ装置および情報処理方法を提供することを課題とする。

【解決手段】ブリッジ105のDMA転送部108によるROM103からRAM104へのデータのDMA転送中にDMA制御部109は記憶部107に格納された管理テーブル21に現在DMA転送済みの領域のデータを保存する。CPU101が、ROM103とRAM104のマッピングを行った仮想アドレス空間41におけるROM103のアドレスに読み出しアクセスを行うと、制御部106は読み出しを行われたアドレスがDMA転送済みの領域に対応するアドレスであるならば、RAM104に読み出しアクセスを行い、DMA転送済みの領域に対応するアドレスでないならばROM103へと読み出しアクセスを行う。

(もっと読む)

マルチプロセッサシステム

【課題】複数のプロセッサが周辺装置を共有しても、当該周辺装置に割り当てられたアドレス空間の重複に起因する誤動作を確実に防止し得るマルチプロセッサシステムを提供する。

【解決手段】マルチプロセッサシステム1は、複数のプロセッサとバスを介して接続されたアドレス変換部35を有する。アドレス変換部35は、複数のプロセッサのうちアクセス要求を発したプロセッサからのアドレス情報を共有メモリ空間内のアドレス情報に変換する。共有メモリ空間は、複数のプロセッサにそれぞれ対応する複数のアドレス領域を有している。アドレス変換部35は、アクセス要求を発した当該プロセッサからのアドレス情報を、当該プロセッサに対応する当該アドレス領域内のアドレス情報に変換する。

(もっと読む)

ブリッジ、情報処理装置、情報処理システムおよびグローバルアドレス管理方法

【課題】コンピュータネットワーク上のノード間において、リソースの透過性を提供することにある。

【解決手段】複数のプロセッサユニットがスイッチング装置によって相互接続されてなる情報処理システムにおいて、各プロセッサユニットの実効アドレスがマッピングされた、複数のプロセッサユニット間で共有されるグローバルアドレス空間を導入する。プロセッサユニットの入出バスを、スイッチング装置の入出力バスへ中継するブリッジは、プロセッサユニットから、ターゲットノードの実効アドレスを指定したアクセス要求パケットを受け取り、この実効アドレスにそのターゲットノードの、スイッチングに必要なノード識別番号を付加することにより、ターゲットノードの実効アドレスをグローバルアドレスに変換して、グローバルアドレスが指定されたアクセス要求パケットをスイッチング装置に出力する。

(もっと読む)

PCI接続装置

【課題】I/O 空間を使用することなく、さらにはポーリングベースの処理をすることなく、PCI ローカルバスを利用して任意のPCI デバイス間で所望の情報を直接に通知し得るPCI接続装置を提供する。

【解決手段】PCI ローカルバス11を介して外部からPCI デバイス内部のメモリ空間へのアクセスを受け付けるPCI 接続装置において、同一のメモリ空間へのアクセスを別々のメモリ空間へのアクセスに変換するアクセス変換回路(12、13)を具備する。

(もっと読む)

データ処理システム

【課題】複数のマスタが調停を受けて共有スレーブにアクセスする構成において、共有スレーブアクセスのためのアドレス変換を行う場合、調停前にアドレス変換テーブルの情報の一部を保持する変換テーブルバッファとアドレス変換部とを実装すると、バッファの更新に調停待ち時間を含む大きなレイテンシが必要である。また、調停後に変換テーブルバッファとアドレス変換部とを実装すると、バッファの更新待ちの間、全てのマスタのアクセスが停止する。

【解決手段】調停部106にて調停を受ける前に変換テーブルバッファ129の更新を待ち合わせ、調停部106の後段にアドレス変換部125を置く。アクセスはバッファ更新が完了するのを待たず、アドレス変換時に更新が終わっていることを保証できる時点で先行的に発行する。これにより、バッファ更新待ちの他マスタへの影響を排し、アクセスレイテンシの短縮が図れる。

(もっと読む)

プラント制御装置の更新方法

【課題】安価で容易に更新を行うことができるプラント制御装置の更新方法を提供する。

【解決手段】既設のローカルPIO4a,4b、コモンPIO4cに対応して3台のバス変換ユニット6を設け、既設のCPU装置1a,1bを接続する。3台のバス変換ユニット6は各入力I/F部52,56を介してカスケード接続し、最右方のバス変換ユニット6の入力I/F部52に更新用の乙プラントコントローラ2のCPU装置2aを接続する。ローカル及びコモンPIO4a,4b,4cのプロセスデータは、各バス変換ユニット6に内蔵された図示しない記憶手段に記憶される。CPU装置2aは、アドレス変換部を介して当該プロセスデータを読み出して、プラント制御の模擬を行う。その後、バス変換ユニット6に内蔵された開閉切替手段にて、CPU装置1a,1bからは制御不可能にするとともに、更新用のCPU装置2aにてプラントの制御を行うようにし、更新する。

(もっと読む)

ノード制御装置および情報処理装置

【課題】バス番号のビット数が仕様で定義されているPCIバス等を使用する場合であっても、バス番号のビット数によって制限される本数以上のバスを使用できるようにする。

【解決手段】レジスタ400,401にコンフィグレーション空間のベースアドレス、サイズを設定することにより、メモリ空間に複数のコンフィグレーション空間をマップする。コンフィグレーションアクセス検出回路403は、フリット信号330に含まれている、アクセス対象デバイスが接続されているバスのバス番号と上記バスを配下に持つIOノードに割り当てられているコンフィグレーション空間のセグメント番号とをマージしたインデックス信号412を出力する。テーブル402は、インデックス信号412に対応するエントリに格納されているIOノード(上記バスを配下に持つIOノード)のノードIDを出力し、クロスバースイッチ320は、フリット信号330を上記ノードIDのIOノードへルーティングする。

(もっと読む)

データ処理システム内で第1のホスト・システムと第2のホスト・システムとの間で通信するための方法、プログラム、およびシステム(トランザクション・プロトコルおよび共用メモリを使用するホスト・システム間の通信のためのシステムおよび方法)

【課題】 トランザクション・プロトコルおよび共用メモリを使用するホスト・システム間の通信のためのシステムおよび方法を提供することにある。

【解決手段】 少なくとも1つのエンドポイントが少なくとも2つのホスト・システムの共用メモリ内にアドレス範囲を有するように、通信ファブリック内の発見プロセスに基づいて共用メモリが初期設定される。ホスト・システムの共用メモリを使用して同じかまたは異なるホスト・システムのルート複合体とエンドポイントとの間で通信するために、トランザクション指向プロトコルを確立することができる。このトランザクション指向プロトコルは、データをプッシュまたはプルするために、様々なエレメント、たとえば、ルート複合体またはエンドポイントによって実行すべき一連のトランザクションを指定する。プッシュ・トランザクションとプル・トランザクションの様々な組み合わせを使用することができる。

(もっと読む)

PCI−Express通信システム

【課題】PCI-Expressスイッチを用いたPCI-Express通信システムにおいて、あるノードから他のノードにリクエストが発行された後、他のノードからリクエスト元のノードにレスポンスが返されるまでにPCI-Expressスイッチ内でバスID/デバイスIDの付替えが発生しても、レスポンスパケットを当初のリクエスト元のノードであるターゲットに送付できるようにする。

【解決手段】各ノードにそれらを識別する固有のノードIDを設定するとともに、データ転送に使用する各チャネルにチャネルIDを設定し、データ転送についてのパケットのアドレス部内に、転送先モジュールの前記ノードIDと該データ転送に使用するチャネルの前記チャネルID、及び前記パケットがリクエストであるかレスポンスであるのかを識別するパケットタイプを設定する。そしてデータ転送には、アドレスルーティングでルーティングされるメモリライトリクエストパケットのみを使用する。

(もっと読む)

メモリバス変換装置及び情報処理システム

【課題】 動作速度やアクセス方法の異なる半導体メモリどうしを接続すること。

【解決手段】 アドレス変換部21は、バス7から受け入れるアドレス信号SIG20をROM5へ送出し、信号変換部20は、バス7から受け入れる制御信号SIG21をROM5へ送出するROMリード信号SIG27に変換し、記憶部22は、ROM5から受け入れるデータを一時保持し、出力制御部23は、記憶部22が格納するデータを読み出して、SDRAM3の制御プロトコルに基づくデータを出力する。

(もっと読む)

データ転送方法および装置

【課題】

プリフェッチ対象として指定するアドレス範囲を必要以上に広げることなく、また、実メモリの使用上のアドレス制限をなくすことのできるデータ転送方法および装置を提供する。

【解決手段】

データの読み出し元として入力された現在のバスアドレス500を、予め開始アドレスレジスタ1131に記憶している開始アドレス503と開始アドレスレジスタ1132が記憶している実メモリ上の開始アドレス504に基づいて、実メモリアドレス506に変換し、変換した実メモリアドレス506に基づいてメモリからデータの先読みを行う。

(もっと読む)

LSI内部バス

【課題】 データ転送効率を高め、動作速度を速くし、設計・検証時間を短縮する。

【解決手段】 データを一時的に保持可能な複数のバスブリッジ80を格子状に配置して、隣接するバスブリッジ80相互間およびバスブリッジ80とユニット200やユニット300間をバス10で接続する。各バスブリッジ80および各ユニット200,300にXY座標上のアドレスを付与する。データの転送は、送信元のユニット200のアドレスと送信先のユニット300のアドレスに基づき、該送信先のアドレス300に近づく2方向のいずれかのバスブリッジ80が選択されようにして、シフト動作により行う。

(もっと読む)

半導体装置、マイクロコンピュータ及び電子機器

【課題】バスインターフェイスにおいて、低コストかつ少ない消費電力でアクセス時間の短縮をはかること。

【解決手段】第2のバス40で接続されたバスマスタ20とバススレーブ30を含む半導体装置であり、BCU26は、受けとった絶対アドレスに対して、絶対アドレスに対応した相対アドレスの生成及び相対アドレスであること示す識別信号の生成を含む第2のバスを介して半導体記憶媒体に対して相対アドレスでアクセス要求を行うための処理を行う第1の相対アドレス制御回路28を含み、メモリコントローラ36は、前記識別情報に基づき、受けとったアクセスアドレスが相対アドレスであるか否か判断して、相対アドレスである場合には対応する絶対アドレスを演算する第2の相対アドレス制御回路38を含む。

(もっと読む)

並列SCSI−ファイバチャネルゲートウェイ

【課題】 パラレルSCSIバス上のSCSIイニシエータがファイバチャネル伝送媒体上のファイバチャネルターゲットと通信できるようにする。

【解決手段】 本発明は、SCSI−ファイバチャネルゲートウェイをパラレルSCSIバスと接続するフロントエンドSCSIコントローラと、前記ゲートウェイをファイバチャネル伝送媒体と接続するバックエンドファイバチャネルコントローラと、前記両コントローラに接続された処理システムとを含む。処理システムは、ファイバチャネルターゲットのファイバチャネル識別子を保持し、該識別子とパラレルSCSIバスに関連付けられたSCSI−IDとの間にマッピングを作成する。SCSIイニシエータとの通信時には、前記マッピングを用いて、ファイバチャネルターゲットがパラレルSCSIバス上のSCSIターゲットとしてSCSIイニシエータに論理的に現れるようにする。

(もっと読む)

1 - 20 / 20

[ Back to top ]