Fターム[5B062AA10]の内容

マイクロコンピュータ (2,258) | 目的、効果 (507) | その他 (94)

Fターム[5B062AA10]に分類される特許

1 - 20 / 94

マルチプロセッサ装置及びマルチプロセッサ装置の制御方法

マイクロコンピュータ及びマルチマイクロコンピュータシステム

【課題】、一のマイクロコンピュータを介する他のマイクロコンピュータのオンボード書込みを行うためのソフトウェア開発の負担軽減とシステムコストの低減とに寄与する。

【解決手段】外部インタフェースユニットに接続する外部端子を、別の外部インタフェースユニットに接続する外部端子に選択的にスルーさせるとともに、当該外部インタフェースユニットのインタフェース機能を抑止する、バイパス生成部(23)をマイクロコンピュータ(1)に採用する。マルチマイクロコンピュータシステムにそのマイクロコンピュータを第1のマイクロコンピュータとして採用し、第1のマイクロコンピュータにおける一の外部インタフェースユニットに書き込みホスト装置に接続するインタフェースコネクタを結合し、当該第1のマイクロコンピュータにおける他の外部インタフェースユニットを別の第2のマイクロコンピュータに接続する。

(もっと読む)

電子システム

【課題】マイコンが生成するPWMパルスの周波数精度を向上する「電子システム」を提供する。

【解決手段】サブマイコン21は、低精度発振子22が生成する動作クロックを、設定された分周比nで分周した周期を持つPWMパルスを出力する。高精度発振子12が生成する動作クロックで動作するメインマイコン11は、サブマイコン21が出力するPWMパルスの周期Tprを計測し、計測した周期Tprと現在サブマイコン21に設定されている分周比nとより、サブマイコン21の動作クロックの真の周期Tsrを算出する。そして、算出したサブマイコン21の動作クロックの真の周期Tsrより、PWMパルスの周期がPWMパルスの所望周期Tptに最も近くなる分周比nを求め、マイコン間通信を用いてサブマイコン21に設定する。

(もっと読む)

補正データ処理装置

【課題】補正データを格納する不揮発性記憶素子の有無に応じた設定情報を管理することなく、不揮発性記憶素子を削除可能な補正データ処理装置を得ること。

【解決手段】回路ユニット1,2から当該回路ユニット1,2の性能ばらつきを補正する第1の補正データを格納する不揮発性記憶素子10,20を削除した場合に、当該回路ユニット1,2の選択時におけるデータ信号線8の論理値をチップセレクト信号線4,5の論理値と同一の論理値とするダイオード11,21を備え、制御ユニット3が回路ユニット1,2を選択してから当該回路ユニット1,2に対してクロック信号を出力するまでの所定時間において、データ信号線8の論理値がチップセレクト信号線4,5の論理値と同一の論理値である場合には、該当する回路ユニット1,2の不揮発性記憶素子10,20がないものと判定し、補正量をあらかじめ所定値に設定した第2の補正データを適用するようにした。

(もっと読む)

マイクロコンピュータ

【課題】アプリケーションプログラムの完成前に、システム全体の電源回路の最適化が可能なマイクロコンピュータを提供すること。

【解決手段】本発明に係るマイクロコンピュータ100は、CPU101と、CPU101に接続されたバス107と、バス107に接続される通常動作モードと、バス107と遮断される擬似動作モードと、を備える機能ブロック103A〜103Cと、通常動作モードと前記擬似動作モードとのいずれかを選択するための制御信号を出力する選択回路102と、を備え、機能ブロック103A〜103Cが、擬似動作モードにおいて消費電流を生成する擬似動作回路105A〜105Cと、を備えるものである。

(もっと読む)

半導体装置および半導体装置の動作試験方法

【課題】ROMに試験用プログラムを記憶させることができない場合にも初期動作の試験が可能な半導体装置の実現。

【解決手段】CPUコア11と、ROM13と、RAM14と、アドレス信号をデコードして、ROMまたはRAMの選択信号を発生するROM/RAM選択アドレスデコーダ15と、スタンバイ制御回路19と、RAM、ROM/RAM選択アドレスデコーダおよびスタンバイ制御回路の電源を、通常電源とバックアップ電源の間で切り替えるバックアップ電源切換機構と、を備え、スタンバイ制御回路は、スタンバイモードから通常動作状態に変化すると、CPUコアがROMの替わりにRAMをアクセスするように、ROM/RAM選択アドレスデコーダを設定可能であり、CPUコアがRAMに記憶された初期動作プログラムにしたがって起動動作を実行可能である。

(もっと読む)

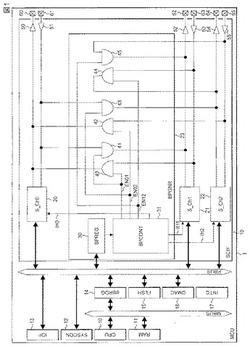

マイクロコンピュータ及び画像表示装置

【課題】LCDダイレクトドライブのための制御にハードウェアを用いることで、ユーザプログラム作成の負担軽減を図る。

【解決手段】クロック信号を形成可能なタイマパルスユニット(103)と、表示用データを液晶ディスプレイへDMA転送可能なDMAコントローラ(110)と、上記DMA転送に用いられる第1クロック信号と、上記液晶ディスプレイへの表示に用いられる第2クロック信号とを選択的に上記液晶ディスプレイのクロック入力端子へ伝達可能なセレクタ(105)とを設ける。また上記セレクタの選択状態を設定可能なレジスタ(106)と、上記レジスタの設定情報に基づいて、上記セレクタの選択状態を上記DMA転送に同期して制御するための制御論理(107)とを設ける。ユーザプログラムにおいては、LCDダイレクトドライブのための制御に関して上記レジスタへの設定を行うだけで良いので、ユーザプログラム作成の負担を軽減できる。

(もっと読む)

集積回路、及びこれを用いた情報処理システム

【課題】CPUによるブートコードの実行速度の高速化とシステムの柔軟性の確保とを両立させつつ、マスタ回路と集積回路とを組み合わせた情報処理システムと、マスタ回路を備えない小規模な情報処理システムとに共用することが容易な集積回路、及びこの集積回路を用いた情報処理システムを提供する。

【解決手段】CPUと、RAMと、外部に不揮発性メモリを接続可能なSPIマスタ23と、RAMへのアクセスを受け付けるSPIスレーブ24と、第1ブートモードが設定された場合、開始アドレスを含んで不揮発性メモリをマッピングし、第2ブートモードが設定された場合、開始アドレスを含んでRAMのアドレスをマッピングするアドレスマッピング部25と、第1ブートモードではリセット信号に応じてCPUのリセットを解除し、第2ブートモードでは第2インターフェース部を介したアクセスに応じてCPUのリセットを解除するリセット制御部26とを備えた。

(もっと読む)

I/O拡張回路

【課題】 汎用ロジックICのシフトレジスタを使ってI/Oポートを拡張すると共に、動作速度を向上させることができるI/O拡張回路を提供する。

【解決手段】 ワンチップマイコン1と汎用シフトレジスタIC2との間で連続出力モードを持つクロック同期方式を用いて、ワンチップマイコン1から汎用シフトレジスタIC2にシリアルデータ、同期クロック、ラッチタイミングの信号を送信し、汎用シフトレジスタIC2では、汎用ロジックICをカスケード接続した構成であり、受信した同期クロック、ラッチタイミングの信号に従って、シリアルデータを複数ビットのパラレルデータに変換するI/O拡張回路である。

(もっと読む)

半導体処理装置

【課題】デバッグツール2から直接に内蔵フラッシュメモリ5の書き換え制御を行うことができ、デバッグの作業効率を高くすることが可能なマイクロコンピュータを得る。

【解決手段】CPU3によって、内蔵フラッシュメモリ5に格納された内蔵フラッシュ情報をJTAGインタフェース11を介してデバッグツール2から読み出し可能にし、デバッグツール2からその内蔵フラッシュ情報に基づいた書き換みデータをJTAGインタフェース11を介して入力して、さらに、CPU3によって、内蔵フラッシュメモリ5に格納された書き換えプログラムに基づいて書き換みデータを内蔵フラッシュメモリ5に書き換える。

(もっと読む)

集積回路における修復可能IO

マルチコアプロセッサ及びこれを用いる車載電子制御装置

【課題】各コアの動作周波数を時系列で適切に変動させることで、放射ノイズ等の問題点を少なくとも部分的に解決すること。

【解決手段】 本発明は、複数のコアを搭載したマルチコアプロセッサ1,2であって、複数のコアA,B,Cは、同一の周期Tで周期的に周波数が変動する動作クロックで動作するように構成され、コアの動作クロックの周波数の変動位相が、前記複数のコア間でずらされることを特徴とする。好ましくは、各コアの動作クロックの周波数の変動位相は、時間T/N(Nはコア数)に相当する位相ずつずらされる。好ましくは、コアの動作クロックの周波数の変動態様は、複数のコア間で、変動位相が異なる以外は同一である。

(もっと読む)

シングル・チップ半導体集積回路装置の製造方法、プログラムデバッグ方法、マイクロコントローラの製造方法

【課題】短時間で、マスクROMを備えたシングル・チップの半導体集積回路装置を製造すること。

【解決手段】第1の集積回路(12)および第1のマスクROM(11)を有する第1の半導体集積回路基板(10)とプログラマブルROM(15)とが搭載された第1の半導体集積回路装置(20)の状態において、第1のマスクROM(11)が第1の内部バス(13)から電気的に切り離された状態で、その第1の集積回路(12)とプログラマブルROM(15)とを使用して決定された最終的なプログラムを、第1の半導体集積回路基板(10)と実質的に同一構成の第2の半導体集積回路基板(100)の第2のマスクROM(110)に記憶することにより、最終製品としての第2の半導体集積回路装置(200)を製造する。

(もっと読む)

半導体装置、マイクロコンピュータの制御方法

【課題】信頼性の高い統計多重制御が可能な統計多重装置を提供する

【解決手段】本発明によるマイクロコンピュータ10は、ステータスレジスタ5に設定された状態フラグ102に応じて、ユーザモードとプログラミングモードの一方を選択し、ユーザモードが選択された場合、不揮発性メモリ2内のユーザプログラムを実行し、プログラミングモードが選択された場合、不揮発性メモリ2へのユーザプログラムの書き込み又は消去を制御する書き込み用ファームウェア3を実行する。

(もっと読む)

マイクロコンピュータ

【課題】ダブルデータレート(DDR)方式のシンクロナスDRAMを高速アクセス可能なマイクロコンピュータを提供する。

【解決手段】中央処理ユニット、メモリ制御手段、及びクロック制御部を有するマイクロコンピュータは、クロック制御部から供給されたクロックを外部クロックとしてマイクロコンピュータの外部に出力し、外部クロックを反転したクロックをマイクロコンピュータの外部に出力する。メモリ制御手段は、前記クロックに対応し、第1の電位状態と第2の電位状態とに遷移するデータストローブ信号を生成する。メモリ制御手段によって制御されるメモリは、データストローブ信号の立ち上がりエッジと立ち下がりエッジに同期してデータの入出力を行うDDR方式の同期型メモリである。メモリ制御手段は、同期型メモリにデータを書き込むとき、前記データストローブ信号の立ち上がりエッジと立ち下がりエッジに同期してデータを外部に出力する。

(もっと読む)

半導体集積回路装置

【課題】外部のデバイスに接続される回路とLSI内部の回路との間におけるタイミング設計を不要とすること。

【解決手段】半導体集積回路装置は、外部デバイスに対して接続されるインタフェース回路であって第1のクロック信号が供給される第1の回路と、第1のクロック信号を分周した第2のクロック信号が供給される第2の回路と、第2のクロック信号を第1のクロック信号に基いて遅延させた送受信タイミング信号を生成するタイミング生成回路と、第2の回路から受信した信号を第1のクロック信号に同期してサンプリングする複数段のシフトレジスタと該複数段のシフトレジスタに対する入出力信号に含まれるハイレベルの信号とロウレベルの信号の多数決を送受信タイミング信号に同期して行うとともに多数決により決定された信号を第1の回路に出力する多数決回路とを有する第1の位相調整回路とを備えている。

(もっと読む)

半導体装置

【課題】マスクデータの変更をせずに複数のデフォルト値を設定する。

【解決手段】半導体装置80には、n個のデフォルト値設定回路が並列に配置される。n個のデフォルト値設定回路には、デフォルト値設定部2、デフォルト値設定部3、及びマルチプレクサMUX1がそれぞれ設けられる。デフォルト値設定部2は低電位側電源VSS電圧(ローレベル)を設定し、デフォルト値設定部3は高電位側電源VDD電圧(ハイレベル)を設定する。マルチプレクサMUX1は、デフォルト値設定部2及び3の値が入力され、モード選択信号Smsにより1ビットのデフォルト値を生成する。n個のデフォルト値設定回路はNビットのデフォルト値を生成する。

(もっと読む)

マイクロプロセッサ及びマイクロプロセッサのデバッグ方法

【課題】マイクロプロセッサの内部の論理不正動作の調査を容易化できるようにする。

【解決手段】論理動作不正が発生する命令列を、比較命令格納バッファ40に記憶し、プログラムを動作させ、命令比較部41で、実際に実行している命令と比較命令格納バッファ40に記憶されている命令とを比較し、コピー指示のある命令を検出すると、偶数個のコピー命令を生成する。後続のコピーされた偶数個の命令は、前方に存在する命令が完了するまで実行しない命令間隔に設定しており、タイミングや競合による論理動作不正を発生しない。命令列中の最後の命令から1命令ずつコピー指示を前の命令に移動させながらプログラムを実行し、多数決処理チェックの結果を確認することで、論理動作不正の発生する命令を特定する。

(もっと読む)

マイクロコンピュータ

【課題】新たなインタフェース仕様に対応することが可能なマイクロコンピュータを提供する。

【解決手段】バスコントローラ30は、固定バス制御部34と、可変バス制御部35とを含む。CPU10は、固定バス制御部34を介して内部ROM50にアクセスし、可変バス制御論理情報を読み出して、プログラム可能な可変バス制御論理部35にマッピングする。そして、CPU10は、可変バス制御論理部35を介して外部バス62と接続された外部メモリに対してアクセスする。

(もっと読む)

マイクロコンピュータ

【課題】大きなコストや製造工数を要することなく使用できる周辺機能の組合せに対して融通性を有するマイクロコンピュータを提供する。

【解決手段】中央処理装置(2)、動作モードの制御を行うシステムコントローラ(5)、不揮発性メモリ(4)、及び複数の周辺回路(6〜17)を備えたマイクロコンピュータにおいて、システムコントローラは、これに入力されるモード信号(SCMD0,SCMD1)に応じて不揮発性メモリから初期化データ(SYSCONFIG)を読み出して夫々の周辺回路の活性又は非活性を決定し、決定する活性及び非活性の組合せの態様を、モード信号の値によって決める。マイクロコンピュータの設計段階で予め想定し得る周辺機能をチップに搭載し、活性化する周辺機能の組合せを規定する数通りの初期化データを不揮発性メモリの初期的に書き込み、その中からモード信号に応じた初期化データを選択できるように対応付けておく。

(もっと読む)

1 - 20 / 94

[ Back to top ]