Fターム[5B062EE03]の内容

マイクロコンピュータ (2,258) | チップ外部との入出力 (243) | 入出力ポート (43)

Fターム[5B062EE03]の下位に属するFターム

入出力ポートの入力/出力の選択 (13)

Fターム[5B062EE03]に分類される特許

1 - 20 / 30

マイクロプロセッサ

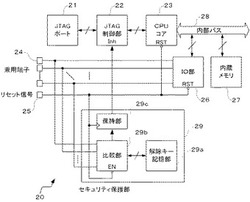

【課題】セキュリティビットをオンにしてフラッシュROMを書き換え禁止にする手法はフラッシュROMの再書き込みができず、解除キーが入力されたときに書き換えを許可する手法は、解除キー入力の専用端子が必要になり、端子数が増加する。本発明は端子数が増加せず、かつ再書き込みができるマイクロプロセッサを提供することを目的とする。

【解決手段】リセット信号がアクティブになったときに解除キーを入力する端子を入力端子に設定し、この端子に印加されるデータと解除キーを比較し、リセット信号がインアクティブに変化したときにこの比較結果を保存して、この保存した信号でデバッグ部の動作の許可、禁止を制御した。解除キー入力端子をユーザが使用する汎用端子と兼用できる。

(もっと読む)

集積回路における修復可能IO

高電圧集積回路用のモード選択のための方法と装置

【課題】追加の高電圧回路の不便なしに高電圧集積回路の端子に機能性を追加する方法を開示する。

【解決手段】特典は追加の端子の犠牲なしに集積回路の試験、トリミング・パラメータ、または他の目的で代替動作モードを選択することができることである。一実施形態において、普通の低電圧回路が、通常高電圧に曝される端子の電圧をモニタリングする。簡単な電圧検出器と通常のラッチの構成により、集積回路が意図された用途にないときには試験とトリミング・モードに容易に入ることができるが、集積回路が意図された用途で動作しているときには試験とトリミング・モードに入ることが禁止される。

(もっと読む)

マイクロコンピュータチップ

【課題】車両用電子制御装置(以下、ECU)に用いられると共に、他の半導体チップが内部のバスに接続可能なマイコンチップにおいて、その半導体チップが接続されない使用形態での消費電流を低減する。

【解決手段】ECUに用いられるマイコンの本体チップ1は、車両及びECUの開発時においては、内部のバス11にキャリブレーション用チップ2が接続端子22を介して接続されるが、車両及びECUの量産時には、上記チップ2が接続されずに使用される。このため、本体チップ1において、接続端子22につながるバス11の信号線へ信号を出力するための少なくとも1つの出力回路43は、それの信号出力能力が、入力端子X1〜X3から与えられる制御信号S1〜S3によって変わるように構成されている。このため、上記チップ2が接続されない場合には、バス11の信号線への信号出力能力を小さくして消費電流を低減できる。

(もっと読む)

コンピュータ装置

【課題】RC発振器の周波数変動が大きい場合やRC発振器の周波数とUARTの通信速度が近い場合であっても、スタンバイ状態にあるマイクロコントローラを正常に起動させることができるようにする。

【解決手段】UART機能とスタンバイ機能を有するマイクロコントローラ1を備え、該マイクロコントローラがスタンバイ状態のとき該マイクロコントローラ用のCPUクロック発振器3が動作を停止するコンピュータ装置において、マイクロコントローラ1がスタンバイ状態のときUARTによるUART起動信号を受信すると割込み信号INTUを生成するUART起動回路10を備え、該割込み信号INTUによりCPUクロック発振器3が動作を開始するとともにマイクロコントローラ1が通常動作に復帰する。

(もっと読む)

演算処理装置及び演算処理方法

【課題】安価なマイクロコンピュータであっても、ノイズの発生による影響を回避して、適切なタイミングで信号の変換入力が可能な演算処理装置を提供する。

【解決手段】信号端子AF+に入力された信号を変換指令に基づいてA/D変換するA/D変換部31aと、A/D変換された信号データを入力し、信号データと閾値を比較して、その結果に基づいて所定の制御信号を出力する信号出力部31bと、信号データに基づいて閾値を調整する閾値算出部31cを備え、信号出力部31bはA/D変換された信号データを入力した後、制御信号S2を出力する前に、A/D変換部31aに次のA/D変換のための変換指令を出力する。

(もっと読む)

出力ポート、マイクロコンピュータ、及びデータ出力方法

【課題】割り込み処理の影響を受けずに、出力データをビット単位に切り替え可能なポート回路、マイクロコンピュータ、及びデータの出力方法を提供することにある。

【解決手段】本発明による出力ポート回路3は、複数の出力バッファ24への出力データを保持する複数の第1保持回路22と、複数の第1保持回路22へ出力すべきデータを保持する複数の第2保持回路20と、複数の第2保持回路20の出力データが複数の第1保持回路22に取り込まれるか否かを個別に設定するビットパタンデータを保持する複数の第3保持回路21とを具備する。複数の第2保持回路20へのデータ入力と複数の第3保持回路21へのデータ入力とは同一タイミングで制御される。

(もっと読む)

電子制御装置

【課題】マイコンを監視する監視ICを備えた電子制御装置(ECU)にて、マイコンが、異常時に実施すべき異常時処理をより確実に実行できるようにする。

【解決手段】監視IC10によりマイコン20の動作を監視すると共に、監視IC10は、マイコン20の異常を検出すると、そのマイコン20にフェールセーフ信号(FSINIT)を出力する。FSINITは、マイコン20において、マスク不可割込を発生させるためのNMI端子に入力され、これにより、マイコン20においてマスク不可割込が発生する。監視IC10がマイコン20の異常を検出するため、マイコン20の異常の種類に関係なく、より確実に異常が検出されると共に、マイコン20においてマスク不可割込が確実に発生する。マイコン20は、このマスク不可割込で異常時処理を実行するようになっており、このため、異常時処理が確実に実行される。

(もっと読む)

半導体集積回路装置

【課題】回路の簡易化及びデータ入出力のタイミングの自由度を高くすることができる半導体集積回路装置を提供する。

【解決手段】IOコンフィグレーション・ブロック104は、入力グループPORT−Aを外部ピンの先頭にピン番号の正順に割り当て、出力グループPORT−Bを外部ピンの後尾にピン番号の逆順に割り当て、余った外部ピンにその他の機能グループOPTIONの信号を割り当て、その他の機能グループOPTIONの信号より入力グループPORT−Aの信号を優先して割り当てる。

(もっと読む)

半導体装置

【課題】マルチコア方式の半導体装置では、CPU単体の消費電力は低減されるが、CPU−CPU間などのデータ・バスにおける消費電力が増大する。

【解決手段】データ送信に無線信号のバックスキャッタ方式を用いる複数のCPUと、CPU−CPU間などのデータ送受信を仲介するルータ回路と、スレッドのスケジューリング機能を有するスレッド回路と、を有することで、低消費電力で高演算能力の半導体装置を安価に提供することができる。

(もっと読む)

プロセッサ

【課題】本発明はCPUまたはDSPを含むDSPコアを備えバスコントローラを介して外部バスと接続され,外部バスに接続された外部装置に対してリードアクセスを行うプロセッサに関し,外部デバイスにリードアクセスを行う際のウエイト時間を短縮して処理能率を向上することを目的とする。

【解決手段】プロセッサ内の外部バスに接続するバスコントローラとDSPコアの間に外部装置に対するリードアクセスのためのリードバッファを設け,リードバッファにリードアドレスとリードデータのレジスタとフラグを設け,フラグは外部バスへの読出しアクセスによりセットされ,リードが完了するとリセットされ,リードバッファはDSPコアからのアドレスのライトアクセスを受け取ると外部バスに対してリードアドレスによりリードアクセスを実行すると共にフラグをセットし,リードデータを受け取るとフラグをリセットしてリード完了を表すよう構成する。

(もっと読む)

マイクロコンピュータ及びマイクロコンピュータのデバッグ方法

【課題】セキュリティ解除に用いるプログラムが更新された場合においても、煩雑な作業なしに、デバッグを開始するためのセキュリティ解除を行うこと。

【解決手段】本発明にかかるマイクロコンピュータは、複数の格納領域を備えプログラムが前記複数の格納領域に分散して格納される不揮発性メモリ203と、プログラムを実行する中央演算処理装置270とを有するマイクロコンピュータ201であって、プログラムのデバッグを行うために使用するデバッグ用装置600を接続するためのデバッグ用端子と、複数の格納領域の各々に対応付けられた複数のデバッグ機能設定値を格納するデバッグ機能設定用メモリ206と、デバッグ機能設定値に基づいて選択される格納領域に格納されたプログラムの一部とデバッグ用端子から入力されるデータとを比較し、当該比較の結果に基づいて、外部からのアクセスの許否を判断するデバッグ判断部260とを備える。

(もっと読む)

IPコア及び複合IPコア

【課題】外部からの制御を全く必要としないで単体でも機能する完全自立形の基本モジュールを複数組み合わせて別の機能を発揮するIPコアを構成することができる基本モジュール及びIPコアを提供する。

【解決手段】本発明は、他のIPコアとの間で通信データを運ぶデータバス12に対してデータの入出力を司るI/Oインタフェース15と、所定の演算処理を実行するモジュール機能本体16と、同一IPコア内の他のIPコアモジュールとの間で所定のフォーマットのデータを運ぶシステム内バス14に対してデータの入出力を司るモジュール間インタフェース17と、I/Oインタフェース、モジュール機能本体、モジュール間インタフェースを統括制御するコントローラ18とを備えた基本モジュールを特徴とする。

(もっと読む)

半導体集積回路装置

【課題】 パッケージの端子数の増加と、ベースチップのI/O領域の増加を抑制すること。

【解決手段】 マスクROM領域と内部バス(13)とを有する半導体集積回路基板(10)と、この半導体集積回路基板上に積層され、複数のROM接続端子(15−1,15−2)を持つプログラマブルROM(15)とを備えた半導体集積回路装置(20)において、内部バスに接続された複数のバス接続端子(132−1,134−1)と複数のROM接続端子とがそれぞれ電気的に接続されている。複数のバス接続端子は、半導体集積回路基板の外周に設けられて良いし、マスクROM領域上に設けられても良いし、内部バス上に設けられても良い。この場合、複数のROM接続端子と複数のバス接続端子とはワイヤボンディングによって電気的に接続される。

(もっと読む)

マイクロコンピュータ及び電子制御装置

【課題】信号が入力される端子数を抑えることができ、かつ消費電流を低減させることのできるマイクロコンピュータ、及びそのマイクロコンピュータを備えた電子制御装置を提供する。

【解決手段】マイコン2に異常が生じるか、或いはIGSW5がオフ状態となると、リセット信号出力部84からアクティブレベルのリセット信号がマイコン2のリセット端子10に入力される。すると、マイコン2では、リセット端子10から、アクティブレベルのオフ指令信号がスイッチSW1,SW2に出力され、接続状態が切り換えられる。SW2が切り換えられると、CPU40の動作クロックが、発振回路28が生成するメインクロックからオンチップオシレータ30が生成するサブクロックに切り換えられ、スイッチSW1が切り換えられると、発振部20と振動子26との接続が遮断され、発振回路28が動作を停止する。このため、消費電流が低減される。

(もっと読む)

シングルチップマイクロコンピュータ

【課題】多数の割込によるデータ転送および使用者毎の固有の処理を可能とし、かつ処理効率が向上できる半導体集積回路装置、さらにこの半導体集積回路装置のデバック効率の向上が可能なエミュレータを提供する。

【解決手段】シングルチップマイクロコンピュータであって、CPU1/2、ROM1/2、RAM1/2、RAMP、タイマ、パルス出力回路、SCI、A/D変換器、IOP0〜IOP11、割込コントローラ、バスコントローラ、クロック発振器の機能ブロックから構成され、これらの機能ブロックは、CPU1,ROM1およびRAM1がIAB1,IDB1、CPU2,ROM2およびRAM2がIAB2,IDB2、RAMPがPAB,PDBに接続され、このIAB1,IAB2およびPABと、IDB1,IDB2およびPDBとの独立したインタフェースによってCPU1とCPU2が並列に動作可能となっている。

(もっと読む)

半導体集積回路装置

【課題】複数のCPUが設けられた半導体集積回路装置において、I/O端子の機能割り付けを管理することにより、I/O端子数を削減する。

【解決手段】接続決定部6は、各々の外部端子として設けられるI/O端子CPORT0〜CPORT23の接続先を、機能選択レジスタ7に設定された機能設定データにより、選択して切り換える。たとえば、I/O端子CPORT0に対応する機能選択レジスタ7の機能設定データが’0’の場合には、I/O端子CPORT0がCPU2に管理される内部汎用入力ポートIPORT4に接続される。I/O端子CPORT0に対応する機能選択レジスタ7の機能設定データが’1’の場合には、I/O端子CPORT0が内部汎用入力ポートGPI4に接続される。このように、I/O端子の接続先を予め設定した2つの機能から選択する。

(もっと読む)

ソフトウェア熱プロファイルの分析生成のコンピュータによって実施する方法、データ処理システム、およびコンピュータ・プログラム

【課題】 ソフトウェア熱プロファイルの分析生成のためにコンピュータによって実施する方法、データ処理システム、およびコンピュータ使用可能コードを提供する。

【解決手段】 熱プロファイルを生成するために、1セットのプロセッサによってプログラムを実行するために1セットの命令ストリームを分析して、分析情報を作成する。分析情報に基づいて温熱指数を生成する。

(もっと読む)

複数のマイコンのパワーオンクリア動作の制御方法

【課題】 複数のマイコンのPOC動作を一つのPOC回路により一括して確実に行う複数のマイコンのパワーオンクリア動作の制御方法を提供する。

【解決手段】 パワーオンクリア信号出力部1Cの制御を行うマスタマイコン1と、パワーオンクリア信号出力部1Cの制御を行わないスレーブマイコン2〜Nとを備えた電子回路において、電子回路の電源電圧が所定値以下となった後に該所定値以上になった際は、パワーオンクリア信号出力部1Cが出力したパワーオンクリア信号によりマスタマイコン1とスレーブマイコン2〜Nがパワーオンクリア動作を行う一方、パワーオンクリア動作が終了した際は、スレーブマイコン2〜Nはマスタマイコン1に動作開始信号を出力し、マスタマイコン1はスレーブマイコン2〜Nすべてから動作開始信号を受け取った場合にパワーオンクリア信号出力部1Cにパワーオンクリア信号を停止するクリア信号を出力する。

(もっと読む)

集積回路装置、マイクロコンピュータ及び電子機器

【課題】データ解析結果をフィードバックさせてより精度の高い解析処理を可能とする集積回路装置、マイクロコンピュータ、電子機器を提供すること。

【解決手段】本集積回路装置10は、所与のパラメータ70、72、74、76、78に基づき、センサ100から受け取ったアナログ信号60に対して所定の周波数帯域を抽出してデジタル変換を行いデジタル信号を出力するアナログ信号処理回路40と、デジタル信号62に基づき、デジタルデータ列が描く波形の特徴抽出を行う特徴抽出処理手段50と、特徴情報64を受け取り、予め用意されたパラメータ調整用アルゴリズム又はパラメータ調整用テーブルを用いて、アナログ信号処理回路の前記パラメータを調整するためのパラメータ調整値を演算するパラメータ調整値演算手段20、30とを含む。前記アナログ信号処理回路40は、パラメータの調整値に基づき前記所与のパラメータの値をプログラマブルに調整する。

(もっと読む)

1 - 20 / 30

[ Back to top ]