Fターム[5B062EE10]の内容

マイクロコンピュータ (2,258) | チップ外部との入出力 (243) | 外部とのインタフェース一般 (53)

Fターム[5B062EE10]に分類される特許

1 - 20 / 53

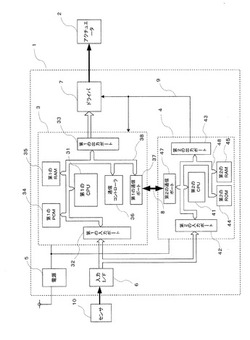

電子制御装置

【課題】第1のマイコンの異常を第2のマイコンにより確実に監視することが出来る電子制御装置を提供する。

【解決手段】少なくとも2個のマイクロコンピュータを有し、第1のマイクロコンピュータ(3)が主に制御対象の制御を司り、第2のマイクロコンピュータ(4)が、主に第1のマイクロコンピュータ(3)の異常の監視を行なうように構成された電子制御装置であって、第1マイクロコンピュータ(3)は、自身が制御量の演算に用いるデータの少なくとも一部を、自身の演算リソースを用いずに第2のマイクロコンピュータ(4)に送信するように構成され、第2のマイクロコンピュータ(4)は、送信されたデータに基づいて第1のマイクロコンピュータ(3)の異常の有無を判断するように構成されている。

(もっと読む)

半導体集積装置

【課題】SiPのチップ間を接続するための端子数が増加する。

【解決手段】パッケージ内部に第1の半導体チップと第2の半導体チップが集積される半導体集積回路であって、前記第1の半導体チップは、第1の通信部と、複数のアナログ回路とを備え、前記第2の半導体チップは、第2の通信部と、前記複数のアナログ回路の特性調整用データを格納するメモリ部とを備え、前記第1の通信部と前記第2の通信部とがシリアルデータ通信線で接続され、前記シリアルデータ線を経由して前記第1の半導体チップが備える複数のアナログ回路の特性調整用データをそれぞれ複数のアナログ回路に転送する半導体集積回路。

(もっと読む)

セット機器及びセット機器の制御方法

【課題】メモリカードに保存したマイコンのアプリケーション命令コードを読み出しを高速化する。

【解決手段】メインマイコンLSI1100とカードホストLSI1200とメモリカード1300aとがそれぞれ所定のカードバス仕様に準拠したカードバスの信号線CD1110a,CD1200a及びクロック信号線CK1110a,CK1200aにより接続されている。boot検出回路1240のバススイッチ制御信号1240aによりI/O回路1250a、1250bの制御方向をアプリケーション命令コードを読み出す方向に設定する。

(もっと読む)

半導体集積回路

【課題】内部プロセッサ、メインメモリ用のメモリI/F、外部プロセッサを有するデバイス用の外部I/F、及びレジスタを備えた半導体集積回路において、内部プロセッサからレジスタ制御を行った場合と外部プロセッサからレジスタ制御を行った場合との応答性能差異を少なくすると共に、外部プロセッサからメインメモリへのアクセス制御を行う場合の応答性能を向上させ処理速度を含めたシステム全体の性能を向上させる。

【解決手段】半導体集積回路(SoC1cで例示)は、プロセッサ11、メモリコントローラ15がバス接続された第1の内部バス(バス10で例示)とレジスタ31がバス接続された第2の内部バス(バス30で例示)とを含む複数の内部バスを備え、且つプロセッサ11及び外部プロセッサの両方からレジスタ31にアクセス可能なように構成される。外部I/F16は第1の内部バスと第2の内部バスとに接続された他の内部バスにバス接続される。

(もっと読む)

制御基板

【課題】制御基板の部品点数を抑えることで、実装面積やコストを抑えた制御基板を提供することを目的とする。

【解決手段】1つ以上の抵抗で構成されたプルアップ抵抗4(若しくはプルダウン抵抗)と、プルアップ抵抗4に接続されたスイッチ3と、マイコン端子8を介してロムライタ12によるオンボード書き込み可能なマイコン2を備えた制御基板1であって、マイコン2へのデータ書き込み時には、制御基板1とロムライタ12を接続し、プルアップ抵抗4を介して、マイコン2へのデータ書き込みが行われ、マイコン2にデータが書き込まれた後は、制御基板1とロムライタ12との接続を切り離し、マイコン2のユーザプログラム実行時には、マイコン2はプルアップ抵抗4を介して、スイッチ3を制御する。

(もっと読む)

多コア・プロセッサの電力供給及び電力管理

【課題】本願における開示された主題の実施例によれば、複数の電圧調節器(「VR」)を備えた電力管理システムを用いて、多コア・プロセッサ内のコアに電力を供給することができる。

【解決手段】各VRは電力をコア、又はコアの一部に供給することができる。別々のVRが、複数の電圧を多コア・プロセッサ内のコア/一部に供給することができる。VRの出力電圧の値は、電圧調節器が電力を供給する先のコア/一部の方向下で調節することができる。一実施例では、複数のVRをコアと単一のダイに一体化することができる。別の実施例では、複数のVRを備えた電力管理システムは、多コア・プロセッサのダイとは別個のダイ(「VRダイ」)上にあり得る。VRダイは、多コア・プロセッサ・ダイと同じパッケージに含めることができる。

(もっと読む)

マイクロコンピュータ及び画像表示装置

【課題】LCDダイレクトドライブのための制御にハードウェアを用いることで、ユーザプログラム作成の負担軽減を図る。

【解決手段】クロック信号を形成可能なタイマパルスユニット(103)と、表示用データを液晶ディスプレイへDMA転送可能なDMAコントローラ(110)と、上記DMA転送に用いられる第1クロック信号と、上記液晶ディスプレイへの表示に用いられる第2クロック信号とを選択的に上記液晶ディスプレイのクロック入力端子へ伝達可能なセレクタ(105)とを設ける。また上記セレクタの選択状態を設定可能なレジスタ(106)と、上記レジスタの設定情報に基づいて、上記セレクタの選択状態を上記DMA転送に同期して制御するための制御論理(107)とを設ける。ユーザプログラムにおいては、LCDダイレクトドライブのための制御に関して上記レジスタへの設定を行うだけで良いので、ユーザプログラム作成の負担を軽減できる。

(もっと読む)

マルチプロセッサ装置

【課題】同一チップ上に複数のマルチプロセッサを含む場合、異なるアーキテクチャごとに独立したバスと外部バスI/Fを持つことで、高性能のマルチプロセッサを得ることを目的とする。

【解決手段】本発明におけるマルチプロセッサ装置は、例えばCPU1〜8、SIMD型超並列プロセッサ31,32、DSP41,42のようにアーキテクチャの異なる第1,第2のプロセッサ群を含む複数のプロセッサと、第1のプロセッサ群が接続されているCPU10バスである第1のバスと、第2のプロセッサ群が接続されて第1のバスとは独立した内部周辺バス14である第2のバスと、第1のバスが接続されている第1の外部バスI/Fと、第2のバスが接続されている第2の外部バスI/Fとを一の半導体チップ上に備える。

(もっと読む)

LSI,鉄道用フェールセーフLSI,電子装置,鉄道用電子装置

【課題】従来のフェールセーフLSIは、チップ内のプロセッサや比較回路の配置について言及されていたが、パッケージの信号ピン配置までは言及されていなかった。また、多様な周辺回路や高速な外部メモリへの対応も考慮されていなかった。

【解決手段】2つのプロセッサからの出力を照合して一本化された内部インタフェースを共通系内部バスに接続し、その共通系内部バスに複数の外部インタフェース回路を接続する。また、2つの系統に関する信号ピンをパッケージの対角に配置するともに、それらの間に共通系に関する信号ピンを配置するようにする。

(もっと読む)

半導体装置、マイクロコンピュータの制御方法

【課題】信頼性の高い統計多重制御が可能な統計多重装置を提供する

【解決手段】本発明によるマイクロコンピュータ10は、ステータスレジスタ5に設定された状態フラグ102に応じて、ユーザモードとプログラミングモードの一方を選択し、ユーザモードが選択された場合、不揮発性メモリ2内のユーザプログラムを実行し、プログラミングモードが選択された場合、不揮発性メモリ2へのユーザプログラムの書き込み又は消去を制御する書き込み用ファームウェア3を実行する。

(もっと読む)

マイクロコンピュータ

【課題】ダブルデータレート(DDR)方式のシンクロナスDRAMを高速アクセス可能なマイクロコンピュータを提供する。

【解決手段】中央処理ユニット、メモリ制御手段、及びクロック制御部を有するマイクロコンピュータは、クロック制御部から供給されたクロックを外部クロックとしてマイクロコンピュータの外部に出力し、外部クロックを反転したクロックをマイクロコンピュータの外部に出力する。メモリ制御手段は、前記クロックに対応し、第1の電位状態と第2の電位状態とに遷移するデータストローブ信号を生成する。メモリ制御手段によって制御されるメモリは、データストローブ信号の立ち上がりエッジと立ち下がりエッジに同期してデータの入出力を行うDDR方式の同期型メモリである。メモリ制御手段は、同期型メモリにデータを書き込むとき、前記データストローブ信号の立ち上がりエッジと立ち下がりエッジに同期してデータを外部に出力する。

(もっと読む)

マイクロコンピュータ

【課題】新たなインタフェース仕様に対応することが可能なマイクロコンピュータを提供する。

【解決手段】バスコントローラ30は、固定バス制御部34と、可変バス制御部35とを含む。CPU10は、固定バス制御部34を介して内部ROM50にアクセスし、可変バス制御論理情報を読み出して、プログラム可能な可変バス制御論理部35にマッピングする。そして、CPU10は、可変バス制御論理部35を介して外部バス62と接続された外部メモリに対してアクセスする。

(もっと読む)

情報処理装置及び制御方法

【課題】書き換え可能なメモリがICチップの外部に配置されていても消費電力を抑えることができる情報処理装置を提供することを目的とする。

【解決手段】本発明に係る情報処理装置は、CPU、内部メモリ及び前記CPUと前記内部メモリとを接続する内部配線が搭載されたICチップと、前記ICチップの外部にあり、インターフェースで前記内部配線と接続される外部メモリと、処理待機時に前記内部メモリ内の待機プログラムを前記CPUに実行させ、外部からの処理要求時に前記外部メモリ内の処理プログラムを前記CPUに実行させる実行番地遷移手段と、前記処理待機時に前記外部メモリを停止させ、前記処理要求時に前記外部メモリを動作させる外部メモリ制御手段と、を備える

(もっと読む)

シングルチップデータプロセッサ及び半導体集積回路

【課題】接続している別のデータプロセッサから、当該データプロセッサの内部機能若しくは当該データプロセッサの外付け回路を効率良く利用する方法を提供する。

【解決手段】一のデータプロセッサ101に他のデータプロセッサ100との接続を可能にするためのインタフェース手段119を設け、このインタフェース手段に、一のデータプロセッサ内の内部バス108に他のデータプロセッサをバスマスタとして接続可能にする機能を設け、内部バスにメモリマップされた周辺機能を前記インタフェース手段を介して外部より当該他のデータプロセッサが直接操作できるようにする。これにより、データプロセッサは、実行中のプログラムを中断することなく、別のデータプロセッサの周辺機能等を使うことが可能となる。要するに、一のデータプロセッサは別のデータプロセッサの周辺リソースを共有することが可能になる。

(もっと読む)

電子制御装置

【課題】電子制御装置におけるタイマ回路が正常なことを短い時間で確認可能にする。

【解決手段】イグニッションスイッチ(IGSW)のオンにより電源が供給されて動作するマイコンと、常時電源供給されるソークタイマとを備えた車載電子制御装置にて、マイコンは、IGSWのオンにより起動すると、ソークタイマ異常検出処理を一定時間毎に実行する。その処理では、初回の実行時に、ソークタイマを起動し(S320)、ソークタイマのカウント値であるタイマ値が1つ変化する時間(1カウント時間)を計測するためのカウンタCT1をクリアする(S330)。そして、毎回、カウンタCT1をインクリメントし(S350)、タイマ値が変化したと判定すると(S370:YES)、その時点でのカウンタCT1の値により、ソークタイマの正常/異常を判定する(S380〜S395)。よって、ソークタイマが正常なことをほぼ1カウント時間で確認できる。

(もっと読む)

マイクロコンピュータチップ

【課題】車両用電子制御装置(以下、ECU)に用いられると共に、他の半導体チップが内部のバスに接続可能なマイコンチップにおいて、その半導体チップが接続されない使用形態での消費電流を低減する。

【解決手段】ECUに用いられるマイコンの本体チップ1は、車両及びECUの開発時においては、内部のバス11にキャリブレーション用チップ2が接続端子22を介して接続されるが、車両及びECUの量産時には、上記チップ2が接続されずに使用される。このため、本体チップ1において、接続端子22につながるバス11の信号線へ信号を出力するための少なくとも1つの出力回路43は、それの信号出力能力が、入力端子X1〜X3から与えられる制御信号S1〜S3によって変わるように構成されている。このため、上記チップ2が接続されない場合には、バス11の信号線への信号出力能力を小さくして消費電流を低減できる。

(もっと読む)

マルチチッププロセッサ

【課題】

プロセッサコア数を可変とすることによるスケーラブルな演算性能、および自由度が高く再構成可能なプロセッサコア間結合トポロジを特徴とする、組み込み向け低コストマルチプロセッサを実現する。

【解決手段】

少なくともプロセッサコアとメモリとを有するユニットチップを複数積層して構成されるマルチプロセッサであって、前記ユニットチップは、複数のプロセッサコアと、複数のメモリと、前記プロセッサコアと前記メモリとチップ外部との接続関係を設定する構成制御部と、前記プロセッサあるいは前記メモリあるいは前記構成制御部と、積層接続される他のユニットチップとのトランザクションを伝送するチップ接続部とを有する構成とし、前記チップ接続部は当該ユニットチップの辺部に回転対称に配設され、積層構成される前記ユニットチップのいずれかのユニットチップが回転接続されるようにした。

(もっと読む)

システム・オン・チップ(SoC)用の周辺構成部分相互接続(PCI)互換のトランザクション・レベル・プロトコルを提供する方法

【課題】システム・オン・チップ(SoC)システムにおいて、PC互換を実現する方法を提供する。

【解決手段】PCIベースのシステムAXI/OCP技術などの異種リソースの使用を可能にするため、PC互換SoC構成部分のトランザクション・レベルのモジュラーな相互接続を行う。SoC構成部分の仕様の規定の物理レベルからトランザクション・レベルを分離することが可能であるので、PCI(又は他のバスベースの)システムをポイントツーポイント(PtP)相互接続システムにマッピングするための機能、ターゲットベースの復号化をPtP相互接続するための機能、及び、PC互換システムにおいて、ターゲットベースの復号化及び他のPC互換機能をロジックを介して実現する。

(もっと読む)

受領信号の形成装置

【課題】従来技術の欠点を低減するために受領信号を形成する装置および方法を提供することである。

【解決手段】受領信号の形成装置であって、プロセッサは、プロセッサクロック信号によりクロッキングされ、中断命令に基づいて静止状態からウェークアップされ、動作状態において前記中断命令を処理し、該中断命令の処理後または該中断命令の処理中に、プロセッサクロック信号に同期する受領信号を形成し、少なくとも1つの周辺機器は、前記プロセッサクロック信号には非同期で経過する周辺機器クロック信号によりクロッキングされ、前記中断命令を周辺機器クロック信号に同期して前記プロセッサに送信し、第1の論理回路は、プロセッサクロック信号に同期する受領信号から周辺機器クロック信号に同期する受領信号を形成し、該同期する受領信号により周辺機器に対して、中断命令が処理されたことが通知される、ことを特徴とする。

(もっと読む)

半導体集積回路及びそれを備えた電子機器

【課題】半導体集積回路における一の入力端子をシリアル受信及び外部割り込みに兼用可能にする。

【解決手段】半導体集積回路(10)は、CPU(12)と、シリアル通信データ信号及び外部割り込み信号に共通の入力端子(11)と、CPU(12)にシリアル受信割り込み又は外部割り込みを通知する割り込み通知部(15)とを備えている。割り込み通知部(15)は、入力端子(11)を介して入力された外部信号からデータフレームが検出できたか否かに基づいて、CPU(12)に割り込み通知を行う。

(もっと読む)

1 - 20 / 53

[ Back to top ]