Fターム[5B065CE07]の内容

外部記憶装置との入出力 (22,430) | アクセス−データ転送 (1,638) | DMA転送、バースト転送 (31)

Fターム[5B065CE07]に分類される特許

1 - 20 / 31

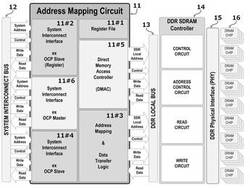

マルチCPUコア・プロセッサ用DMAC付きDRAMアドレス・マッピング回路

【課題】CPUシステム(PC,TabletPC,PDA etc.)において、CPUコアもしくはOSが32bitであると主記憶サイズは4GB以下の3.5GB程度に制約される。 現状4GB(3.5GB)を超えて搭載したメモリーは無駄となる。 また、実行速度改善に効果がある現在のRAMDISKは主記憶を使う為、主記憶サイズの制限は、32bitシステムでの性能向上の足かせとなっている。

【解決手段】DRAMのローカル・アドレスをシステム物理アドレスにマッピングする回路にDMA機能を持たせる事により、主記憶に割り振れなかったDRAM領域をRAMDISKとして経済的に使用し、かつ、それに関わるデータ転送をDRAMのローカルバス上で局所的に行う事で、従来の主記憶を使ったRAMDISKより、実行効率の良いRAMDISKを供給する。

(もっと読む)

拡張メモリ付きハイブリッドドライブ、及び拡張メモリ付きハイブリッドドライブを備えた記録再生装置

【課題】光ディスクドライブと不揮発性メモリを組み合わせた拡張メモリ付きハイブリッドドライブにおいて、不揮発性メモリへのデータ転送上の制限を緩和して、拡張メモリ付きハイブリッドドライブの利便性を高めること。

【解決手段】光ディスクドライブと不揮発性メモリを組み合わせた拡張メモリ付きハイブリッドドライブ100において、光ディスク制御部10に拡張バスI/F30を設けて拡張バス35により不揮発性メモリ装置40を接続すると共に、ホストI/F13との間を拡張バス35で接続する。ホスト機器50側からのデータを拡張バスI/F30経由で不揮発性メモリ42に転送可能として、バッファメモリ14側のデータ転送要件に左右されない利便性の高い拡張メモリ付きハイブリッドドライブを提供する。

(もっと読む)

データ処理装置、及びデータ処理方法

【課題】パフォーマンスの低下を抑止する。

【解決手段】記憶媒体とデータを送受信する際に、当該記憶媒体のセクタ長以上のデータサイズ単位でデータの送信を制御するSDホスト106と、複数のファイルのデータサイズを認識する認識部109と、複数のファイルのうち、セクタ長よりデータサイズが小さいファイルが含まれていた場合に、データサイズ単位で当該小さいファイルを送信する際の冗長データのサイズに基づいて、セクタ長以上のデータサイズ単位で送信するか否かを判定する判定部108と、送信しないと判定された場合、セクタ長より小さいファイルをSDホスト106が送信する際、当該ファイルのデータサイズに基づいて送信するデータサイズ単位を調整する調整部111と、を備える。

(もっと読む)

シリアル・アドバンスド・テクノロジー・アタッチメントの性能を改善するための方法および装置

【課題】SATAターゲットデバイスとの通信の性能を改善するための方法および装置を提供する。

【解決手段】方法は、DMA ACTIVATEフレーム情報構造(FIS)の受領に関係なく、ストレージコントローラからSATAターゲットデバイスへの継続したDMA転送を提供する。このためのロジックは、拡張SAS/STPイニシエータと連結された拡張SASエキスパンダ内のブリッジロジックによって提供され、または拡張SATAターゲットデバイスと直接連結された拡張SATAホスト内の適切なロジックによって提供され得る。FISの受領に関係なく、イニシエータ/ホストからSATAターゲットデバイスへのデータの継続したDMA転送によって、SAS/SATA通信リンクの利用可能な、より多くの帯域幅を利用することができる。

(もっと読む)

ハイブリッドドライブ装置

【課題】光ディスク装置とフラッシュメモリ等の高速アクセス可能なメモリを組み合わせたハイブリッドドライブ装置において、より大容量の高速アクセス可能なメモリを追加出来る拡張メモリ付きハイブリッドドライブ装置を提供すること。

【解決手段】光ディスク装置と、該光ディスク装置の制御部50に接続された高速アクセス可能なSDRAMとを有するハイブリッドドライブ装置において、インターフェース変換回路20を介して大容量メモリ30を追加する。インターフェース変換回路20は、FPGAを用いたSDRAM−eMMC Brigeであり、大容量メモリ30のアドレスは、大容量メモリアドレス指定用レジスタによって指定される。

(もっと読む)

DMAセキュリティチェック回路及びDMAセキュリティチェック方法

【課題】IO TLB(I/O Translation Look aside Buffer)でキャッシュミスした場合にDMAが待たされることを防止する。

【解決手段】IOV(I/O Virtualization) HBA(Host Bus Adapter)に対応したDMA(Direct Memory Access)セキュリティチェック回路が、HBAからのDMAリード要求に対しディスクリプタフェッチを検知した場合に、当該DMAリード要求のリプライデータの中から抽出した論理アドレスと、当該リプライデータに含まれるリクエストIDとが同じゲスト空間のものであるかを判定し、同じゲスト空間のものである場合に当該リプライデータに含まれるアドレスが適切であると判断する。

(もっと読む)

情報処理装置

【課題】メインメモリと周辺装置との間でデータを転送すること。

【解決手段】メインメモリ130を具備する中央処理装置100と、PCI Expressカード260〜263及びローカルメモリ230を具備する入出力処理装置200とを備え、入出力処理装置200は、PCI Expressカード260〜263からメインメモリ130に対して直接データ転送を行う第1の経路と、PCI Expressカード260〜263又はメインメモリ130からローカルメモリ230に一度データ転送した後、メインメモリ130又はPCI Expressカード260〜263にデータ転送を行う第2の経路とを有する。

(もっと読む)

同時データ操作が可能なDMAエンジン

【課題】DMAコントローラ/エンジンによって管理される直接メモリアクセス(DMA)・チャネルを介して転送されるデータ上で、複数のデータ操作オペレーションを同時に実行するための方法およびデバイスを提供する。

【解決手段】DMAコントローラ内部で動作する制御データブロック(CDB)プロセッサは、CDBを読み出し、CDBの内容に従ってデータの読み出し、データ操作オペレーションおよびデータの書き込みを設定してもよい。データがDMAコントローラを通して導かれる間に、例えばハッシング、HMAC、フィルパターン、LFSR、EEDP検査、EEDP生成などの複数のデータ操作オペレーションをデータ上で同時に実行してもよい。データ操作オペレーションを実行するデータ変更エンジンは、データ操作オペレーションの間に外部メモリへのアクセスを回避するために局所RAMを使用する、DMAコントローラ上で実施されてもよい。

(もっと読む)

インターフェース回路、ホスト装置、スレーブ装置、および不揮発性記憶システム

【課題】不揮発性記憶装置への書き込みデータバーストが不揮発性メモリのページ境界をまたぐとき、効率よく書き込みを行うために追加のバッファが必要となる。

【解決手段】ホスト装置は不揮発性記憶装置のインターフェースバッファに格納できるセクタ数を取得し、データバースト内のDATAパケット数NDBを決定する。続いてホスト装置は、最初のDATAパケットから、Write先セクタアドレスがNDBの倍数である直前のDATAパケットまでで第1データバーストを構成する。

(もっと読む)

DMAコントローラ及びその制御方法

【課題】従来のDMAコントローラは、効果的なデータ転送の最適化を行うことができないという問題があった。

【解決手段】本発明にかかるDMAコントローラは、外部メモリ11とバス9を介して接続された複数のDMA部40−0〜40−mが実行するデータ転送を制御するDMAコントローラであって、DMA部40−0〜40−mからのデータ転送の要求に対してバス9の調停を行う調停回路12と、複数のDMA部40−0〜40−mのうち選択されたいずれか一つのDMA部と、外部メモリ11と、の間において転送される転送データのバースト長を当該転送データのデータ転送間隔に基づいて制御するバス観測回路13と、を備える。このような回路構成により、効果的なデータ転送の最適化を行うことができる。

(もっと読む)

情報処理システム及びデータ転送方法

【課題】初期アクセスレイテンシによるデータ処理速度の低下を低減するとともに無駄なメモリアクセスの発生しない情報処理システムを提供する。

【解決手段】情報処理システムは、連続する複数回のデータ読み出し命令を出力する際に転送状態信号を合わせて出力し、ある1つのデータ読み出し命令に対して少なくとも1つのデータ読み出し命令が後続することを転送状態信号により示すマスタモジュールと、上記ある1つのデータ読み出し命令と転送状態信号とをマスタモジュールから受信すると、転送状態信号に応答して、上記ある1つのデータ読み出し命令に後続する少なくとも1つのデータ読み出し命令に対応するデータをメモリから読み出して保持するとともに、上記ある1つのデータ読み出し命令に対応するデータをマスタモジュールに供給するメモリコントローラを含むことを特徴とする。

(もっと読む)

データ転送装置、データ転送制御方法、データ転送制御プログラム及び記録媒体

【課題】本発明は、外部へのデータ送出に必要なデータ転送を効率的に行うデータ転送装置、データ転送制御方法、データ転送制御プログラム及び記録媒体に関する。

【解決手段】画像処理装置1は、CPU2が、バンドサイズレジスタ23の保持するバンドサイズに応じたディスクリプタd1〜dnとディスクリプタd1〜dnのバンドサイズに分割したデータD1〜Dnをメインメモリ4に書き込み、DMAコントローラ13が、メインメモリ4のディスクリプタd1〜dnを読み取って該ディスクリプタd1〜dnに応じてメインメモリ4のデータD1〜Dnをネットワークコントローラ12にDMA転送し、ネットワークコントローラ12からネットワークNWへデータ送出するデータ送出性能に対するDMA転送性能の適否を転送状況監視部21で判定して、ダミーディスクリプタ生成部22がバンドサイズレジスタ23にDMA転送のバンドサイズを設定する。

(もっと読む)

ストレージ装置、及びデータ保証方法

ストレージ装置のチャネル制御部に、I/O要求とともにホストコンピュータとの間で送信又は受信する可変長形式データについてのデータ転送を行う可変長DMA(Direct Memory Access)、キャッシュメモリとの間で固定長形式データのデータ転送を行う固定長DMA、及び可変長DMAと固定長DMAとの間に介在するバッファを設け、固定長DMAは、キャッシュメモリへの固定長形式データのデータ転送に際し、可変長形式データをキャッシュメモリにおけるデータの取り扱い単位に対応したデータサイズの複数の固定長形式データに分割し、当該分割により生成される固定長形式データの末尾の固定長形式データに、可変長形式データの全体に基づいて生成した第1の保証コードを付加するようにする。 (もっと読む)

情報処理装置及び画像データ記録システム

【課題】I/Oバッファに対するDMA転送を高速化することができる情報処理装置及び画像データ記録システムを提供すること。

【解決手段】本発明の情報処理装置1は、内部バス40と、転送元リソースから転送先リソースにデータ転送を行うDMAコントローラー20と、FIFO320(I/Oバッファ)を含み、FIFO320と外部デバイス100の間のデータ転送を行うI/Oコントローラー30と、を含む。DMAコントローラーは、転送元リソースがI/Oコントローラーである場合は、I/Oコントローラーからの1回のデータ転送要求に対して、FIFO320から複数のデータを連続して読み出すか1つのデータを読み出すかを選択し、転送先リソースがI/Oコントローラーである場合は、I/Oコントローラーからの1回のデータ転送要求に対して、FIFO320に複数のデータを連続して書き込むか1つのデータを書き込むかを選択する。

(もっと読む)

データストレージシステム

【課題】複数の記憶デバイスを制御する複数の制御モジュールを有するストレージシステムに関し、制御モジュールの数が増加しても、低レンテシイな応答を維持しつつ、実装構成を容易とする。

【解決手段】複数の記憶デバイス(2−0〜2−35)を並列接続したエンクロージャを、バックエンドルータ(5−0〜5−7)で、各制御モジュール(4−0〜4−7)の第2のインターフェース(42)に接続し、全ての制御モジュールが、全ての記憶デバイスにアクセスできる冗長性を維持する。且つ制御モジュールと第1のスイッチユニットとをバックパネル(7)で、インターフェースを構成する信号数が少ないシリアルバスで接続する。これにより、プリント基板での実装が可能となる。

(もっと読む)

制御装置、制御方法、及びプログラム

【課題】ミラーリングシステムを構成する記憶装置として、データアクセス性能が異なるものが装着された場合でも、ミラーリングシステムとしてのデータアクセススピードの低下を抑えること。

【解決手段】RAIDコントローラ111は、特定データを受信した場合に、該特定データをHDD1に設けられた第1記憶領域及びHDD2に設けられた第2記憶領域の双方に書き込み、前記第1記憶領域及び前記第2記憶領域のアクセススピードを取得し、該取得されたアクセススピードに基づいて、前記アクセススピードが高い記憶装置を選択して前記特定データを読み出す構成を特徴とする。

(もっと読む)

インタフェースコントローラ

【課題】1つのリクエストに対して複数のレスポンスパケットが発生するメモリアクセスにおいて、インタフェースコントローラの受信バッファのオーバーフローを回避する。

【解決手段】インタフェースコントローラ101は、リクエストパケットをメモリに出力するパケット生成手段101Cと、受信バッファに記憶されたレスポンスパケットから所定のプロトコルに従ってレスポンスを生成し、前記レスポンスを前記ホスト装置に出力するプロトコル生成手段101Fと、前記ホスト装置によって発行されたリクエストの最大分割数を算出する最大分割数算出手段101Aと、前記最大分割数算出手段によって算出された最大分割数、処理済リクエストの最大分割数及び処理済レスポンスの最大分割数に従って、前記ホスト装置にリクエスト発行許可を行うリクエスト発行制御手段101Bと、を備える。

(もっと読む)

データ転送装置、半導体集積回路、および処理状況通知方法

【課題】プロセッサの処理負荷を軽減するとともにデータ転送以外の処理によるバスの占有率を減少させ、迅速にデータ転送を実行すること。

【解決手段】リクエスト受付部423aは、複数のDMA回路421それぞれから送信される転送実行のリクエストを受け付ける。転送可能フラグ423bは、複数のDMA回路421それぞれに対応するフラグを備えており、転送実行のリクエストを送信したDMA回路421に対応するフラグをセットする。通知データ生成部423cは、転送可能フラグ423bを常時監視しており、いずれかのDMA回路421に対応するフラグがセットされると、転送可能DMA情報およびすべてのDMA回路421の状態情報をCPU43へ通知するための通知データを生成する。状態情報収集部423dは、すべてのDMA回路421から状態情報を収集する。

(もっと読む)

データ入出力装置

【課題】データ転送の処理時間とメモリ利用効率とを大幅に向上させる。

【解決手段】DMAを有するデータ入出力装置において、DMA転送に最適なデータバッファ作成サービスを準備し、プログラムを構成する階層化された各システムでこのデータバッファ作成サービスを利用しデータバッファを作成することにより、DMA転送によってDMAに接続されるデバイスから最上位のアプリケーションまでのデータ転送を直接行う。

(もっと読む)

データ処理システム内でシステム・イメージとローカルに接続された外部記憶装置との間の動作を実行するための方法、コンピュータ・プログラム、および装置(キャッシュされたアドレス変換を使用して入出力アダプタと通信するための装置および方法)

【課題】 キャッシュされたアドレス変換を使用して、ローカルに接続された入出力装置と通信するように構成された入出力(I/O)アダプタと通信するための装置および方法を提供することにある。

【解決手段】 この装置および方法により、記憶トランザクション要求を受信したことに応答して、未変換バッファ・アドレスを指定するキュー・エレメントがコマンド・キュー内に作成される。キュー・エレメントは入出力アダプタによって検索することができ、キュー・エレメントが読み取り動作コマンドを含むかどうかに関する判断を行うことができる。キュー・エレメントが読み取り動作コマンドを含む場合、読み取り動作コマンドがローカルに接続された外部記憶装置に送信されるのとほぼ同時に、入出力アダプタからルート複合体に変換要求を送信することができる。キュー・エレメントの未変換アドレスに対応する変換済みアドレスは、外部記憶装置から読み取られたデータを受信する前に、返され、入出力アダプタに保管することができる。

(もっと読む)

1 - 20 / 31

[ Back to top ]