Fターム[5B077BA01]の内容

情報転送方式 (3,847) | 処理装置間の情報転送 (462) | 共用メモリを介した転送 (28)

Fターム[5B077BA01]に分類される特許

1 - 20 / 28

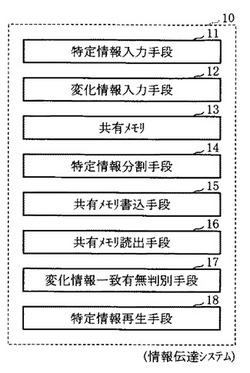

情報伝達システムおよび情報伝達方法

【課題】共有メモリを使用し、しかも送信側が共有メモリに書き込んだという情報を受信側に伝達する必要なく受信側が最新の情報を得ることのできる情報伝達システムおよび方法を得る。

【解決手段】情報伝達システム10は時間的に変化する可能性のある特定情報を入力する時点で、その度に内容の変化する情報としての変化情報を変化情報入力手段12で共有メモリ13に書き込み、この同一の情報を挟む形で、分割した特定情報を共有メモリ13に書き込む。受信側ではこれら1セットの最新情報を共有メモリ13から読み出し、1対の変化情報が一致すれば読み出した特定情報を最新の情報として採用する。一致しなければ一致するまで同様の処理を繰り返す。

(もっと読む)

データ形式変換装置、電子システム、データ形式変換方法及びプログラム

【課題】ソフトウェアの変更やエミュレーション機能の使用を必要とせずに、第1のデータ形式と第2のデータ形式の互換性を実現することを目的とする。

【解決手段】第1装置と第2装置とで通信されるデータを中継するデータ形式変換装置であって、第2装置で用いられる第2のデータ形式が、第1装置で用いられる第1のデータ形式よりも、データを扱う際の最小単位のサイズが大きい場合、第1装置から第2装置に対して送信されたデータを第1装置から受信すると、受信したデータを第1のデータ形式から第2のデータ形式に変換し、変換したデータを第2装置へ送信し、第2装置から第1装置に対して送信されたデータを第2装置から受信すると、受信したデータを第2のデータ形式から第1のデータ形式に変換し、変換したデータを第1装置へ送信する。

(もっと読む)

モニタ回路、バスブリッジ及びバスシステム

【課題】マスタの数に応じたバスブリッジの設計変更を行うことなく、データの一貫性を保証可能なバスシステムを提供する。

【解決手段】入力されるモニタ起動信号からカウンタ起動信号を生成する起動制御回路と、カウンタ起動信号により起動されて、バスブリッジから転送が1つ発行されたことを示すブリッジ転送完了信号を用いて発行された転送の数をカウントし、起動時にブリッジ内停滞転送数信号により示されるバスブリッジ内に停滞する転送数の転送が発行されたときにカウント完了信号を出力するカウンタ回路と、カウンタ回路からカウント完了信号を受けてモニタ完了信号を出力する完了制御回路とを有するモニタ回路をバスシステムの構成に合わせて接続し、バスブリッジにアクセスするマスタの数に応じてバスブリッジの設計変更を行うことなく、任意のバスシステムにおいてデータの一貫性を保証可能にする。

(もっと読む)

エンドポイント共有システムおよびデータ転送方法

【課題】サーバと記憶装置をPCIeで接続し、複数のサーバの中の特定のサーバと統合エンドポイントの間のデータ転送の高速化を図ったエンドポイント共有システムおよびデータ転送方法を得ること。

【解決手段】統合エンドポイントにおける所定のエンドポイントから現用系の主サーバにPCIeパケットが送信されると、このパケットを処理するサーバが決定され、そのサーバ名がPCIeパケットに挿入される。2次共有メモリ転送手段16は、サーバとの間のデータの個別伝送に使用する2次共有メモリのうちの該当するものに転送する。サーバ側から統合エンドポイントへのデータの転送も行われる。

(もっと読む)

情報処理システム

【課題】データ転送時に発生するデータの書き込み完了通知及びデータの読み出し完了通知を抑制する。

【解決手段】情報処理システム90には、情報処理装置1、情報処理装置2、及び共有部3が設けられる。情報処理システム90では、情報処理装置1及び情報処理装置2の間の共有部3に設けられる共有メモリ31を介して、情報処理装置1と報処理装置2の間のデータ転送を行っている。連続したデータ転送の場合、データ転送が終了後或いは所定回数のデータ転送が終了後に転送データの完了通知が送信される。

(もっと読む)

半導体記憶装置

【課題】データ転送時に自身が備えるCPUにかかる負荷を可及的に低減した半導体記憶装置を提供すること。

【解決手段】NANDコントローラ3が単位サイズのデータをRAM2へ書き込む毎に終了通知を直接ATA I/Fコントローラ1に出力し、ATA I/Fコントローラ1が、終了通知を受信する毎に、CPU4により作成されたRAM2のデータのアドレスが転送順に指定されているディスクリプタにしたがってデータをRAM2から読み出してホスト装置200に転送する。

(もっと読む)

データ転送制御装置、データ転送制御方法、光ディスク装置

【課題】リソースへのアクセス要求が発生していない状態でも、最低必要なアクセスバンド幅を維持するデータ転送制御装置および方法を提供する。

【解決手段】リソース転送バス(20)の状態が“待機中”であることを空時間監視部(7)が検知すると(ST10でNo)、分割転送指示部(6)は、単位時間(T)に必要なデータ転送量(M)の転送完了時間を分割なし(T0),分割あり(T1)のそれぞれの場合について予測し(ST20,ST30)、その結果に応じて分割転送指示(21,22,23)をマスタ(1,2,3)に与える(ST40,ST50)。分割転送指示(21,22,23)を受けたマスタ(1,2,3)は、その時点で蓄積されているデータを共有リソース(5)へ転送し(分割転送)、その後は平均転送レート(TR1)にて共有リソース(5)へのデータ転送を実行する。これにより、単位時間(T)内に所定量(M)のデータをリソース(5)に転送できなくなる事態を防ぐことができる。

(もっと読む)

データ転送システム

【課題】共有メモリを介して行うデータ転送において、遅延時間や処理待ち時間を低減して高速なデータ転送を実現するデータ転送システムを得ること。

【解決手段】本発明にかかるデータ転送システムは、マルチコアCPUまたはマルチプロセッサに対して仮想化技術を適用した送信装置(1)および受信装置(2)と、送信装置(1)および受信装置(2)からアクセス可能な記憶装置(3)と、を備え、受信装置(2)宛のデータが発生した場合、送信装置(1)は、受信装置(2)宛のデータをデータ格納部(33)に格納し、次に、データ格納済領域を示すデータ保持領域情報を未処理リスト格納部(32)に格納し、その後、データ格納処理が完了した旨を示す通知を受信装置(2)へ発行し、受信装置(2)は、通知を受けた場合、未処理リスト格納部(32)内のデータ保持領域情報に基づいて、データ格納部(33)から自身宛のデータを読み出す。

(もっと読む)

データ交換システム

【課題】コモンメモリが無駄に大きくなることを抑えて効率的なデータ交換ができる。

【解決手段】ブロック割付け手段(1A,1B)は、自装置のコモンメモリ2上に確保する送信領域のワードサイズを共通のものとしてブロック単位に割付けておく。送信ノードグループ決定部1Dはシステムに結合されているノード群を複数のグループに分け、このグループ別にコモンメモリの各送信領域を1対1に対応付け、同じグループに属するノード群のうち、どのノードから送信領域に送信できるかを決定しておく。送信ブロック番号決定部1Eは自ノードがコモンメモリ送信処理において送信するブロック番号を決定する。受信処理部1Fは、コモンメモリ上の各ブロックを、どのノード番号から受信するかを設定し、当該ノード番号をもつノードからの送信データを当該ブロックに受信する。

(もっと読む)

情報処理システム

【課題】非同期での通信が可能で、かつ、接続経路の変更が容易な情報処理システムを提供する。

【解決手段】情報処理システム1Aは、情報が読み書き可能に記録される記憶部2Aと、記憶部2Aに接続される複数の機能基板3Aを備える。情報の転送元となる機能基板3Aは、記憶部2Aの未使用領域を確保して、記憶部2Aにデータと転送先情報を送信して記録する。記憶部2Aに接続された各機能基板3Aは、任意のタイミングで転送先情報を検索し、自機宛の転送先情報が記録されていると、記憶部2Aからデータを受信する。

(もっと読む)

回路間データ転送方法およびシステム

【課題】運用中にアドレス接続正常性の検証を可能とする回路間データ転送方法およびシステムを提供する。

【解決手段】回路5,6間でメモリ3を介してデータ転送を行う際に、メモリ3の転送用領域に書き込まれる転送データに所定アドレスカウント間隔で誤り訂正可能なエラービットを書き込み、メモリ3の転送用領域から読み出された転送データからエラーが検出されるアドレスカウント間隔を監視し(S504)、エラー検出間隔の異常を判別することで転送の正常性を検証する(S507、S508)。

(もっと読む)

バス制御装置

【課題】ポステドライト方式を使用した場合であっても、ハードウエア実装の面で複雑な回路を用いず、かつソフトウエアの面でも簡単な処理で、書き込みデータのコヒーレンシを保つバス制御装置を提供すること。

【解決手段】バス制御装置1は、バス14を介して、メモリ15に対してデータを書き込むためのライトコマンド信号を出力する複数のブロック13と、各ブロック13に対応して設けられたバス接続制御部16とを含む。バス接続制御部16は、バス14とブロック13との間の信号を監視して、ブロック13の要因レジスタのデータを読み出すためのリードコマンド信号を検出すると、ブロック13とバス14との間の信号線の接続を遮断し、メモリ15へのダミーリードコマンド信号を出力し、かつ、ダミーリードコマンド信号に対するレスポンス信号を受信すると遮断を解除する。

(もっと読む)

データ処理システム内で第1のホスト・システムと第2のホスト・システムとの間で通信するための方法、プログラム、およびシステム(ソケット接続および共用メモリを使用するホスト・システム間の通信のためのシステムおよび方法)

【課題】 ソケット接続および共用メモリを使用するホスト・システム間の通信のためのシステムおよび方法を提供することにある。

【解決手段】 このようなソケット・ベースの通信では、ホスト・システム内の作業キューを使用して、着信ソケット初期設定要求を聴取することができる。第2のホスト・システムとのソケット通信接続を確立することを希望する第1のホスト・システムは、その作業キュー内にソケット初期設定要求作業キュー・エレメントを生成することができ、そのソケット初期設定要求作業キュー・エレメントが処理のために使用可能であることを第2のホスト・システムに通知することができる。その後、第2のホスト・システムは、その要求を受諾または拒否することができる。第2のホスト・システムがその要求を受諾する場合、そのホスト・システムは、第1および第2のホスト・システム間でソケット・ベースの通信を実行する際に第1のホスト・システムによって使用するためのソケットのパラメータのうちの後半部分を返す。

(もっと読む)

情報処理装置およびインターフェイス回路

【課題】バスマスタがレジスタ等の周辺モジュールをアクセスする際のレイテンシを有効に低減する情報処理装置及びインターフェイス回路を提供すること。

【解決手段】第1クロック信号に同期して動作するバスマスタ(1100)と、第2クロック信号に同期して動作する周辺モジュール(1200)と、前記第1クロック信号に同期して前記バスマスタとの間でデータ転送するための第1アクセスポートと前記第2クロック信号に同期して前記周辺モジュールとの間でデータ転送するための第2アクセスポートとを有する記憶手段としてデュアルポートRAM(1210)を有し、該デュアルポートRAMを介してバスマスタ(1100)と周辺モジュール(1200)との間のデータ転送を遂行する。

(もっと読む)

情報処理装置、データ転送方法及びプログラム

【課題】I/Oデバイスに対するデータ転送を直ちに開始させることができ、且つデータ転送性能を安定的に発揮することができる情報処理装置を提供すること。

【解決手段】メモリ14の論理アドレスを物理アドレスに変換するアドレス変換テーブルをメインプロセッサ14及びサブプロセッサ24の間で共有するためのハードウェアを備えた情報処理装置において、サブプロセッサ24の1つを、メモリ14の論理アドレスを指定した転送要求を受け付ける手段、共有された前記アドレス変換テーブルを用いて、前記転送要求において指定された論理アドレスを物理アドレスに変換する手段、及び変換された物理アドレスに従ってメモリ14に格納されたデータの転送処理を実行する手段として機能させる。

(もっと読む)

USB装置、印刷装置、USB装置の制御方法及びプログラム

【課題】USB転送において、処理を簡略化してより迅速に情報の入出力を行うことができる。

【解決手段】プリンタ20は、USBデバイスを接続可能な固定接続ポート(ポート1,3)に固定的に接続されたカードリーダ42及び内蔵ドライブ48に応じた情報を記憶する領域が共有メモリ49上に予め固定確保されており、固定接続ポートのUSBデバイスから読み出した情報を固定確保された領域へ格納したり、固定確保された領域に格納された情報をこれらのUSBデバイスへ出力したりする。共有メモリ49には、USBクラスの種別に応じたエンドポイントの情報を記憶する領域が予め固定確保されている。また、共有メモリ49には、エンドポイントの種別に応じた記憶容量の領域が予め固定確保されている。汎用ポート(ポート2)にUSBデバイスが接続されたときには、これに必要な領域を共有メモリ49に動的確保する。

(もっと読む)

CPU間のデータ転送方式

【課題】両CPU側のソフトウェアの処理を削減し、かつ、データの同時性を保証し、データ転送の高速性を確保する。

【解決手段】CPU1,2は、デュアルポートメモリ5内に設定する2つのデータ転送エリアA,Bに対するデータ書き込みおよび読み出しを交互に切り替える。書き込みエリア選択信号生成回路6A,6BはCPUの書き込み中フラグと、読み出し中フラグから、データ書き込み中の書き込みエリア選択信号を生成する。CPUは、書き込みエリア選択信号から相手側CPUがデータ書き込み中でないエリアを判別し、データ読み出しを行う。

書き込みエリア選択信号、書き込み中フラグおよび読み出し中フラグを基に、両CPUによるデータ書き込みおよびデータ読み出しを行うエリアのアドレスを制御するマルチプレクサ回路を設けることも含む。

(もっと読む)

プロセッサ間通信方法

【課題】疎結合マルチプロセッサ構成の制御装置におけるプロセッサ間通信方法において、プロセッサ間で大量のデータを高速に通信することを可能にする。

【解決手段】プロセッシングユニット(PU)間の転送データをローカルメモリLMに書き込むことで、共有メモリSMに対するアクセスのオーバヘッドをなくし、転送データの書き込みが完了してから、プロセッサ1aのブロック転送命令あるいはDMAで、転送元ローカルメモリLMから共有メモリSMへまとめて転送を行うことで、大量データの高速転送を実現する。転送データの書き込み完了は、OS等が持っている解放系同期基本操作を行ったタイミングでそれとみなす。次に、転送データの読み込みに先立って、プロセッサ1aのブロック転送命令あるいはDMAで、共有メモリSMから転送先ローカルメモリLMにまとめて転送を行う。転送データの読み込み開始は、OSの獲得系同期基本操作を行ったタイミングでそれとみなす。

(もっと読む)

伝送装置、伝送システムおよび更新データの排他制御方法

【課題】アクセスに待ち時間を発生させることなく、更新中のバッファを管理するための制御を簡略化し、低いコストで実現する伝送システムを提供する。

【解決手段】伝送装置1は、計算機5とのインタフェースを司るシステムバスインタフェース11と、LAN9とのインタフェースを司る通信インタフェース12とが接続される内部バス16と、共有メモリ14が接続されるメモリバス17との間にあって、少なくとも共有メモリ14に割り付けられた伝送装置毎のエリアと等容量のサイズを持ち、内部バス16のバスアクセス調停の結果、バスマスタになるシステムバスインタフェース11もしくは通信インタフェース12を介して行われるメモリアクセスと、メモリバス17を介して行われる共有メモリ14に対するデータ転送と、を非同期に行うデュアルポートメモリ150、を持つ。

(もっと読む)

データ・トランスファー装置とその方法,及びそのコンピューター・ラピッド起動方法

【課題】データ・トランスファー装置はコンピューターのチップセットとのデータ・トランスファーをする、データ・トランスファー装置とその方法を提供する。

【解決手段】データ・トランスファー制御ユニット、第1の格納装置と第2の格納装置を含んでなり、チップセットと第1の格納装置との間にデータを伝送する時に、データ・トランスファー制御ユニットにより目的地が全ての伝送したデータを受信できるかどうかを判断してもよいが、もしできれば、目的地から全てのデータを直接的に受信し、さもないとまず目的地にてデータの一部を受信し、そして残りのデータを予め第2の格納装置に格納し、目的地により前のデータを一つ受信してしまった後に、さらに第2の格納装置に格納されたデータを目的地に伝送して受信する。

(もっと読む)

1 - 20 / 28

[ Back to top ]