Fターム[5B077DD00]の内容

情報転送方式 (3,847) | 情報転送におけるバッファ (524)

Fターム[5B077DD00]の下位に属するFターム

バッファの種類 (285)

バッファ内のデータ量管理 (150)

バッファのエリア管理 (72)

Fターム[5B077DD00]に分類される特許

1 - 17 / 17

推測的技術を用いるメッセージベースのネットワークインターフェースのためのプロセッサ

【課題】メッセージネットワークインターフェースユニットを提供すること。

【解決手段】メッセージネットワークインターフェースユニットは、プロセッサに連結されており、プロセッサがプロセッサによって生成された複数のメッセージをハードウェアユニットに送信することを可能にし、メッセージネットワークインターフェースユニットは、プロセッサによって生成された複数のメッセージのうちの少なくもと1つのメッセージの引数を格納するように動作可能な伝送レジスタであって、少なくとも1つのメッセージが推測的に生成される、伝送レジスタと、伝送レジスタに連結されており、複数のメッセージをキューに入れるように動作可能なキューであって、動作は、メッセージネットワークインターフェースユニットがトリガーメッセージを受信することに応じてキューにおいて実行される、キューとを含む。

(もっと読む)

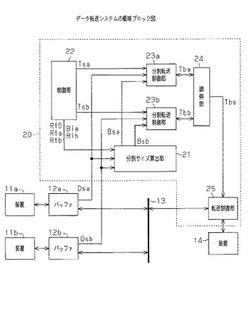

データ転送装置及びデータ転送方法

【課題】データ転送時の待ち時間を減らすこと。

【解決手段】データ転送装置20の分割サイズ算出部21は、各バッファ12a,12bの分割サイズBsa,Bsbを、互いに他のバッファのデータ蓄積量に基づいて算出する。例えば、バッファ12bのデータ蓄積量Dsbに基づいて、バッファ12bにしきい値Bib以上のデータが蓄積されるまでのデータ蓄積時間を予測し、そのデータ蓄積時間に応じて、バッファ12aから転送するデータの分割サイズBsaを算出する。分割転送制御部23a,23bは、分割サイズBsa,Bsbとデータ蓄積量Dsa,Dsbに応じて、各バッファ12a,12bに対する転送指示Tba,Tbbを発行する。転送制御部25は、転送指示Tbs(転送指示Tba,Tbb)に応じて、各バッファ12a,12bから装置14にデータを転送する。

(もっと読む)

データ転送制御装置、データ転送システム、及びデータ処理システム

【課題】記憶資源を効率的に使用する。

【解決手段】各々が転送されたデータを転送された順に処理する画像処理部(第1〜第4画像処理部11〜14)の各々に対応させて設けられデータを一時的に記憶するための複数の中間バッファ32と、各々が画像処理部の各々に対応するように定められた互いに重複しない複数の記憶領域を備えた単一の記憶装置50の記憶領域から予め定められた順にデータを読み出し上記対応させて設けられた中間バッファ32に書き込む複数のDMA制御部33と、各々が画像処理部の各々に対応させて設けられ対応する画像処理部からの要求に応じて該画像処理部に対応する中間バッファ32に書き込まれたデータを書き込まれた順に読み出して対応する画像処理部に転送する複数の画像処理部I/F31と、複数のDMA制御部33の各々に対して排他的に記憶装置50からデータを読み出す権利を付与して排他制御を行う排他制御部40とを設ける。

(もっと読む)

データ受信システムおよび割り込み実行方法

【課題】複数のデータ出力装置からの非同期の割り込み要求信号を欠落なく、効率的に確実に、データ受信装置に、任意のタイミングでデータを送信するデータ受信システムおよび割り込み実行方法を提供する。

【解決手段】複数のデータ出力装置から非同期で割り込み要求もしくはデータを受信するデータ受信システムにおいて、データ出力装置からの割り込み要求信号を検出し、CPUに割り込み信号を送信する割り込み発生回路部と、データ出力装置から受信データを取得した複数のデータを一時的に保持するデータバッファ部と、割り込み発生回路部からの割り込み信号を受信した際に全てのデータ出力装置に対してデータが入力されているか否かを判断し、入力されているデータを順次受信する割り込みルーチンと、全てのデータ受信が終了した場合に割り込みリセットを実行するCPUを有するデータ受信システムを提供する。

(もっと読む)

情報処理装置、情報処理方法および情報処理プログラム

【課題】

デバイス間で実行されるデータ転送に係るレイテンシを制御することで、当該データ転送を含む情報処理を首尾良く実行する。

【解決手段】

開示の情報処理装置の一形態では、複数のデバイスと複数のスイッチとを有し、一の該デバイスと他の該デバイスとは一つ以上の該スイッチを介してデータの送受信を行い、該各スイッチは該データを蓄積する一つ以上のバッファを備える情報処理装置であって、データの送受信が行われる経路に存在するスイッチの備えるべきバッファの数である目標バッファ数を取得するバッファ情報取得手段と、前記経路に存在するスイッチが備えるバッファの数が前記バッファ情報取得手段によって取得された目標バッファ数となるように、前記経路に存在するスイッチに対してバッファの数を設定するスイッチ制御手段と、を有することを特徴とする。

(もっと読む)

マイクロコンピュータ

【課題】CAN拡張フレームを使用しない場合には、CAN拡張ID記憶領域が使用されず、ハードウェア資源に無駄を生じさせるが、従来の技術では、CAN拡張ID記憶領域には、CAN拡張IDしか書き込むことができなかった。

【解決手段】CANメッセージバッファを少なくとも一つ備えるCANメッセージバッファ部と、CANメッセージバッファアクセス管理部とを具備するマイクロコンピュータによって解決することができる。CANメッセージバッファは、CAN標準IDを記憶する第一の記憶領域と、CAN拡張IDを記憶する第二の記憶領域と、CAN送受信データを記憶する第三の記憶領域とを有する。CANメッセージバッファアクセス管理部は、CAN拡張IDとは異なる目的外データを受け取り、その目的外データを、CANメッセージバッファにおける第二の記憶領域に書き込む。

(もっと読む)

周辺機能制御システムおよび方法

【課題】遠隔周辺機能を制御する周辺デバイス上の第2CPUを無くして、ハードウエアだけでなくソフトウエアの設計および維持コストを低減して全体のコストを低減する。

【解決手段】周辺機能を制御するシステムであって、遠隔周辺機能を起動および制御する制御コマンドを発生するプログラマブル処理ユニット110、およびプログラマブル処理ユニット110からの制御コマンドを制御パラメータの組に変換する第1ハンドリングユニット130を備える制御デバイス100と、制御パラメータの組に基づいて周辺機能を実行する周辺機能ユニット250、および通信リンク140,240を介して第1のハンドリングユニット130に接続され、制御パラメータの組を受信および検出して周辺機能ユニット250に送信する第2のハンドリングユニット230を備える周辺デバイス200と、を備える。

(もっと読む)

通信制御装置、情報処理装置およびプログラム

【課題】受信関数で指定された受信キーと一致する受信キーを有する受信メッセージを検索する時間を従来に比べて大幅に短縮させる。

【解決手段】取得した受信メッセージが有している受信キーからハッシュ値生成手段190により生成されたハッシュ値に応じて、複数の受信バッファ161〜164の中から一の受信バッファを選択して格納し、受信関数で指定される受信キーの一致判定により受信を行なう受信手段20からの送信要求に応じてハッシュ値に係る受信バッファ161〜164から受信関数に応じた受信メッセージの一つ以上の候補を出力する。これにより、受信関数で指定された受信キーと一致する受信キーを有する受信メッセージより先に一致しない受信キーを有する受信メッセージが大量に届いた場合であっても、受信関数で指定された受信キーと一致する受信キーを有する受信メッセージを検索する時間を従来に比べて大幅に短縮させることができる。

(もっと読む)

レジスタ制御装置、レジスタ制御方法、プログラム、およびプログラムを記録したコンピュータ読み取り可能な記録媒体

【課題】非連続な複数のレジスタに保持されているデータを、外部装置からの要求に応じて送信する。

【解決手段】レジスタ制御装置20は、データを保持するデータレジスタの番号を保持する複数の参照先管理レジスタ23と、外部装置からのデータ取得要求から開始レジスタ番号と読み出しレジスタ数とを抽出し、上記抽出した開始レジスタ番号で指定される参照先管理レジスタ23より開始して、上記抽出した読み出しレジスタ数で示される数だけの参照先管理レジスタ23からデータレジスタの番号を取得し、該取得した番号で指定されるデータレジスタから該取得順でデータを取得し、該取得したデータを該取得順でデータバッファレジスタ261に格納するレジスタデータ取得部26と、該格納されたデータを該格納順で取得するバッファリングデータ取得部27と、該取得したデータを該取得順に含めた応答メッセージを送信する応答メッセージ送信部29とを備える。

(もっと読む)

データ転送制御装置及び電子機器

【課題】IORDY信号のアサートタイミング違反等を確実に回避し、小規模でパラレルATAとシリアルATAのブリッジ機能を実現できるデータ転送制御装置等を提供する。

【解決手段】データ転送制御装置は、PATAバスに接続されるPATAI/F10と、SATAバスに接続されるSATAI/F50と、転送シーケンス制御を行うシーケンスコントローラ30とを含み、PATAI/F10は、TFR12を有する。シーケンスコントローラ30は、PIOリードの転送時にデバイス4からのPIOセットアップFISを受信した後に該デバイスから1セクタ分のリードデータの準備が完了するまで待ち、該リードデータの準備が完了した後に前記タスクファイル・レジスタのステータスレジスタのビジービットをクリアすると共にデータリクエストビットをセットする。

(もっと読む)

パケット処理装置

【課題】迅速にパケットの受信処理を行なうパケット処理装置を得ること。

【解決手段】複数のCPUa1〜anでNIC20を介して外部装置からのパケットを受信するパケット処理装置において、NIC20からDMA転送されるパケットを受信するDMA受信バッファb1〜bnをカーネル空間内に複数設定するOS40と、NIC20からのパケットをOS40からの指示に基づいた所定のDMA受信バッファで受信して上位レイヤ処理部62へ転送するパケット受信処理部1と、を備え、パケット受信処理部1は、NIC20から次のDMA転送が開始されるまでに、次に割込みを通知するCPUの設定と次にパケットを受信するDMA受信バッファの設定を切替えておき、NIC20が次のDMA転送を行なうと、設定しておいたCPUに割込み通知を行なうとともに設定しておいたDMA受信バッファでパケットを受信する。

(もっと読む)

クロスバーのストールした出力キューの情報をクリアするためのシステム及び方法

【課題】クロスバーのストールした出力キューの情報をクリアするためのシステム及び方法を提供する。

【解決手段】各時限ポート204は、入力キュー302、出力キュー304、及びキュータイマ306を備える。入力キュー302及び出力キュー304は、1つ又は複数の情報キュー308、312をそれぞれ備える。各情報キュー308、312は、単一の情報を記憶するように構成されている。 情報キュー308、312は直列に接続されて、1つの情報が情報キュー308、312の最初のものに到着するようにされている。その後、この1つの情報は、直列に又は順次、情報キュー308、312の最後のものへ伝播される。この1つの情報が出口キューに存在している時、次に、その情報をそのキューに結合された出力接続部上へ通信することができる。

(もっと読む)

シリアルデータ送受信装置

【課題】 他の機能ユニットとの間で送受信データのやり取りを効率的に行うことができるシリアルデータ送受信装置を提供する。

【解決手段】 送受信シフトレジスタ902は、受信したシリアルデータSDRをパラレルデータに変換するとともに、パラレルデータをシリアルデータSDSに変換して送信する。送受信バッファレジスタ904は、メインRAM25上に構成される送受信バッファSRBに受信データを書き込み、送受信バッファSRBから送信データを読み込む。送受信シフトレジスタ902は、受信開始の設定後の最初の受信データSDRの変化点から受信データを有効な受信データVDRとして送受信バッファレジスタ904に送出し、送信開始の設定後から送受信バッファレジスタ904から受領した送信データSDSを有効な送信データとして送信する。

(もっと読む)

マルチプロセッサシステム、及びマルチプロセッサシステムのメッセージ伝達方法

【課題】

プロセッサ間通信のスループットを向上させ、送受信するメッセージの優先順位に基づいたプロセッサ間通信を実行する。

【解決手段】

複数のプロセッサ2−1〜2−nと、メモリ3とを具備するマルチプロセッサシステムを用いる。メモリ3は、複数のプロセッサ2−1〜2−nの各々にバス4を介して接続されている。メモリ3は、複数のプロセッサ2−1〜2−nの各々から他のものへ送信されるメッセージを格納している。メモリ3は、メッセージを受信する側としての複数のプロセッサ2−1〜2−nに対応した複数の第1バッファ領域8−1〜8−nを備えている。

(もっと読む)

データ処理モジュール及びそのメッセージ受信方法

【課題】

CPUがメッセージバッファからメッセージを読み出す際に余分な処理が発生しないようにすること。

【解決手段】

送受信設定情報(MT)、格納情報(DN)および上書情報(OWS)と、識別子比較部からのFIT信号と、に基づいて、受信したメッセージを格納すべきメッセージバッファ内のアドレスの優位性を判定する判定部24を備え、メッセージバッファの第1のアドレスに係るバッファに第1のメッセージが格納されているときであって、第1のアドレスに係るバッファの格納情報が格納不可で上書情報が上書不可であり、かつ、第1のメッセージの識別子と同じ識別子の第2のメッセージを受信したときに、判定部24は、第1のアドレスよりも優位性の低い第2のアドレスについて劣位と判定し、第2のアドレスに係るバッファに第2のメッセージを格納しないようにする。

(もっと読む)

データ処理装置及びデータ処理方法及びプログラム

【課題】 実時間で持続的に発生するデータの継続的な格納処理において大量データが発生した場合でも、大量データ発生時点以外の定常状態のときには遅延のないデータ格納を実現する。

【解決手段】 データ量調整部103が、データ解析・正規化部102から入力データを入力し、入力データが所定のデータブロック分となった際に、書き込みデータ列107のデータブロックの数に基づき、入力データのデータブロックの書き込みが完了する格納予定時間を算出し、格納予定時間を遅延が許容される最大時間である遅延許容時間と比較し、遅延許容時間内に入力データのデータブロックが格納可能か否かを判断し、遅延許容時間内に格納可能な場合には入力データのデータブロックを書き込みデータ列の末尾に追加し、格納不可能な場合には当該データブロックを保留データ列に追加し、保留データ列のデータブロックはデータの入力がないときにデータベースへの書き込みを行う。

(もっと読む)

情報処理装置

【課題】 システムに所定の機能を追加する場合に、ハードディスクコントローラ手段が備えるファームウエアの修正のみで対応できる情報処理装置を提供する。

【解決手段】 シリアルATAブリッジ14に所定の機能を追加する場合に、ハードディスクコントローラ24が備えるファームウエア26の修正のみで、所定の機能を追加の追加を行う。

(もっと読む)

1 - 17 / 17

[ Back to top ]