Fターム[5B077GG07]の内容

情報転送方式 (3,847) | タイミング制御 (384) | タイミング制御の目的 (147) | スキューの補正/防止 (40)

Fターム[5B077GG07]に分類される特許

1 - 20 / 40

インターフェースの接続方法およびコンピュータ

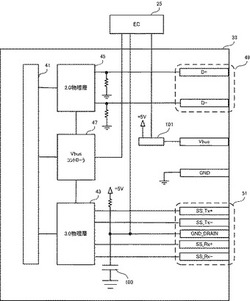

【課題】USB3.0に適合する周辺機器がコネクタで接続されたときに先にUSB2.0の構成が確立されても自動的にUSB3.0の構成を確立する。

【解決手段】3.0ピン51と2.0ピン49を備えるコネクタにデバイスを接続する。コネクタの挿入速度が遅い場合には2.0ピンだけが接続され3.0ピンが接続されない状態が短い時間発生する。その場合システムは先にUSB2.0の構成を確立する。EC25はその後3.0ピンが接続されてGND_DRAINラインの電位が変化したことを検出するとパワー・スイッチ101を所定の時間だけオフにしてデバイスをリセットする。リセットされたときは3.0ピンの接続が完了しているのでシステムはUSB3.0の構成を確立する。

(もっと読む)

クロック同期化回路及び半導体集積回路

【課題】SoCにおいて、バスマスタとクロック生成回路間の配線が長くなると、CTSバッファやリピータが複数必要になる。その結果、SoC内での遅延ばらつきが増大し、基本クロックCLKとクロック同期化信号CLKENの適正なタイミングを維持することができず、正常なデータの送受信が行なえない。そのため、基本クロックとクロック同期化信号の遅延ばらつきを解消するクロック同期化回路及び半導体集積回路が、望まれる。

【解決手段】図1に示すクロック同期化回路は、基本クロックと、基本クロックとシステムクロックとを同期させる第1の同期化信号と、システムクロックの分周比に関する情報を含む選択信号と、を受け付け、選択信号に基づき第1の同期化信号を所定時間保持し、基本クロックに同期させて、基本クロックとシステムクロックとを同期させる第2の同期化信号を出力する。

(もっと読む)

シリアルコントローラ及び双方向シリアルコントローラ

【課題】シリアルコントローラを提供する。

【解決手段】本シリアルコントローラは外部クロックと入力データとを受信し、反転クロックと出力データとを出力するよう適合し、インバータと、シリアル位置検出器と、同期クロック生成器と、シリアルレジスタと、半サイクル遅延ユニットとを備える。このシリアルコントローラにより、クロック列が反転された場合、データ信号と駆動クロックが同期しないという問題を回避できる。また、双方向シリアルコントローラは識別ユニットと、データ方向付けユニットとを更に備え、このシリアルコントローラは、エラー検出のための参照データとするために現在の状態を中央制御ユニットに送ることが出来る。

(もっと読む)

シリアル転送装置及び方法

【課題】受信側でのデータの待ち合わせ時間を短くし、送信側と受信側との間に生ずるレイテンシを小さくする。

【解決手段】シリアル転送装置1は、データを送信する送信部2と、データを受信する受信部3と、送信部2と受信部3とを接続し、データを伝送する複数のシリアル伝送路4と、受信部3において、各シリアル伝送路4のスキューに関するレーン間スキュー情報を生成し、レーン間スキュー情報を送信部2に送信するレーン間スキュー情報生成部5と、送信部2において、レーン間スキュー情報に基づいてデータの各シリアル伝送路4への振り分けを決定する変換ルールを生成するデータ変換ルール生成部6とを備える。

(もっと読む)

半導体装置、その装置を備える半導体システム、及びそのシステムの動作方法。

【課題】半導体装置コントローラと半導体装置との間でデータが入出力される時、データの位相が変動することと関係なく、半導体装置コントローラと半導体装置との間で常に安定的にデータが入出力できるシステム、そのシステムに用いる半導体装置、及びそのシステムの動作方法を提供すること。

【解決手段】半導体装置は、印加されるライトクロックとライトデータとを補正する回路及び方法に関するもので、データ入出力コマンドに応答してノーマルデータ(ソースクロックのセンターに同期する)を入出力するノーマルデータ入出力部11と、所定のコマンドに応答してデータ復旧情報信号(前記ソースクロックのエッジに同期する)の入力を受けて所定の時間の後に出力するデータ復旧情報信号入出力部100とを備える。

(もっと読む)

情報処理装置およびその制御方法

【課題】特にメモリカードとホスト側間の全体的なデータの転送速度を向上させることができる情報処理装置およびその制御方法を提供する。

【解決手段】位相が異なる複数のサンプリングクロックを生成するクロック生成手段と、複数のサンプリングクロックの各々で入力データをサンプリングする複数のデータ入力手段と、データ入力手段がサンプリングした複数のデータ値をサンプリング単位で比較するデータ比較手段と、データ比較手段による比較結果に基づき、位相ずれに関する情報を集める位相ずれ集計手段と、位相ずれ集計手段が集めた位相ずれに関する情報を通知する通知手段とを有するホストコントローラと、通知手段から通知された情報を基にホストコントローラを制御する制御手段とを備える。

(もっと読む)

データ転送装置、データ転送制御方法、データ転送制御プログラム及び記録媒体

【課題】本発明は、複数のデータ転送制御部から印刷部側に画像データを同期転送する複合装置、プリンタ装置等のデータ転送装置、データ転送制御方法、データ転送制御プログラム及び記録媒体に関する。

【解決手段】複合装置1は、同期をとって送信する必要のある画像データを複数の転送制御部7a、7bから印刷処理部8に送信する場合に、各転送制御部7a、7bが受信した基準信号Ksを相互に基準信号入力・転送回路30a、30b及び基準信号転送路11を通して比較基準信号Kshとして送受信し、該基準信号Ksと該比較基準信号Kshの時間差を検出して、該時間差であるスキュー値に基づいて印刷処理部8へのデータ送信タイミングを調整する。したがって、印刷処理部8と各転送制御部7a、7bとの間にスキューがある場合にも、該スキューを考慮した画像データの転送を行うことができる。

(もっと読む)

送受信制御装置、電子機器、データ送信方法及び制御プログラム

【課題】 スレーブデバイスによる応答信号を返信するタイミングが許容範囲を満たしていない場合であっても、バスファイトを一度も発生させることがなく、デバイス内の回路破壊を防止することができるマスターデバイスを提供する。

【解決手段】 マスター10は、クロックを生成し、各スレーブ20に当該クロックを送信するクロック生成部12と、各スレーブ20に対して最初に送信するシリアルデータの第一バイトにおける最下位ビットを除くフレームで擬似フレームを生成し、各スレーブ20に当該擬似フレームを送信するフレーム生成部13と、擬似フレームをデータ信号線31に送出し終えた時点から当該擬似フレームに対するスレーブ20からのACKを検出した時点までの応答時間を算出する応答時間算出部14bとを備え、フレーム生成部13が、応答時間に基づき、シリアルデータの各バイトのフレームにおける、データ信号線に対するフレームの送出を完了するタイミングを調整する。

(もっと読む)

高速データレートインタフェース装置及び方法

【課題】デジタル制御データとデジタルプレゼンテーションデータの事前に選択されたセットを通信するための通信プロトコルを形成するために、共にリンクされるパケット構造を使用して、通信経路上、ホストとクライアントの間でデジタルデータを転送するためのデータインタフェースを提供する。

【解決手段】信号プロトコルは、通信プロトコルを形成するパケットを生成、送信、及び受信し、デジタルデータを1つ又は複数のタイプのデータパケットに形成するように構成され、少なくとも1台が該ホストデバイスに常駐し、該通信経路を通して該クライアントに結合される、リンクコントローラによって使用される。インタフェースは、短距離「シリアル」タイプデータリンクでの、費用効果が高い、低電力の、双方向高速データ転送機構となる。

(もっと読む)

液晶表示装置の製造方法

【課題】受信したクロックと入力信号の間に位相ずれがあっても、位相ずれをなくした状態で入力信号を取り込める半導体装置の実現。

【解決手段】受信したクロックに基づいて内部クロックを発生するクロック発生回路142と、入力信号を内部クロックに同期して取り込む信号入力回路144とを備える半導体装置において、外部クロックと同じ周波数を有する入力信号に同期した信号が入力され、クロック発生回路で発生された内部クロックに同期して取り込んだ時の出力信号値を判定することにより、取り込みタイミングが内部クロックに対して進んでいるか遅れているかを判定するダミー入力回路174,175,176,181を備え、クロック発生回路は、判定結果に基づいて外部クロックを選択的に遅延させて内部クロックを生成するデイレイ回路171,172と、ダミー入力回路の判定結果に基づいてディレイ回路での遅延量を制御するディレイ制御回路173とを備える。

(もっと読む)

フォールトトレラントコンピュータ及びそのタイミング調整方法

【課題】従来のフォールトトレラントコンピュータは、多重化されたシステムにおいてロックステップ状態を維持できないという問題があった。

【解決手段】本発明にかかるフォールトトレラントコンピュータは、演算処理回路101、109と、演算処理回路101との第1の信号送受信を行い、第1のクロックを調整する調整回路104と、演算処理回路109との第2の信号送受信を行い、第2のクロックを調整する調整回路112と、を備え、調整回路104は、第1の信号送受信時間を記憶するメモリ107と、第1の信号送受信時間と第2の信号送受信時間とに基づいて第1のクロック遅延調整量を決定する遅延調整量決定部108と、を備え、調整回路112は、第2の信号送受信時間を記憶するメモリ114と、第1の信号送受信時間と第2の信号送受信時間とに基づいて第2のクロック遅延調整量を決定する遅延調整量決定部116と、を備える。

(もっと読む)

同期型データ転送システムおよび同期型データ転送制御方法

【課題】システムが動作中であっても、さらには、小型化・高速化を要する環境下であっても、安定した同期型データ転送の実現が可能な同期型データ転送システムを提供する。

【解決手段】例えばメモリ2からデータ転送用クロック32に同期させてデータ・バス31aを介してデータを転送する際に、データ転送要求受付後最初のデータをメモリコア22から取り出すまでのデータ出力待ち時間を利用して、遅延時間測定データ格納部23に格納している遅延時間測定データ23a〜23cをデータ・バス31aに送信することにより、制御LSI10の遅延時間測定部12にてデータ・バス31aの遅延時間を測定し、遅延調整制御部17は、測定した遅延時間に基づいて、データ・バス31aを介して転送されてくるメモリコア22からのデータを取り込むためのデータ取り込みタイミングを調整して、メモリコントローラ11に供給する。

(もっと読む)

データ伝送回路、及びこれを用いた画像形成装置

【課題】本来転送しようとしているデータのデータ量を増大させることなく、スキューの影響を低減することができるデータ伝送回路、及びこれを用いた画像形成装置を提供する。

【解決手段】データ送信部81によって、テスト用データを転送クロック信号CKと同期させて送信させ、各ビット受信部83により受信されてデュアルポートRAM84に記憶されたデータを読み出して前記テスト用データと比較し、当該読み出されるデータの各ビットがテスト用データの各ビットとそれぞれ一致するように、位相の異なるクロック信号のうち一つを各マルチプレクサ831で選択させ、受信同期用の同期クロック信号CKnとするタイミング調整処理を実行するデータタイミング調整部46とを備えた。

(もっと読む)

位相調整装置およびカメラ

【課題】 より簡易な構成で、データとクロックとの位相の関係を適切に調整するための手段を提供する。

【解決手段】 位相調整装置は、比較コード生成部と、演算部と、遅延部とを備える。比較コード生成部は、シリアル転送データに含まれる先頭コードの位相を進めた第1比較コードと、先頭コードの位相を遅らせた第2比較コードとをそれぞれ生成する。演算部は、先頭コードおよび第1比較コードの比較結果と、先頭コードおよび第2比較コードの比較結果とを用いて、シリアル転送データの位相の調整方向を求める。遅延部は、位相の調整方向に基づいて、シリアル転送データの遅延量を調整する。

(もっと読む)

データ伝送回路、画像形成装置

【課題】データ同士のスキューを可及的に低減できるデータ伝送回路を提供する。

【解決手段】例えば複合機1の主電源がオンされると、或いは、画像形成動作を実施しない期間の或るタイミングで、当該複合機1のモードを、各差動ドライバ部205〜207のドライブ能力の設定処理を実施するキャリブレーションモードに設定するモード設定部46と、前記差動ドライバ205〜207のドライブ能力の段階を順番に切り替えていくドライブ能力設定部48と、前記ドライブ能力の各段階において、予め定められた補正用信号がパラシリ変換部201〜203から出力されるように送信制御回路200に指示を与え、前記補正用信号を前記シリパラ変換部307〜309で受信したタイミングを、受信制御回路300を用いて検出する検出部47とを備えた。

(もっと読む)

伝送制御回路及びそれを備えた半導体記憶装置

【課題】信号を伝送する際の遅延の変動に対し、適切な出力タイミングを自動的に制御し、高速な伝送速度と不良の低減が可能な伝送制御回路を提供する。

【解決手段】本発明の伝送制御回路は、制御信号SMに同期して入力された信号を信号バスDBに伝送させ、制御信号SBに同期して出力する信号伝送回路20と、信号伝送回路20に制御信号SBを供給し、信号バスDBの出力タイミングを制御する出力制御回路14と、制御信号SMに基づく信号の入力タイミングに連動してレベルが遷移するレプリカ信号を、信号バスDBと同一の伝送特性を有するレプリカ信号バスRBに伝送させて出力するレプリカ回路30と、レプリカ信号のレベルの遷移を検知し検知結果を示すフィードバック信号SFを出力制御回路14に供給する検知回路34を備え、出力制御回路14の出力タイミングは、フィードバック信号SFにおけるレプリカ信号の遷移タイミングに応じて制御される。

(もっと読む)

メソシンクロナス・データ・バス装置及びデータ伝送方法

メモリ・システムにおける指定されたポイント間の全体の時間遅延が一定に維持されるように、メモリ・モジュール間のデータの伝送時間が管理される、メモリ・システムについて説明される。多数のレーンのバスの各レーンを別個に管理することができ、中間モジュールにおいてスキュー除去する必要なしに、宛先モジュールにおいてデータフレームを評価することができる。バス・シリアル・データ速度の1つ又それ以上の約数でモジュールを通してデータ経路を作動させ、受信されたデータのサンプリング・ポイントを選択し、温度変化又は時間経過に起因する時間遅延の変動を調整することによって、データを経路指定するためのスイッチを有するモジュールを通したデータの伝播における時間遅延が低減される。 (もっと読む)

データ送信装置、データ受信装置、データ転送装置、及び電子機器

【課題】回路規模を縮小することができるデータ送信装置、データ受信装置、及びデータ転送装置、並びに当該装置を備える電子機器を提供する。

【解決手段】データ転送装置1は、データ送信装置10とデータ受信装置20とを備え、2ビットのデータD11,D12を、転送クロックCLKに同期してデータ送信装置10からデータ受信装置20に転送する。データ送信装置10,20は、転送クロックCLKと周波数が同じ第1クロックCLK1と、第1クロックCLK1に対して周波数が1/2倍の第2クロックCLK2とを生成するクロック生成部11,21をそれぞれ備える。また、データ送信装置10は4つのDフリップフロップ13,14,15a,15bからなる送信部12を備え、データ受信装置20は4つのDフリップフロップ23,24a,24b,26及びセレクタ25からなる受信部22を備える。

(もっと読む)

半導体集積回路装置

【課題】クロック周波数を切り替える際のモジュール間のデータ転送の同期はずれが生じない半導体集積回路装置を提供する。

【解決手段】外部から供給されるクロックから第1及び第2の内部クロックを生成するとともに、該第1及び第2の内部クロックの周波数の関係に応じた第1及び第2のクロック同期信号を生成するクロック制御部と、前記第1のクロックと前記第1及び第2のクロック同期信号を受取る第1のモジュールであって、該モジュール内部で用いられるクロック及び前記第2のクロックのタイミングで動作する第2のモジュールを制御するための制御信号を生成する内部回路を有する第1のモジュールとを有する半導体集積回路装置である。前記第1の内部クロックの周波数にかかわらず、前記第1及び第2のモジュール間のデータ転送は同期して行われる。

(もっと読む)

デバイスのタイミングを補償する装置及び方法

【課題】周辺装置との間の信号授受のタイミングを制御し、動作の安定化が図られるメモリ素子を提供する。

【解決手段】デバイスタイミング制約を伴う電子デバイスは、行列コマンドを搬送する相互接続構造体に接続された1組の接続部を含む。メモリコアはデータを記憶する。1組の接続部及びメモリコアにはメモリインターフェイスが接続される。メモリインターフェイスは、行コマンド及び列コマンドに基づいてメモリコアタイミング信号を発生する回路を備えている。メモリインターフェイス回路は、メモリコアタイミング信号の選択されたタイミング信号のタイミングを調整する個々の遅延要素を含む。

(もっと読む)

1 - 20 / 40

[ Back to top ]