Fターム[5B079BA06]の内容

Fターム[5B079BA06]の下位に属するFターム

Fターム[5B079BA06]に分類される特許

1 - 20 / 32

時間測定装置、マイクロコントローラ、プログラム、及び時間測定方法

クロックゲーティング回路およびバスシステム

【課題】トランザクションを単位として扱うバスシステムにおいて消費電力を低減する。

【解決手段】クロックゲーティング回路は、クロックイネーブル信号生成部とマスククロック生成部とを備える。クロックイネーブル信号生成部は、バスシステムを複数のリージョンに分割した各々においてアウトスタンディングトランザクションの数を計数することにより複数のリージョンの各々のためのクロックイネーブル信号を生成する。マスククロック生成部は、複数のリージョンの各々のためのクロックイネーブル信号によってクロックをマスクしてマスククロックを生成する。

(もっと読む)

半導体装置

【課題】所定の動作の期間においてクロックを停止させ、消費電力を低減する半導体装置を提供すること。

【解決手段】発振器11からの第1クロックCLK_oriをN分周した第2クロックCLK_divを出力する分周回路120−1と、前記第1クロックと前記分周回路からの前記第2クロックとを選択し、選択したクロックを出力する選択回路120−2と、前記第1クロックまたは前記第2クロックをカウントするタイマ回路120−3と、前記タイマ回路のカウント結果をデコードし、第1結果を出力するデコーダ120−4と、前記デコーダからの前記第1結果に基づき、前記選択回路が前記第2クロックを選択するよう第1選択信号を出力するステートマシン120−9と、前記第1選択信号に基づき、前記ステートマシンの動作を停止する停止信号を出力する論理回路120−6とを具備する。

(もっと読む)

データ処理装置、データ処理方法及びプログラム

【課題】より高い省電力効果を得ることができるようにする。

【解決手段】入力データを処理して出力する処理手段と、前記処理手段の入力又は出力に接続されてデータの入出力を遮断するゲート手段と、前記処理手段へのクロック供給を制御する制御手段と、前記制御手段にクロック制御の指示を行う指示手段とを有し、前記制御手段は、前記指示手段からの指示に基づいて、前記ゲート手段を制御するとともに、前記処理手段に供給するクロックを制御するデータ処理装置等を提供する。

(もっと読む)

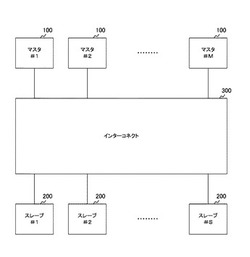

データ処理システム

【課題】 データ処理システムの消費電力をきめ細かく制御する。

【解決手段】 複数のマスターの各々は、データの転送要求とともにデータの転送速度を示すスピードグレード信号を出力する。調停回路は、複数のマスターからの転送要求およびスピードグレード信号を調停する。クロックイネーブル生成回路は、調停回路により調停されたスピードグレード信号に応じて、有効期間の比率が異なるクロックイネーブル信号を生成する。スレーブは、クロックイネーブル信号が有効なときにクロック信号を受けて動作し、調停回路により調停された転送要求に応じてデータを転送する。これにより、スレーブを動作させるクロック信号の周波数を転送要求毎に変更でき、スレーブの電力のきめ細かな制御を容易に実施できる。

(もっと読む)

マルチコアプロセッサ用の電力チャネルモニタ

マルチコアプロセッサ内での電力チャネル監視の技法を、全般的に説明する。電力管理システムを、マルチコアプロセッサ内の個々のコアに供給する電力チャネルを監視するように構成することができる。電力チャネルモニタは、各コアの電力消費の直接測定値を提供することができる。個々のコアの電力消費は、どのコアの使用が多いか、または少ないかを示すことができる。使用判定を、測定されるコアへまたはこれからのデータメッセージの送信を全く伴わずに行うことができる。各プロセッサコアによってサービスされる判定された使用負荷を使用して、そのコアに供給される電力および/またはクロック信号を調整することができる。  (もっと読む)

(もっと読む)

半導体集積回路

【課題】独立してクロック信号の供給と遮断が行われる領域を有する半導体集積回路において、クロックスキューを低減し、かつ、消費電力を低減すること

【解決手段】本発明にかかる半導体集積回路1は、クロック信号が供給される第1の配線と、第1の配線に供給されるクロック信号とは独立して供給と遮断とが切り替えられてクロック信号が供給される第2の配線と、第1の配線からクロック信号が供給される第1のメッシュ形状配線を有する第1の領域と、第2の配線からクロック信号が供給される第2のメッシュ形状配線を有する第2の領域と、第1のメッシュ形状配線と第2のメッシュ形状配線の間の信号の導通と遮断を切り替え可能な切り替え回路とを備える。

(もっと読む)

クロックのデューティ・サイクルの自動制御

【課題】クロック信号の立ち下がりを調節して望ましいデューティ・サイクルを達成するデューティ・サイクル補正(DCC)回路を提供する。

【解決手段】幾つかの例では、DCC回路は、入力クロック信号の立ち下がりに応答してパルスを発生し、そのパルスを制御電圧に基づいて遅延し、遅延したパルスに基づいて入力クロック信号の立ち下がりを調節して出力クロック信号を生成し、出力クロック信号のデューティ・サイクルと望ましいデューティ・サイクルとの間の差に基づいて制御電圧を調節する。DCC回路は、望ましいデューティ・サイクルを達成するためにクロック・サイクルの立ち下がりを調節するので、クロック信号の立ち上がりを調節する既存のPLL制御ループへ、その動作に干渉することなく組み込むことができる。

(もっと読む)

クロック制御回路

【課題】遅延時間の大きな信号の状態が変化した後または前後でクロック信号を停止あるいは周波数を低くするクロック制御回路を提供する。

【解決手段】このクロック制御回路は、クロック信号の供給を停止するゲート回路1と、リセット信号に応答して、ゲート回路1によってクロック信号の供給を停止させるとともに、リセット信号に応答して論理レベルが変化する内部リセット信号を生成し、内部リセット信号の論理レベルが変化する前後でクロック信号の供給を停止させるゲート制御回路13とを備える。したがって、フリップフロップ21〜25の誤動作を防止できる。

(もっと読む)

クロック分周回路

【課題】入力クロック信号の立ち下がりの際に、出力クロック信号の立ち上げを可能とし、入力クロック信号を任意の有理数で表わされる分周比にて分周した出力クロック信号を得ること。

【解決手段】本発明は、演算器11、演算器12a、比較器108とを少なくとも備える。分子設定値112を分母設定値111で除した値である分周比で入力クロック信号109を分周する。演算器11は、入力クロック信号109に同期して入力信号の値を記録する。そして、生成した演算器出力値120を入力クロック信号109に応じて出力する。演算器12aは、演算器出力値120を出力する。比較器108は、演算器出力値120が分子設定値112と比較してハイ信号またはロウ信号を出力クロック信号121として出力する。演算器出力値120は帰還して演算器11に入力される。

(もっと読む)

半導体集積回路およびその動作方法

【課題】クロック選択回路の最終選択出力でのメタステーブルの障害の発生確率を低減する。

【解決手段】半導体集積回路に内蔵のクロック選択回路は、デコーダDEC、制御ユニットCnt、マルチプレクサMpxを有する。DECに選択信号SELが供給され、Cntに第1と第2のクロック信号CKIN0、1とデコーダDECの第1と第2の選択出力信号が供給され、MpxにCntの第1と第2の選択制御信号Q´0、1が供給される。Cntの第1と第2のゲートAND0、1の一方の入力にDECの第1と第2の選択出力信号が供給される。第1ゲートAND0の出力と第2ゲートAND1の他方の入力の間に直列接続の第1と第2のD型フリップフロップD−FF0、2と、第2ゲートAND1の出力と第1ゲートAND0の他方の入力の間に直列接続の第3と第4のD型フリップフロップD−FF1、3を含む。

(もっと読む)

クロック制限回路、信号出力回路及び信号入力回路

【課題】対象となる回路の制約を受けずに適用可能なゲーテッドクロック回路を提供すること。

【解決手段】入力回路30への動作クロックCLK2の入力を制限するゲーテッドクロック回路10であって、入力回路30に入力される非同期信号ASYNCと次クロックにおいて入力回路30に入力される次信号DATAとの排他的論理和の信号を出力するXOR101と、XOR101の出力信号を、CLK2に応じて出力するLAT102及びCGFF103と、CGFF103の出力とCLK2の論理積であるゲーテッドクロック信号GCLKを出力するAND104を含む。

(もっと読む)

マイクロコンピュータ

【課題】チップ外に出力されるクロック信号と、チップ内のクロック信号との間の位相差を低減する。

【解決手段】第1クロック信号を発生可能な発振器(101)と、上記第1クロック信号とフィードバック信号との位相比較を行い、それに基づいて第2クロック信号を形成するPLL回路(102)とを設ける。さらに、上記第2クロック信号に基づいて、チップ内部に供給される第3クロック信号と、チップ外部に出力される第4クロック信号(CLK(φ))とを形成するクロックパルスジェネレータ(103)と、クロック遅延補正データが格納されるクロック遅延補正データ記憶部(105)とを設ける。上記PLL回路に、上記フィードバック信号を補正するための可変ディレイ回路(13)を設け、上記位相差低減のためのクロック遅延補正を行う。

(もっと読む)

クロック信号供給回路の設計方法、情報処理装置およびプログラム

【課題】半導体集積回路におけるクロック信号の供給において、回路全体を通しクロックラインを短縮し得る構成を提供することを目的とする。

【解決手段】回路素子のグループ間で回路素子の交換、移動を実行し、当該実行の前後でグループごとに回路素子の位置と中心位置との距離の合計し更に全グループについて合計した値が減少する場合には当該実行後のグループを維持し減少しない場合には当該実行前のグループを維持する最適化を実行する構成である。

(もっと読む)

半導体装置

【課題】ノイズ又はジッタの影響により不安定な位相比較結果が出ても、クロック整合トレーニング動作の安定した結果を外部コントローラに伝送することができる回路を提供する。

【解決手段】第1クロックHCKの位相を基準として第2クロックWCKの位相を検出し、当該検出結果に対応する第1検出信号DET_SIG1を生成する第1位相検出手段430と、第2クロックWCKを所定時間だけ遅延したクロックDLY_DIV_WCKの位相を、第1クロックHCKの位相を基準として検出し、当該検出結果に対応する第2検出信号DET_SIG2を生成する第2位相検出手段440と、出力信号を出力し、第1検出信号DET_SIG1、第2検出信号DET_SIG2、及びフィードバックされた出力信号TRAINING_INFO_SIGに応答して、出力信号TRAINING_INFO_SIGの論理レベルを決定する論理レベル決定手段450と、を備える。

(もっと読む)

信号処理装置および信号処理方法

【課題】 相互に異なる周期のクロック信号が与えられ、かつ相互に非同期で所定の処理を行う複数の処理部のリセットを、簡単な構成で、確実に行うことができる信号処理装置および信号処理方法を提供する。

【解決手段】 モジュール回路部14は、モジュールA,B,Cのうちのいずれかに対するリセット指令が与えられると、指令されたモジュールを指定する信号を含み、かつCPUCLKの1周期分の長さを有する1shotリセット信号を生成する。同期リセット生成回路部15は、1shotリセット信号が与えられ、この1shotリセット信号の長さを指令されたモジュールに対応する長さに引き延ばした伸長リセット信号を生成し、生成した伸長リセット信号を指令されたモジュールのクロックに同期させて同期リセット信号を生成し、指定されたモジュールでは、同期リセット信号が与えられた状態で、クロック信号が立上がりまたは立下ると、リセットされる。

(もっと読む)

マイクロコンピュータシステム

【課題】メインCPU部に対する電源の供給制御をより適切に行い、低消費電力化を図ることができるマイクロコンピュータシステムを提供する。

【解決手段】メインCPU4を含むメインマイコン2とは別に、サブCPU8と、メインマイコン2への電源供給を制御する電源制御部24とを備えるサブマイコン3を設け、サブマイコン3に低周波数のサブクロック信号を供給するサブクロック部9を、連続モードと間欠モードとに切り替え可能とする。メインCPU4が、自身の動作停止条件が成立したと判断してサブCPU8に動作停止通知を行うと、サブCPU8はその通知を認識し、メインマイコン2への電源供給を停止させてサブクロック部9を間欠モードに設定する。サブCPU8は、間欠モードでサブクロック信号が供給されている期間に動作開始条件が成立したかを判断し、条件が成立するとサブクロック部9を連続モードに切り替えてメインマイコン2に対する電源供給を再開させる。

(もっと読む)

半導体装置

【課題】クロックサイクルに同期する回路による電力消費状態の相違に起因する電源電圧の変動を容易に抑制する。

【解決手段】クロックサイクルに同期動作しアクセスを要求することができる第1回路(2)がアクセス要求に対する応答を待っているとき、電流消費動作を行う電流消費回路(20)を採用する。前記電流消費回路は第1回路に指示された動作の休止期間における消費電流量の低下を抑制するために前記クロックサイクル毎に電流消費動作を行い、電流消費動作を行う複数個の電流消費ユニット(21)を有する。前記第1回路の動作休止期間に、電流消費動作を行う前記電流消費ユニットの数は可変化能にされる。電流消費回路による消費電流量は動作選択される電流消費ユニットの数によって設定されるから、予めその電流量を見積もることは難しい場合にも容易に対応することができる。

(もっと読む)

動作モード設定装置、それを含む半導体集積回路および半導体集積回路の制御方法

【課題】クロックの状態変化による誤動作に対する適応性を向上させる動作モード設定装置、それを含む半導体集積回路および半導体集積回路の制御方法を提供する。

【解決手段】本発明の動作モード設定装置は、基準クロックとフィードバッククロックの位相を判別して固定猶予信号を生成する動作モード設定制御部およびリセット信号と前記固定猶予信号の制御によって位相比較信号とパルス信号に応答して固定完了信号を生成する動作モード設定部を含む。

(もっと読む)

情報処理装置、およびプロセッサ回路の制御方法

【課題】パフォーマンスの低下を抑えながら、半導体装置の温度上昇を抑制すること。

【解決手段】DTS201Bが温度T1を測定し、制御部201Cが温度T1が閾温度より高いと判断した場合に、半導体回路202に測定温度T1を送信する。DTS202Bが温度T2を計測する。制御部202Cは、温度T1が前記温度T2より高いと判断した場合に、第2プロセッサ回路202Aの動作速度を低下させる。

(もっと読む)

1 - 20 / 32

[ Back to top ]