Fターム[5B079CC08]の内容

計算機・クロック (4,131) | 位相/タイミングの調整 (657) | 調整手段 (364) | 遅延量を計測するもの (50)

Fターム[5B079CC08]に分類される特許

1 - 20 / 50

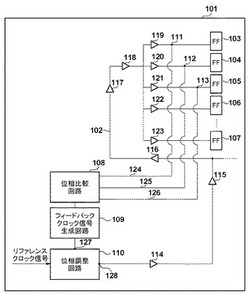

クロック分配回路及びクロック分配回路の形成方法

【課題】 28nm以降の半導体プロセスでは、チップ内バラツキが顕著になったため、フィードバックパスにトランジションフォルトが発生する頻度が上がった。従来技術ではフィードバックパスのトランジションフォルトが発生した場合の対策がなく、歩留まり低下につながる。

【解決手段】 クロック信号が分配されるクロックツリーと、クロックツリーの異なる分岐点から出力される複数のフィードバッククロック信号を受信し、各フィードバッククロック信号の位相差を検知する位相比較回路とを有する。位相比較回路によって検知した位相差に基づいて、半導体集積回路内の製造バラツキを補正するためのバラツキ補正済フィードバッククロック信号を生成するフィードバッククロック信号生成回路を有する。フィードバッククロック信号生成回路によって生成されたバラツキ補正済フィードバッククロック信号と基準クロック信号との位相差が小さくなるようにクロック信号を遅延する位相調整回路を有する。

(もっと読む)

半導体集積回路のクロック遅延調整回路およびその制御方法

【課題】回路規模が増大する問題があった。

【解決手段】複数の回路ブロックと、入力するクロック信号を遅延制御信号に基づいて遅延したクロック信号を対応する前記複数の回路ブロックに供給する複数のクロック遅延回路と、前記複数の回路ブロックの遅延試験を行う制御回路と、前記遅延試験の結果に応じて、前記複数の回路ブロックのうち遅延処理が必要な回路ブロックの情報を記憶する救済グループ記憶回路と、前記遅延試験の結果に応じて、前記複数の回路ブロックのうち遅延処理が必要な回路ブロックの遅延値情報を記憶する、所定数の遅延設定回路と、前記救済グループ記憶回路が記憶した回路ブロックの情報に対応したクロック遅延回路に対し、前記遅延設定回路が記憶した遅延値情報に応じた前記遅延制御信号を割り当てる遅延設定割当制御回路と、を有する半導体集積回路のクロック信号調整回路。

(もっと読む)

デジタル信号処理回路、デジタル信号処理方法、及び、プログラム

【課題】セットアップタイム及びホールドタイムのマージンを十分に確保することが可能なデジタル信号処理回路を提供すること。

【解決手段】回路は第1の遅延量を複数の判定用遅延量のそれぞれに設定する。回路は入力データ信号を、第1の遅延量だけ遅延させた第1の遅延データ信号と第2の遅延量だけ遅延させた第2の遅延データ信号とを出力する。回路は、第1の遅延データ信号をラッチすることにより第1のラッチデータを取得し、第2の遅延データ信号をラッチすることにより第2のラッチデータを取得する。回路は、複数の判定用遅延量のそれぞれに対して、第1のラッチデータと第2のラッチデータとが一致しているか否かを判定し、当該判定結果に基づいて第1のラッチデータと第2のラッチデータとを一致させるように、第1の遅延量を第1の制御遅延量に設定し且つ上記第2の遅延量を第2の制御遅延量に設定する。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】入力クロックの周波数変化に依存して変調プロファイルが変化しないスペクトラム拡散クロックジェネレータを提供する。

【解決手段】スペクトラム拡散クロックジェネレータは、切替信号に応じて入力クロックを遅延し、出力クロックとして出力する遅延ラインと、入力クロックの周期を計測する入力クロック周期計測部と、入力クロック周期計測部の計測結果に応じて、1変調周期当たりの出力クロックのサイクル数、および、あらかじめ設定された変調度に対応する入力クロックの所定サイクル当たりの出力クロックの周期の変調ステップ幅を算出し、算出されたクロックサイクル数および変調ステップ幅に基づいて切替信号を生成する遅延ライン制御部とを備えている。

(もっと読む)

クロックツリー合成装置、クロックツリー合成方法及びプログラム

【課題】半導体集積回路のCTSにおいて、クロック遅延時間を削減すること。

【解決手段】CTS装置は、クロックドメインに接続された複数のフリップフロップの重心座標を求め、求めた重心座標と各フリップフロップとの距離を算出し、重心座標から遠いフリップフロップから順に、重心座標からのクロックラインにおける遅延時間をクロック遅延時間として算出し、前段のフリップフロップとの距離を求め、求めた距離からデータパスにおける遅延時間をデータ遅延時間として算出し、クロック遅延時間とデータ遅延時間との和がクロックドメインのクロックの1周期よりも長いフリップフロップを選択し、選択されたフリップフロップと前段のフリップフロップとのデータパスがフォルスであると判定された場合には、選択されたフリップフロップをスキュー調整の対象外としてクロックツリーを合成する。

(もっと読む)

動的バスクロックを制御するための装置及び方法

【課題】本発明は動的バスクロックを制御するための装置及び方法に関する。

【解決手段】本発明による動作バスクロックを制御するための装置は、少なくとも一つのマスターモジュールと、少なくとも一つのスレーブモジュールと、前記少なくとも一つのマスターモジュールと前記少なくとも一つのスレーブモジュールが送受信するデータを媒介するバスと、前記少なくとも一つのマスターモジュールの動作情報(Activity)を考慮してバスクロックの周波数を決定するバス周波数制御機と、前記バス周波数制御機で決定した周波数を発生させて生成したクロックを前記少なくとも一つのマスターモジュールと前記少なくとも一つのスレーブモジュール及び前記バスに提供するクロック発生器と、を含む。

(もっと読む)

半導体集積回路

【課題】複数の回路ブロックを有する半導体集積回路にて、電源ノイズにより発生するクロック信号におけるジッタを低減する。

【解決手段】第1の回路ブロックに供給される第1のクロック信号のクロックパスディレイを測定する遅延測定回路と、第2の回路ブロックの動作による電源電圧の変動時間を測定する時間測定回路と、第2の回路ブロックに供給される第2のクロック信号を遅延させる遅延調整回路と、第1のクロック信号と第2のクロック信号との位相差を測定する位相差測定回路と、遅延調整回路での遅延量を制御する位相制御回路とを備え、第2の回路ブロックの動作周波数が第1の回路ブロックの動作周波数より低い場合には、位相制御回路が、ジッタが最小となる電源ノイズと第1のクロック信号との設定位相差を算出し、位相差測定回路により測定した位相差が設定位相差になるように遅延量を制御する。

(もっと読む)

クロック分配素子及びそれを用いたレイアウト設計方法

【課題】簡易かつ精度良くデューティ比を調整することができるクロック分配素子及びレイアウト設計方法を提供すること。

【解決手段】本発明に係るレイアウト設計方法は、クロックツリー回路のレイアウト設計方法であって、クロックツリー回路上に第1のクロック分配素子を配置し、前記第1のクロック分配素子が配置された前記クロックツリー回路に配線し、配線された前記クロックツリー回路についてタイミング検証し、前記タイミング検証の結果に基づいて、前記第1のクロック分配素子を、当該第1のクロック分配素子と入力負荷容量が略等しく遅延値が異なる前記第2のクロック分配素子へ置換するものである。

(もっと読む)

クロック分配回路およびクロック分配方法

【課題】クロック分配網間のクロックスキューをより低減する。

【解決手段】リファレンスクロック信号11の位相を調整してクロック分配網に分配するPLL回路1、2と、クロック分配網における複数のフィードバック点PA1〜PAn、PB1〜PBnからそれぞれフィードバッククロック信号HA1〜HAn、HB1〜HBnを入力し、PLL回路1、2でリファレンスクロック信号11の位相比較対象とされる複数のフィードバッククロック信号から一つの信号を、複数のフィードバッククロック信号のそれぞれの遅延値に基づいて選択するフィードバッククロック信号選択回路9、16と、を複数のクロック分配網のそれぞれに対応して備える。

(もっと読む)

デスキュー回路およびデスキュー方法

【課題】デスキュー後のデータの遅延時間を一定範囲に保ち、また、消費電力を低減することができるデスキュー回路を得ること。

【解決手段】データ信号にチェックコードを付加してパラレル信号に変換する伝送データ送信処理回路1と、パラレル信号に対してそれぞれ遅延時間を付加する遅延回路2−1〜2−nと、遅延付加信号のチェックコードに基づいて受信品質を求める伝送データ受信処理回路3と、受信品質に基づいて、パラレル信号ごとの付加すべき遅延時間の最適値を求め、また、付加できる遅延時間の最大値または最小値が、設定遅延時間の最大値または最小値となるよう各最適値に一定の値を一括して加算または減算を行って設定遅延時間を求め、パラレル信号ごとの設定遅延時間を遅延回路2−1〜2−nへ指示する遅延時間最適化制御回路4と、を備える。

(もっと読む)

集積回路、集積回路システム、シリアルパラレル変換装置およびスキュー調整方法

【課題】簡単な回路または簡単な処理によりスキュー調整する。

【解決手段】集積回路3は、入力された外クロック信号を遅延させた内クロック信号を出力するクロック遅延回路43と、入力されたデータ信号を内クロック信号によりラッチするラッチ回路45と、クロック遅延回路43に対して、外クロック信号に対する内クロック信号の遅延量として、複数の遅延量を設定する遅延量設定回路58と、複数の遅延量それぞれの設定の下でのラッチ回路45の出力信号を判定するラッチ判定回路52と、ラッチ判定回路52による複数の遅延量それぞれについての複数の判定値を記憶する記憶部53と、記憶部53に記憶された複数の判定値とクロック遅延回路43に設定した複数の遅延量との関係から、クロック遅延回路43による内クロック信号の遅延量を取得する遅延量取得部とを有する。

(もっと読む)

クロック分配回路及びクロックスキュー調整方法

【課題】消費電力とクロックスキューを最小限に抑える。

【解決手段】クロック分配回路は、クロック分配領域に格子状に配置され、クロックメッシュを駆動する複数のクロックドライバと、各クロックドライバに対して格子状に割り当てた分割領域毎に、クロックドライバが駆動するクロックメッシュの配線容量及びクロックメッシュに接続した回路素子のクロック端子容量を抽出し、分割領域毎に抽出した総容量から必要なクロックドライバの駆動力を割り出して、ディジタルデータとして保持するクロックドライバ駆動力保持回路と、各分割領域内で必要なクロックドライバの駆動力保持データと、上下方向及び左右方向の分割領域内で必要なクロックドライバの駆動力保持データとをそれぞれ分割領域毎の抵抗比率により平均化して、クロックドライバの駆動力を調整するクロックドライバ駆動力制御回路とを有する。

(もっと読む)

可変遅延回路

【課題】簡単かつ小型な構成で、微小な遅延時間を高精度かつ広い可変遅延幅で連続的に設定する。

【解決手段】微動部および粗動部を遅延回路部として少なくとも2組と、各遅延回路部の切り替えを行う選択回路とを備えた可変遅延回路において、第1の遅延回路部の第1の微動部の遅延時間が最大値に設定される前に、第2の遅延回路部の第2の微動部の遅延時間を最小値に設定し、第1の遅延回路部の第1の微動部の遅延時間が最小値に設定される前に、第2の遅延回路部の第2の微動部の遅延時間を最大値に設定し、第1の遅延回路部と第2の遅延回路部の遅延時間が等しくなるように第2の遅延回路部の第2の粗動部の遅延時間を設定した後に、選択回路によって第1の遅延回路部から第2の遅延回路部に切り替える構成である。

(もっと読む)

メッシュクロック構造を生成するための装置及び構造

【課題】クロックスキューの低減と消費電力の低減を実現できるメッシュクロック構造を生成する。

【解決手段】メッシュクロック構造生成装置は、複数のノードを生成するノード生成部と、各々が複数のノードにクロック信号を供給するメッシュ構造のクロック配線を示す複数のメッシュクロック構造候補を生成するメッシュドライバ構造生成部とを備える。メッシュドライバ構造生成部は、複数のメッシュクロック構造候補の各々について消費電力の評価値を算出する消費電力評価部と、複数のメッシュクロック構造候補の各々についてクロック信号の遅延時間差の評価値を算出する遅延解析部とを備える。

(もっと読む)

半導体設計支援プログラム、半導体設計支援装置、および半導体設計支援方法

【課題】半導体装置におけるクロックジッタの低減ができる半導体設計支援装置を提供することを目的とする。

【解決手段】半導体設計支援装置100は、クロック信号が伝播する伝播遅延時間の調整対象となるクロック分配回路と、クロック分配回路に周期的なノイズの影響を与えるノイズ源のノイズ周期を特定する。そして、クロック分配回路のクロック信号の伝播遅延時間を特定する。そして、クロック信号の伝播遅延時間に調整時間を加えた調整後伝播遅延時間がノイズ周期の自然数倍となるように調整時間を決定する。クロック分配回路のクロック信号の伝播遅延時間を調整時間を加えた値とすることで、半導体装置におけるクロックジッタの低減ができる。

(もっと読む)

メモリモジュールのコントローラ

【課題】受信したクロック信号及びストローブ信号のタイミングを判断して判断結果を出力する機能を有するメモリモジュールのコントローラにおいて、当該機能を有効に活用可能なメモリコントローラを提供すること。

【解決手段】DDR3規格のメモリモジュールのコントローラ1であって、メモリモジュールから入力される信号の遅延を制御する遅延制御信号を出力するマスターDLL30と、ストローブ信号を遅延させて遅延ストローブ信号として出力するストローブ信号制御部40と、データ信号を遅延させて遅延データ信号として出力するデータ信号制御部50とを含む。

(もっと読む)

信号生成回路

【課題】 プロセス要因で生じるクロック信号の位相バラツキを抑える。

【解決手段】 信号生成回路100は、クロック信号PLLCKが通るクロック信号線30に1以上のクロックバッファ31が配置され、1以上のクロックバッファ31によりクロック信号PLLCKを遅延させ、遅延したクロック信号に基づき所定の信号を生成する。この信号生成回路100は、前記クロックバッファ31と同一チップ上に形成された複数のクロックバッファ41を有して構成される参照用クロックバッファ40と、参照用クロックバッファ40の遅延量を検知し、この遅延量と予め定められた遅延量との差に基づく位相調整信号PHADJを出力する遅延検知回路50と、位相調整信号PHADJに応じて、クロック信号PLLCKの位相を変える位相調整回路20と、を備える。

(もっと読む)

信号の較正方法および装置

信号較正方式において、一連の複数の信号の間で所望の位相関係が維持される。たとえば、いくつかの態様では、高速度の基準クロック信号から発生したクロックツリーの所望の位相を、低速度の基準クロック信号と、クロックツリーの様々な位相に関連付けられた低速度のクロック信号との間の位相差を検出することにより、維持することが可能である。いくつかの態様では、クロックツリーの使用中に発生するフレーミングオフセットを検出することにより、クロックツリーの所望の位相を維持することが可能である。 (もっと読む)

半導体集積回路の設計方法

【課題】レイアウト後のクロックのデューティ調整を容易に行なうことのできる、半導体集積回路の設計方法を提供する。

【解決手段】、クロックの両エッジで動作するセルへクロックを供給するセルとして初期配置セルを配置した後、クロックツリーの配置、クロック配線、セル間配線などのレイアウトを実行し、レイアウト実行後の実配線長にもとづくタイミング検証を行って、デューティ値の規定を満たさないデューティ違反が発生している初期配置セルを抽出し、デューティ違反の初期配置セルを、レイアウト上の配置位置はそのままで、外形サイズ、入出力端子位置、入力容量および出力駆動力が初期配置セルと同じで、デューティが規定値を満たすように調整されたデューティ調整セルに置換する。

(もっと読む)

半導体集積回路装置及びクロックスキュー計測方法

【課題】クロックスキューをより正確に計測できる半導体集積回路装置及びクロックスキュー計測方法を提供する。

【解決手段】LSI100内部のクロック信号を入力するクロック入力端子1と、クロックスキューを計測するためのクロックスキュー計測信号を入力する計測信号入力端子2と、クロック信号とクロックスキュー計測信号とが入力される複数のF/F3と、計測信号入力端子2から複数のF/F3にクロックスキュー計測信号を分配する複数の計測信号分配ドライバ7と、を備え、複数のF/F3は、複数のF/F群5に分けられ、F/F群5内の全てのF/F3は、同一の計測信号分配ドライバ7と直接に信号線のみを介して接続され、複数のF/F3の出力信号に基づいて、複数のF/F3間におけるクロックスキューを計測するように構成した。

(もっと読む)

1 - 20 / 50

[ Back to top ]