Fターム[5B125CA04]の内容

リードオンリーメモリ (43,397) | 目的、効果 (6,321) | 節電、低消費電力化、低電力化 (411) | 動作電流の低減 (221)

Fターム[5B125CA04]の下位に属するFターム

回路の間欠動作 (10)

Fターム[5B125CA04]に分類される特許

1 - 20 / 211

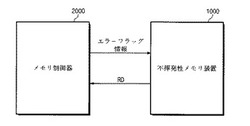

メモリシステム及びそれの動作方法

【課題】動作速度及び電力消耗を減らすことができるメモリシステム及びそれの動作方法が提供される。

【解決手段】本発明の実施形態によるメモリシステムは不揮発性メモリ装置と、前記不揮発性メモリ装置を制御するように構成されたメモリ制御器と、を含み、前記メモリ制御器は前記不揮発性メモリ装置から読み出されたデータのエラーの位置情報を含むエラーフラッグ情報を前記不揮発性メモリ装置へ提供する。

(もっと読む)

半導体記憶装置

【課題】消費電力を低減出来る半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、選択トランジスタ、メモリセル、ワード線、セレクトゲート線、ドライバ回路12、ロウデコーダ11−0、及び検知回路16を備える。ドライバ回路12は、第1電圧Vss,Vccを出力する。ロウデコーダ11−0内の第1転送トランジスタは、ワード線及びセレクトゲート線の各々に関連付けられ、ドライバ回路12から出力された第1電圧を、ワード線及びセレクトゲート線に転送する。検知回路16は、データの消去時において、ビット線及び/またはソース線に印加される第2電圧を検知して、検知結果に応じてフラグを生成する。ドライバ回路12は、フラグが生成されたことに応答して第1電圧の値を変更して、第1転送トランジスタをカットオフさせる。

(もっと読む)

半導体記憶装置

【課題】低消費電力化に有利な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルを備えるメモリセルアレイと、メモリセルの入力データまたは出力データをセンスするセンスアンプS/A0〜S/A7と、偶数側(Even Side)センスアンプと奇数側(Odd Side)センスアンプの間に、これらを電気的に分離するように配置されるラッチ回路22と、偶数側、奇数側センスアンプのいずれか一方に電気的に接続されるキャッシュメモリ23と、これらを制御する制御回路とを具備し、前記入力データの入力動作の際に、制御回路は、ラッチ回路の入力データを偶数側、奇数側センスアンプのいずれかへ転送させると共に、メモリの入力データを奇数側、偶数側センスアンプのいずれかへ転送させる。

(もっと読む)

フラッシュメモリ装置

【課題】低操作電圧および低電力消費量のフラッシュメモリを提供する。

【解決手段】フラッシュメモリ装置は、複数のメモリセルと、複数のプログラミング制御電圧生成器とを含む。各メモリセルは、制御エンドポイントを介してプログラミング制御電圧を受信し、プログラミング制御電圧に基づいてデータプログラミング操作を実行する。各プログラミング制御電圧生成器は、プリチャージ電圧送信機と、ポンピングキャパシタとを含む。プリチャージ電圧送信機は、第1期間中に、プリチャージイネーブル信号に基づいて、対応するメモリセルの制御エンドポイントにプリチャージ電圧を提供する。ポンプ電圧は、第2期間中にポンピングキャパシタに提供され、各メモリセルの制御エンドポイントでプログラミング制御電圧を生成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】読み出し動作を正確に実行する。

【解決手段】 制御回路は、メモリトランジスタの読み出し動作を実行する際、選択メモリトランジスタに接続される選択ワード線には、第1の電圧を印加する。選択メモリトランジスタを除く非選択メモリトランジスタに接続される非選択ワード線には、メモリトランジスタの保持データに拘わらずメモリトランジスタを導通させる第2の電圧を印加する。ビット線には、第3の電圧を印加する。ソース線のうち、選択メモリブロック中の前記選択メモリトランジスタが含まれるメモリストリングに接続される選択ソース線には第3の電圧より小さい第4の電圧を印加する。ソース線のうち、選択メモリブロック中の非選択のメモリストリングが接続される非選択ソース線には第3の電圧と略同一の第5の電圧を印加する。

(もっと読む)

昇圧回路を備えた半導体装置

【課題】回路面積を縮小でき、昇圧効率の高い昇圧回路を備える半導体装置を提供する。

【解決手段】出力電圧を監視するモニタ電圧MON1に基づいて、出力電圧を所定電圧に制御する制御回路と、出力電圧を通常動作時に第1電圧に設定し、評価時に第1電圧より高い第2電圧に設定するトランジスタTR4,TR5と、出力電圧の振幅をクロック信号の振幅としてクロック信号を発生するクロックドライバ11と、コンデンサ及びダイオードを含む単位回路21が直列に複数段接続され、コンデンサに入力されるクロック信号により電源電圧VCCを昇圧するチャージポンプ12とを備える。

(もっと読む)

不揮発性半導体メモリ

【課題】消費電力および消費電流を低減することが可能な不揮発性半導体メモリを提供する。

【解決手段】複数のメモリセルを含むメモリセルアレイと、入出力パッドと、メモリセルから読み出したデータを、入出力パッドを介して外部に出力し、且つ、外部から書き込みデータおよびコマンドを、入出力パッドを介して入力するためのI/O回路と、メモリセルの、書き込み、読み出し、又は消去動作に必要な第1の電源電圧が印加される第1の電源電圧パッドと、第1の電源電圧よりも低く且つI/O回路に供給するための第2の電源電圧が印加される第2の電源電圧パッドと、第1の電源電圧を降圧し、第2の電源電圧よりも高い第1の降圧電圧を出力する第1の降圧回路と、第2の電源電圧を降圧し、第1の降圧電圧よりも低い第2の降圧電圧を出力する第2の降圧回路と、第1の降圧電圧が供給される第1の内部回路と、第2の降圧電圧が供給される第2の内部回路を備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】消費電力を削減することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性メモリセルは、電気的に書き換え可能である。電源回路15a,15b,15cは、不揮発性メモリセルを駆動するポンプ回路を含んでいる。接地パッド14dには、接地電圧が供給される。第1の電源パッド14aには、第1の電源が供給される。第2の電源パッド14eには、第1の電源の電圧より高い第2の電源が供給される。降圧回路は、第2の電源パッドに接続され、第2の電源を降圧し、第2の電源より低い電圧を出力する。ポンプ回路は、第1の電源に基づき、第2の電源の電圧より高い電圧をする。

(もっと読む)

半導体メモリシステム

【課題】プログラムを並列化したときに消費電流のピーク期間の重なりを防止する。

【解決手段】実施形態に係わる半導体メモリシステムにおいて、複数の半導体メモリ1の各々は、連続する複数の動作を含む内部シーケンスを実行すると共に各動作の終了後に待機期間を有し、待機期間中に次の動作の開始を予告する2ビット以上の予告信号STAをメモリコントローラ28へ通知すると共に、メモリコントローラ28から内部シーケンスの再開命令を受けたときに次の動作を開始する。メモリコントローラ28は、複数の動作の各々について、動作期間及び消費電流のピーク期間に関する管理テーブルを備え、複数の半導体メモリ1のうち所定の半導体メモリから予告信号STAを受けたとき、管理テーブルに基づいて、所定の半導体メモリに対して再開命令を通知する。

(もっと読む)

半導体記憶装置

【課題】バス配線における消費電力を抑制する。

【解決手段】センスアンプ回路SAは、ビット線に接続されメモリセルから読み出される信号を検知増幅する。第1のデータラッチDL1,DL2は、センスアンプと第1のバスLBを介して接続される。第2のデータラッチDL3は、第2のバスGBに接続される。1つのセンスアンプ回路及び1つの第1のデータラッチをそれぞれ含む複数の回路群Gi(i=1〜j)が第1方向に沿って繰り返し設けられる。また、第2のデータラッチは、複数個の回路群と入出力バッファ5との間に設けられている。

(もっと読む)

MLCメモリセルのための方法および装置

【課題】MLCメモリセルの性能を向上させる。

【解決手段】マルチレベルセル(MLC)メモリセルのアレイを管理するための装置および方法である。さまざまな実施形態に従えば、選択されたMLCメモリセルの利用可能な複数の物理状態の各々に関連する書込努力に関して、複数の物理状態の各々に対して異なるマルチビット論理値を割り当てる非連続エンコーディングスキームが選択される。その後、選択された非連続エンコーディングスキームに関して、選択されたMLCメモリセルにデータが書込まれる。いくつかの実施形態においては、MLCメモリセルは、スピントルクトランスファランダムアクセスメモリ(STRAM)メモリセルを備える。他の実施形態においては、MLCメモリセルは、MLCフラッシュメモリセルを備える。

(もっと読む)

半導体記憶装置

【課題】VGA型半導体記憶装置のビット線ディスチャージ時の消費電力を低減する。

【解決手段】ビット線BL[0]〜[7]のディスチャージ時に、ビット線同士をビット線接続スイッチ00〜03で接続し、複数のビット線選択トランジスタ30〜37のうち一部のビット線選択トランジスタ30,32,34,36のみを導通させ、主ビット線MBL[0]及びディスチャージトランジスタ40を介して一部のビット線BL[0],[2],[4],[6]のみを接地電源に接続し、他のビット線BL[1],[3],[5],[7]はビット線接続スイッチ00〜03を介してディスチャージする。

(もっと読む)

電圧変換回路及び不揮発性半導体記憶装置

【課題】チャージポンプ回路を駆動するクロックバッファ回路に流れる瞬時電流を抑制すること。

【解決手段】

第1のトランジスタ(T11)のドレインを第1のキャパシタ(C11)によって第1の制御信号(DCLK10)に応じて昇圧駆動する第1のバッファと、第1のトランジスタ(T11)のゲートを第2のキャパシタ(C12)によって第2の制御信号(GCLK10)に応じて昇圧駆動する第2のバッファとから構成される電圧変換回路おいて、

第1のバッファは,第1の制御信号(DCLK10)の遷移時の駆動能力が,第2の制御信号(GCLK10)の遷移時の駆動能力よりも低いことを特徴とする電圧変換回路。

(もっと読む)

半導体記憶システム

【課題】 複数のチップを実装した場合において、消費電流の増加を抑制することが可能な半導体記憶システムを提供する。

【解決手段】 半導体記憶システムは、第1の半導体記憶装置71aと、第2の半導体記憶装置71bと、配線83とを有している。配線83は、第1の半導体記憶装置71aと第2の半導体記憶装置間71bに接続されている。第1、第2の半導体記憶装置71a,71bの一方が電荷を放電するとき、第1、第2の半導体記憶装置71a,71bの他方は、配線83を介して放電された電荷を受ける。

(もっと読む)

ワードライン昇圧回路、記憶装置、集積回路装置、及び電子機器

【課題】極低電圧でもワードラインを十分に昇圧することができるワードライン昇圧回路、記憶装置、集積回路装置、及び電子機器等を提供する。

【解決手段】メモリーセルMCを選択するためのサブワードラインSWLに供給される昇圧電圧を生成するワードライン昇圧回路140は、サブワードラインSWLに昇圧電圧を供給するp型の第1の駆動トランジスターTr10と、第1の駆動トランジスターTr10のソース電圧を第1の電源電圧VWLに基づいて生成するp型の第1の電圧供給トランジスターTr11と、第1の駆動トランジスターTr10のソースと第1の電圧供給トランジスターTr11のドレインを接続する第1の電源ラインSPL1と、第1の基準電圧と第1の電源ラインSPL1との間に挿入された第1の昇圧キャパシターBC1とを含む。

(もっと読む)

半導体記憶装置

【課題】ピーク電流を低減可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルが行および列に配置されるメモリセルアレイと、偶数の前記列に配置される複数の偶数ビット線と、前記偶数の前記列に隣接する奇数の前記列に配置される複数の奇数ビット線と、各々が前記奇数ビット線および偶数ビット線に選択的に接続される複数のセンスアンプ11とを具備し、前記センスアンプのそれぞれは、第1,第2ノードにデータを保持するようにラッチ接続される第1,第2インバータ回路68,69と、ゲートに電流制御信号が与えられ、電流経路の一端が第1電源電圧に接続され、電流経路の他端が前記第1,第2インバータ回路の制御端子にそれぞれ接続される第1,第2トランジスタP11,P12とを有するセンス部を備える。

(もっと読む)

昇圧回路

【課題】消費電流を低減可能な昇圧回路を提供すること。

【解決手段】本発明にかかる昇圧回路は、電源端子GNDと出力端子Voutとの間に、トランジスタM11〜M14と、ノードV24の電位に応じて導通状態が制御されるトランジスタM15と、を備え、トランジスタM11〜M15間の各接続点とクロック入力端子CLK1又はCLK2との間に容量素子C11〜C14を備え、電源端子GNDと出力端子Voutとの間に、トランジスタM21〜M24と、ノードV14の電位に応じて導通状態が制御されるトランジスタM25と、を備え、トランジスタM21〜M25間の各接続点とクロック入力端子CLK1又はCLK2との間に容量素子C21〜C24を備える。各トランジスタはトリプルウェル上に形成され、少なくともトランジスタM11〜M14,M21〜M24を形成する各トリプルウェルにてNウェル及びPウェル間は電気的に接続される。

(もっと読む)

参照メモリセルを利用した不揮発性メモリを読取る構造及び方法

【課題】従来技術における直流電流バイアスによる電流の大幅消耗を減少させ、又メモリセルのしきい電圧を迅速に且つ高解析度で検出する目的を達成する。

【解決手段】本発明は、参照メモリセルを利用したNVM読取構造を提供して、適切な検出速度及び良好な正確度により参照メモリセルMrf及び読取NVMセルMCの両者間のしきい電圧差を識別する。

(もっと読む)

昇圧回路

【課題】寄生トランジスタに流れる電流を低減し、消費電流の増大を抑制することが可能な昇圧回路を提供すること。

【解決手段】本発明にかかる昇圧回路は、低電位側電源端子GNDと出力端子Voutとの間に設けられたダイオード素子D1,D2と、ダイオード素子D1,D2と出力端子Voutとの間に設けられ、ダイオード素子D1,D2よりも順方向降下電圧の小さいダイオード素子D3と、ダイオード素子D1,D2,D3の間の各接続点に一端が接続され、他端にクロック信号CLK1,CLK2が供給される容量素子C1,C2と、を備える。

(もっと読む)

半導体記憶装置

【課題】メモリの状態に適した誤り訂正能力を有し、無駄な消費電力を省いたECC回路を備えたメモリを提供する。

【解決手段】メモリは、ビット線と、ワード線と、ビット線とワード線との交点に対応して設けられたメモリセルを含むメモリセルアレイとを備える。センスアンプは、ビット線に接続され、メモリセルに格納されたデータを検出する。ワード線ドライバは、ワード線の電圧を制御する。コントローラは、第1の誤り訂正能力を有する第1の誤り訂正回路および第2の誤り訂正能力を有する第2の誤り訂正回路を含む。メモリセルは、データ消去の単位となるメモリセルブロックを成し、メモリセルブロックにおいて各ワード線に接続されたメモリセルがページを成す。コントローラは、書込み時にワード線の電圧をステップさせる回数に応じて、読出し時または書込み時に第1の誤り訂正回路および第2の誤り訂正回路のうちいずれか一方またはそれらの両方を駆動させる。

(もっと読む)

1 - 20 / 211

[ Back to top ]