Fターム[5B125CA16]の内容

リードオンリーメモリ (43,397) | 目的、効果 (6,321) | 安定化、誤動作防止 (2,478) | 破壊防止、過電圧、過電流対処 (104)

Fターム[5B125CA16]に分類される特許

1 - 20 / 104

半導体集積回路及びその制御方法

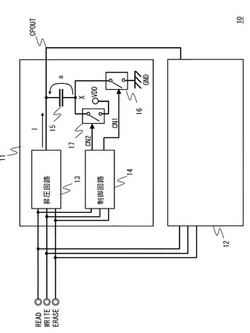

【課題】デカップリング容量素子の信頼性と、フラッシュメモリの動作モードに対応した供給電流の補償を損なわずに、フラッシュメモリの面積増加を抑制する。

【解決手段】本発明に係る半導体集積回路10は、フラッシュメモリ部12と、フラッシュメモリ部12に電圧を供給する昇圧回路13と、昇圧回路13の出力に一端が接続されたデカップリング容量素子15と、フラッシュメモリ部12の動作モードに応じて、デカップリング容量素子15の他端の電位を制御する制御回路14とを備える。

(もっと読む)

半導体記憶装置

【課題】動作信頼性を向上出来る半導体記憶装置を提供すること。

【解決手段】実施形態の半導体記憶装置1は、メモリセルアレイ10と、ビット線BLと、ソース線SLと、センス回路13とを備える。メモリセルアレイ10は、半導体基板40上に積層されたメモリセルMTが直列接続されたメモリストリング16を有する。ビット線BLは、いずれかのメモリストリング16に接続され、データを転送可能である。ソース線SLは、いずれかのメモリストリング16に接続され、データの読み出し時において、ビット線BLから読み出し電流が流れ込む。センス回路13は、ビット線BLに接続され、読み出しデータをセンスする。センス回路13の動作タイミングは、ソース線SLに流れる電流に基づいて決定される。

(もっと読む)

不揮発性半導体記憶装置

【課題】高集積化を図ることができる不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、セルの書き込みにおいて、制御装置は複数の第2の選択ゲートトランジスタに第1電位を与えた後、第1電位よりも低い第2電位を与える。複数のビット線のうち、書き込み不十分のセルに第3電位を与え、書き込み終了に間近のセルに第3電位より高い第4電位を与え、書き込みが終わったセルに第4電位より高い第5電位を与える。制御装置は、第2電位を与えた後、複数のワード線のうち選択されたワード線に書き込み電位を与え、第1電位は、第2の選択ゲートトランジスタをオンすることにより第3電位をNANDストリングに転送する電位であり、第2電位は、第3電位をNANDストリングに転送した後、前記第2の選択ゲートトランジスタをオフする電位である。

(もっと読む)

カップリングチャネルを使用したアンチヒューズメモリ及びその操作方法

【課題】カップリングチャネルを使用したアンチヒューズメモリ及びその操作方法を提供する。

【解決手段】カップリングチャネルを使用したアンチヒューズメモリは、第1導電型の基板と、第2導電型のドープ領域と、カップリングゲートと、ゲート誘電層と、アンチヒューズゲートと、アンチヒューズ層と、を含む。基板中に隔離構造を有する。ドープ領域が基板中に設置され、且つドープ領域及び隔離構造の間にチャネル領域を定義する。カップリングゲートがドープ領域及び隔離構造の間の基板上に設置され、且つカップリングゲートとドープ領域と隣り合う。ゲート誘電層がカップリングゲート及び基板の間に設置される。アンチヒューズゲートがカップリングゲート及び隔離構造の間の基板上に設置され、アンチヒューズゲート及びカップリングゲートの間に間隔を有する。アンチヒューズ層がアンチヒューズゲート及び基板の間に設置される。

(もっと読む)

不揮発性半導体記憶装置

【課題】読み出し動作を正確に実行する。

【解決手段】 制御回路は、メモリトランジスタの読み出し動作を実行する際、選択メモリトランジスタに接続される選択ワード線には、第1の電圧を印加する。選択メモリトランジスタを除く非選択メモリトランジスタに接続される非選択ワード線には、メモリトランジスタの保持データに拘わらずメモリトランジスタを導通させる第2の電圧を印加する。ビット線には、第3の電圧を印加する。ソース線のうち、選択メモリブロック中の前記選択メモリトランジスタが含まれるメモリストリングに接続される選択ソース線には第3の電圧より小さい第4の電圧を印加する。ソース線のうち、選択メモリブロック中の非選択のメモリストリングが接続される非選択ソース線には第3の電圧と略同一の第5の電圧を印加する。

(もっと読む)

半導体集積回路

【課題】不揮発性メモリを搭載した半導体集積回路において、外部端子を通して不揮発性メモリの特性テストを実施し、更に、その外部端子にサージ電圧が印加された場合であっても、そのサージ電圧が不揮発性メモリに伝わることを防止する。

【解決手段】半導体集積回路は、不揮発性メモリと、不揮発性メモリに対するデータ書き込み時、書き込み電圧が印加される書き込み制御線と、書き込み制御線に接続された第1ノードと、第1スイッチ回路を介して第1ノードに接続された外部端子と、スイッチ回路を介さずに外部端子に接続された第1ESD保護回路と、動作モードに応じて第1スイッチ回路をON/OFF制御する制御回路と、を備える。動作モードは、外部端子を用いて不揮発性メモリの特性テストを行うテストモードと、外部端子を使用しないユーザモードと、を含む。テストモードにおいて、制御回路は、第1スイッチ回路をONする。ユーザモードにおいて、制御回路は、第1スイッチ回路をOFFする。

(もっと読む)

NANDメモリ用デコーダ

【課題】NANDフラッシュメモリで使用する広い正負電圧範囲を有する高電圧スイッチを提供する。

【解決手段】高電圧スイッチはデコーダ信号を受信し、負第1バイアス電圧と正第2バイアス電圧により設定される第1電圧範囲のレベルシフター電圧出力を有するレベルシフターと、レベルシフターの出力に結合され、第1電圧範囲より広い正第3バイアス電圧と負第1バイアス電圧により設定される第2電圧範囲のプルアップ回路電圧出力を有するプルアップ回路とを備える。

(もっと読む)

読み出し装置

【課題】トランジスタを流れる電流を小さくすることができ、エレクトロマイグレーションやホットキャリアの問題を生じずにビット線の電位を読み出すことができる読み出し装置を提供する。

【解決手段】ワード線WLの電圧を制御する制御回路C1と、所望のワード線WLの電圧においてビット線(bit線)の電圧をセンスアンプ1により読み出し、その出力結果を基に制御回路C2によりビット線の電位を設定する回路を備える。トランジスタのゲート電圧を断熱的に変化させることにより、トランジスタを通って流れる電流を低減させる。

(もっと読む)

EEPROM

【課題】昇圧回路の残留電荷に起因する誤書き込みを防止することのできるEEPROMを提供する。

【解決手段】実施形態のEEPROMは、昇圧回路2が、メモリセルアレイ1に配列された不揮発性メモリセルへ供給する書き込み電圧として、チャージポンプ方式により電源電圧VDDよりも高い高電圧VPPを生成する。放電回路3が、昇圧回路2の出力端子と接地電位GNDの電源線との間に接続されたMOSトランジスタMT1を有しており、放電制御回路4が、リードイネーブル信号RE、待機信号ST、書き込み防止信号WR_PRTCTのいずれが入力されたときに放電指示信号DSCを出力して、放電回路3のMOSトランジスタMT1を導通させる。

(もっと読む)

不揮発性半導体記憶装置

【課題】安定した動作を実行可能な不揮発性半導体記憶装置法を提供する。

【解決手段】メモリストリングは、電気的に書き換え可能な複数のメモリトランジスタ、及びスペアメモリトランジスタを直列接続してなる。ワード線は、メモリトランジスタのゲートに接続されている。スペアワード線は、スペアメモリトランジスタのゲートに接続されている。メモリストリングは、第1半導体層、電荷蓄積層、複数の第1導電層、及び第2導電層を備える。第1半導体層は、基板に対して垂直方向に延びる第1半導体層を含む。電荷蓄積層は、第1半導体層の側面を取り囲む。複数の第1導電層は、電荷蓄積層を介して第1半導体層の側面を取り囲みワード線として機能する。第2導電層は、電荷蓄積層を介して第1半導体層の側面を取り囲み、スペアワード線として機能する。制御回路は、ワード線に代えてスペアワード線を駆動可能である。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルに与えられるストレスを緩和し、不揮発性半導体記憶装置の信頼性を高める。

【解決手段】不揮発性半導体記憶装置は、電気的書き換え可能な不揮発性メモリセルが配列されたメモリセルアレイと、制御部とを備える。制御部は、データ書き込みのため選択メモリセルに対し書き込みパルス電圧を印加する書き込み動作、データ書き込みが完了したか否かを確認する書き込みベリファイ動作、及びデータ書き込みが完了しなかった場合に書き込みパルス電圧を所定のステップアップ電圧の分だけ上昇させるステップアップ動作を繰り返す制御を司る。制御部は、書き込み動作中、少なくとも最初に発生させる第1の書き込みパルス電圧を第1の傾きで立ち上げた後、第1の書き込みパルス電圧の後に発生させる第2の書き込みパルス電圧を第1の傾きよりも大きい第2の傾きで立ち上げて書き込み動作を実行する。

(もっと読む)

不揮発性半導体記憶装置

【課題】安定した動作を実行可能な不揮発性半導体記憶装置法を提供する。

【解決手段】制御回路は、消去動作時、選択セルユニットに接続された第1配線の電圧を、選択セルユニットに含まれる第1トランジスタのゲートの電圧よりも第1電圧だけ大きくする。制御回路は、消去動作時、非選択セルユニットに接続された第1配線の電圧と、非選択セルユニットに含まれる第1トランジスタのゲートの電圧との間の電圧差を第1電圧と異なる第2電圧とする。また、制御回路は、消去動作時、選択セルユニット及び非選択セルユニットにおいて、ダミーメモリストリング中の少なくとも1つのダミーメモリトランジスタのゲートに第3電圧を印加し、ダミーメモリストリング中の別のダミーメモリトランジスタのゲートに第3電圧よりも低い第4電圧を印加する。

(もっと読む)

半導体メモリ

【課題】 メモリセルのしきい値のシフト量を正確に制御することができる半導体メモリを提供する。

【解決手段】 本発明の半導体メモリは、行列状に配列され、電荷を蓄積可能な複数のメモリセルを備えたメモリセルアレイ100と、メモリセルアレイの行方向のメモリセルを選択する行選択手段と、行選択手段によって選択されたメモリセルに書込みパルスを印加することによってデータの書込みを行う書込み制御手段とを有する。書込み制御手段は、時間的に連続する少なくとも第1および第2の書込みパルスP1、P2を印加するとき、第2の書込みパルスP2は、第1の書込みパルスP1の電圧よりも低い低電圧幅部分VpgmLと、第1の書込みパルスの電圧よりも高い高電圧幅部分VpgmHとを有する。

(もっと読む)

不揮発性メモリ、データ処理装置、及びマイクロコンピュータ応用システム

【課題】電源電圧レベルに対応して予め設定された複数の電源電圧モードにおいて不揮発性メモリの安定動作を図る。

【解決手段】メモリアレイ(149)と、チャージポンプ(152)と、上記チャージポンプの出力電圧を選択するディストリビュータ(151)と、上記チャージポンプと上記ディストリビュータとの動作を制御可能なシーケンサ(145)とを含んで不揮発性メモリ(14)を構成する。電源電圧レベルに対応して予め設定された複数の電源電圧モードの中から選択的に指定された電源電圧モードを上記シーケンサに指示するとともに、上記シーケンサに指示した電源電圧モードと、実際に供給された電源電圧との不整合を検出し、その検出結果に基づいて、上記シーケンサによる上記チャージポンプと上記ディストリビュータとの動作を制限可能なアナライザ(146)を設けることで、不揮発性メモリの安定動作を図る。

(もっと読む)

半導体装置

【課題】印加電圧の過剰による、アンチヒューズ素子の誤コネクトや書き込みが正確に行われないアンチヒューズ素子の発生を抑制する。

【解決手段】本発明の半導体装置は、アンチヒューズ素子の一端の電位AF_Gと電位VPPRとを比較し、電位AF_Gが電位VPPR以上の場合には、アンチヒューズ素子の一端に接続される電源線の電位VPPSVTを昇圧し、昇圧された電位によりアンチヒューズ素子の一端と他端とが導通状態となることで、電位AF_Gが電位VPPRよりも低くなった場合には、昇圧を停止する。

(もっと読む)

半導体装置

【課題】LSI内部の回路の動作状態が不安定なときに、誤って書き込み動作指示信号が入力されても、誤書き込みを回避する。

【解決手段】書き込み用の電源端子VPRGの電圧のレベルを検出するVPRGレベル検出回路4と、レベル検出回路からの検出信号IVPRGと、書き込み指示信号PRGE、クロック信号CLKにもとづき、書き込み制御信号WEと読み出し制御信号REを生成するW/Rコントロール回路5と、第1の電源端子VDD33の電源電圧と、電源VPRGとを受け、書き込み制御信号WEに基づき、書き込み時には、VPRGを選択し、書き込み時以外には、VDD33を選択しVPPとして出力する内部電源スイッチ回路6を備える。さらにアンチヒューズメモリセルアレイ7にはVPPとビット線間に接続され、書き込みデータDINと書き込み制御信号WEとに基づき、オン・オフされるスイッチを設ける。

(もっと読む)

半導体集積回路

【課題】 スイッチの信頼性を低下することなく、内部電圧線を所定の電圧に迅速に設定し、半導体集積回路の動作速度を向上する。

【解決手段】 半導体集積回路は、第1高電圧が供給される第1高電圧線を内部電圧線に接続するために第1スイッチ制御信号の活性化に応じてオンする第1スイッチと、第1高電圧を生成するために第1電圧生成信号の活性化に応じて動作する第1電圧生成回路と、第1電圧生成信号の活性化に応じて動作し、第1高電圧と内部電圧線の電圧とを比較し、第1高電圧と内部電圧線の電圧との差が所定値になったときに第1スイッチ制御信号を活性化するレベル比較器とを備えている。第1スイッチの両端に掛かる電圧を比較し、電圧差が小さくなったときに第1スイッチをオンすることで、第1スイッチの信頼性を低下することなく、内部電圧線を所定の電圧に迅速に設定できる。

(もっと読む)

電源切換回路、不揮発性記憶装置、集積回路装置及び電子機器

【課題】メモリーセルのデータが意図せずに書き換えられることを防止できる電源切換回路、不揮発性記憶装置、集積回路装置及び電子機器等を提供すること。

【解決手段】電源切換回路は、第1の高電位電源VPP及び第1の高電位電源VPPよりも低電位の第2の高電位電源VDDのいずれか一方を選択して、供給電源として出力する電源選択回路100と、切換制御信号SGに基づいて電源選択回路100を制御する制御回路200とを含む。制御回路200は、第1、第2の高電位電源VPP、VDDの電圧レベルが共に立ち上がるまでは、電源選択回路100が供給電源として第1の高電位電源VPPを出力しないように電源選択回路を制御し、第1、第2の高電位電源VPP、VDDの電圧レベルが共に立ち上がった後に、切換制御信号SGに基づいて、電源選択回路100が第1、第2の高電位電源VPP、VDDのいずれか一方を供給電源として出力するように電源選択回路100を制御する。

(もっと読む)

フラッシュメモリセルの自動昇圧システム

【課題】NANDストリングの異なったセルのプログラミングサイクル中にワードライン0に結合されたメモリセルのしきい値電圧のシフトを減らしたり、または防止する。

【解決手段】消去された領域の自己昇圧と局部的な自己昇圧方式を含む色々な異なった自己昇圧方式のいずれかで実施される。改造された消去された領域の自己昇圧方式では、低い電圧が選択されたワードラインのソース側の2本以上のワードラインに印加され、帯域から帯域へのトンネリングを低減すると共に2つの昇圧されたチャネル領域間の絶縁を改善する。改造された局部的な自己昇圧方式では、0ボルトまたは低い電圧が選択されたワードラインのソース側の2本以上のワードラインとドレイン側の2本以上のワードラインに印加されて、帯域から帯域へのトンネリングを低減すると共に選択されたワードラインに結合されたチャネル領域の絶縁を改善する。

(もっと読む)

記憶装置およびデータの書込み方法

【課題】2ビット以上のデータを多値化して記憶する記憶装置において、データ書込み処理の信頼性を改善する。

【解決手段】記憶装置1は、ページ単位でのデータ書き込みが可能な複数のページを有し、各ページに複数ページ分の書込みデータを多値化して記憶可能なメモリ16と、メモリ16に対してデータを書き込む場合、メモリ16の複数のページから書き込み先のページを選択し、選択したメモリ16のページに、当該書込みに係るデータのページを含む複数のページによる2ビット以上のデータを多値化して書き込む制御部12,14とを有する。複数ページ分の書込みデータをメモリ16に書き込む場合、制御部12,14は、当該複数ページ分の書込みデータを、ページ毎に別々に多値化し、メモリ16の互いに異なる未使用の複数のページに1ページずつ書き込む。

(もっと読む)

1 - 20 / 104

[ Back to top ]