Fターム[5B125DB12]の内容

リードオンリーメモリ (43,397) | 書込動作 (3,780) | 書込信号制御 (1,782) | 書込パルス電圧値制御 (722)

Fターム[5B125DB12]に分類される特許

1 - 20 / 722

メモリシステム及びそれのブロック複写方法

ホスト装置、装置、システム

不揮発性プログラマブルスイッチ

【課題】セル面積の小さい不揮発性プログラマブルスイッチを提供する。

【解決手段】第1配線に接続される第1端子と第2配線に接続される第2端子と第3配線に接続される第3端子とを有する第1不揮発性メモリトランジスタと、第4配線に接続される第4端子と第2配線に接続される第5端子と第3配線に接続される第6端子とを有する第2不揮発性メモリトランジスタと、第2配線にゲート電極が接続されたパストランジスタと、を備え、第1および第4配線が第1電源に接続され、第3配線が第1電源の電圧よりも高い電圧に接続されるときに第1不揮発性メモリトランジスタの閾値電圧が増加し、第2不揮発性メモリトランジスタの閾値電圧が低下し、第1および第4配線が第1電源に接続され、第3配線が第1電源の電圧よりも低い電圧に接続されるときに第1不揮発性メモリトランジスタの閾値電圧が低下し、第2不揮発性メモリトランジスタの閾値電圧が増加する。

(もっと読む)

不揮発性半導体メモリ素子、および不揮発性半導体メモリ装置

【課題】フローティングゲートへの電荷の蓄積と消去を容易に行え、またフローティングゲートの電荷を消去する場合にメモリセルの閾値を容易に制御できる、不揮発性半導体メモリ素子を提供する。

【解決手段】フローティングゲートへの電荷の蓄積時に、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットエレクトロンを半導体基板中に発生させ、フローティングゲートに電荷を注入する。また、フローティングゲートの電荷の消去時には、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットホールを発生させ、該ホットホールにより蓄積された電荷を消去する。また、フローティングゲートの電荷の消去時には、メモリセルのコントロールゲートとソース間の閾値が所望の値になるように制御しながら、電荷を消去する。

(もっと読む)

半導体記憶装置

【課題】読出速度が速い半導体記憶装置を提供する。

【解決手段】フラッシュメモリ3は、選択ビット線BLをプリチャージするプリチャージ回路45と、定電流源50と、電流検知型のセンスアンプ23と、選択ビット線BLがメモリアレイMA2に属する場合は、選択ビット線BLおよび定電流源50をそれぞれセンスアンプ23の入力ノードLBT,LBBに接続し、選択ビット線BLがメモリアレイMA3に属する場合は、選択ビット線BLおよび定電流源50を入力ノードLBB,LBTに接続する切換回路SWT2,SWB2,SWとを含む。したがって、ビット線BLのプリチャージとデータ読出を並列に実行できる。

(もっと読む)

不揮発性半導体記憶装置

【課題】閾値電圧分布の広がりを抑制した不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、メモリセル、ビット線、ワード線、及び制御回路を有する。メモリセルは、電気的にデータを書き換え可能に構成される。ビット線は、メモリセルの電流経路の一端に電気的に接続される。ワード線は、ビット線と交差する方向に配列されたメモリセルに共通に接続される。制御回路は、ワード線に書込電圧を印加してデータを書き込むべきメモリセルの閾値電圧を所定の閾値電圧以上になるまで移動させる書込動作を実行する。制御回路は、書込動作時に、ワード線に逐次上昇する書込電圧を印加しつつ、書き込むべきメモリセルの閾値電圧と書込電圧の印加回数との関係に基づいてビット線に印加する電圧を逐次変更する。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体メモリの情報書き換え方法

【課題】不揮発性半導体メモリの書き換え時に、適切なパルス電圧および適切なパルス幅を備える信号を印加可能な不揮発性半導体記憶装置を提供することである。

【解決手段】本発明にかかる不揮発性半導体記憶装置は、記録されている情報を所定のパルス電圧および所定のパルス幅を備える信号を印加することで書き換え可能な不揮発性半導体メモリ11と、不揮発性半導体メモリ11の書き換えを制御する書き換え制御部12と、を備える。書き換え制御部12は、不揮発性半導体メモリの総書き換え回数に基づき仮のパルス電圧および仮のパルス幅の少なくとも一つを決定する。更に、決定された仮のパルス電圧および仮のパルス幅の少なくとも一つを不揮発性半導体メモリ11の温度に基づいて補正することで、書き換え時に不揮発性半導体メモリ11に印加する信号のパルス電圧およびパルス幅の少なくとも一つを決定する。

(もっと読む)

メモリのプログラミング方法及びメモリアレイ

【課題】クリティカル・ディメンションの変動に鈍感であり且つ高速なメモリプログラミング方法等を提供する。

【解決手段】メモリの複数のメモリセルの夫々は、ウェルと、ソース及びドレイン領域と、記憶レイヤと、ゲートとを有する。メモリセルはマトリクス状である。同じ列ドレイン領域は同じビットラインへ接続し、同じ行ゲートは同じワードラインへ接続し、同じ列ソース領域は同じソースラインへ接続する。メモリは、いずれかのメモリセルへ電気的に接続されたワードラインへ第1の電圧を印加し、そのメモリセルへ電気的に接続されたビットラインへ少なくともプログラミング閾値だけ第1の電圧と異なる第2の電圧を印加し、そのメモリセルへ電気的に接続されたソースラインへ少なくともプログラミング閾値だけ第1の電圧と異なる第3の電圧を印加し、複数のメモリセルへ基板電圧を印加することによって、プログラミングされる。

(もっと読む)

不揮発性半導体記憶装置

【課題】多値書き込み時におけるメモリセルのしきい値分布の拡大を抑制する。

【解決手段】書き込み制御部7aは、レベルの高い第1のしきい値分布についての第1書き込み動作を行い、前記第1のしきい値分布の第1ベリファイ動作を行い、前記第1ベリファイ動作の結果に基づいて、第2書き込み動作を行い、前記第1のしきい値分布よりもレベルの低い第2のしきい値分布についての書き込み動作を開始する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルのしきい値分布の拡大を抑制しつつ、書き込みの高速化を図る。

【解決手段】書き込み制御部7aは、メモリセルの低レベル領域と高レベル領域を検索する条件ベリファイ動作を行い、条件ベリファイ動作以降の書き込み動作において前記低レベル領域と前記高レベル領域の書き込み電圧を共通に設定するとともに、前記低レベル領域と前記高レベル領域のビット線電圧を別個に設定する。

(もっと読む)

半導体記憶装置およびデータ書込み方法

【課題】MOS構造を有する各メモリセルにおいて信頼性が高い2ビットのデータの記憶が容易な半導体記憶装置およびデータ書込み方法を提供する。

【解決手段】MOS構造を有するメモリセル10は、ゲート電極13の第1半導体領域121側に設けられた第1記憶部141と、ゲート電極13の第2半導体領域122側に設けられた第2記憶部142とを有する。第1記憶部141に電子を保持させる第1電荷移動ステップと、第2記憶部142に電子を保持させる第2電荷移動ステップとを交互に行うことで、第1記憶部141および第2記憶部142の双方に所定量の電子を保持させる。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込み不良を低減させた不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、異なる複数の閾値電圧によって不揮発にデータを記憶するメモリセルを複数個有するメモリセルアレイと、前記メモリセルに対するデータ書き込みにおいて、前記メモリセルの閾値電圧を遷移させるプログラム動作、並びに、当該プログラム動作後の前記メモリセルの閾値電圧を検知するベイファイ動作、を有する書き込みループを実行する制御部とを備え、前記制御部は、前記複数の閾値電圧のうち最上位の前記閾値電圧に遷移させるデータ書き込みにおいて、前記メモリセルに対する書き込みループ数が第1回数よりも多くなった場合、前記書き込みループ数が前記第1回数以下の場合よりも前記ベリファイ動作がパスし易い条件を用いて前記ベリファイ動作を実行することを特徴とする。

(もっと読む)

不揮発性半導体記憶装置及び不揮発性半導体記憶装置のデータ書き込み方法

【課題】セル間干渉によるしきい値電圧の変動を低減させる。

【解決手段】不揮発性半導体記憶装置は、第1及び第2の選択ゲートトランジスタ、並びに第1及び第2の選択ゲートトランジスタ間に設けられ電気的に書き換え可能なデータを記憶する複数のメモリセルが直列接続されたメモリストリングからなるセルユニットと、メモリセルに第1の選択ゲートトランジスタ側から第2の選択ゲートトランジスタ側へ下位ページデータ及び下位ページデータに応じた上位ページデータを順次書き込むデータ書き込み手段とを備える。データ書き込み手段は、選択メモリセルに対して下位ページデータを書き込む第1の書き込み動作と、選択メモリセルに対して第2の選択ゲートトランジスタ側に隣接するn個(nは2以上の整数)の非選択メモリセルに対する第1の書き込み動作が終了した後に、選択メモリセルに対して上位ページデータを書き込む第2の書き込み動作とを行う。

(もっと読む)

不揮発性半導体記憶装置

【課題】データ書き込みを高速化した不揮発性半導体記憶装置を提供することを目的とする。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、メモリセルアレイと、プログラム動作並びにベリファイ動作を有する書き込みループを繰り返し実行する制御回路とを備え、ベリファイ動作は、メモリセルの閾値電圧が、メモリセルの所望の閾値電圧の下限を示す本ベリファイ電圧よりも低い値で設定された予備ベリファイ電圧まで遷移したことを確認する予備ベリファイステップ、並びに、メモリセルの閾値電圧が本ベリファイ電圧まで遷移したことを確認する本ベリファイステップからなり、書き込みループは、各データに対応した1又は2以上のベリファイ動作からなり、制御回路は、所定の第1条件を具備した後、所定のデータに対応したベリファイ動作の予備ベリファイステップを省略させた書き込みループを実行する。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択メモリセルに与える影響を緩和し、正確にデータを書き込むことのできる不揮発性半導体記憶装置を提供する。

【解決手段】一の実施の形態に係る不揮発性半導体記憶装置は、メモリセルアレイと、選択メモリセルに書き込みパルス電圧を印加するとともに非選択メモリセルに中間電圧を印加する書き込み動作、書き込みベリファイ動作及び書き込みパルス電圧を第1のステップアップ値だけ上昇させるステップアップ動作を繰り返す制御を実行する制御部とを備える。制御部は、書き込みパルス電圧の印加回数が第1の回数より少ない第1期間では中間電圧を一定の値に保ち、書き込みパルス電圧の印加回数が第1の回数以上である第2期間では中間電圧を第2のステップアップ値だけ上昇させるようにステップアップ動作を制御し、且つ、第2のステップアップ値に基づき第1のステップアップ値を決定する。

(もっと読む)

不揮発性半導体記憶装置

【課題】周辺回路の面積を縮小する。

【解決手段】

複数のメモリブロックの各々には、基板に対し垂直な方向に延びるように複数のメモリストリングが配列される。各メモリストリングは、複数のメモリトランジスタ及びダミートランジスタを直列接続してなる。ドレイン側選択ゲート線及びソース側選択ゲート線は、メモリブロックが選択されるときには転送トランジスタが導通することにより電圧を制御回路から供給される一方、メモリブロックが非選択とされるときは転送トランジスタが非導通状態となることによりフローティング状態とされる。ダミーワード線は、メモリブロックが選択されるときには第1の転送トランジスタが導通することにより制御回路から電圧を供給される一方、メモリブロックが非選択とされるときは第1の転送トランジスタとは別の第2の転送トランジスタにより電圧を供給される。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルの劣化による影響を考慮した読み出し動作を実行できる不揮発性半導体記憶装置を提供する。

【解決手段】一の実施の形態に係る不揮発性半導体記憶装置は、メモリセルアレイと、読み出し動作及び書き込みベリファイ動作を制御する制御回路とを備える。制御回路は、第1の場合に、選択ワード線に印加する電圧を第1の書き込みベリファイ電圧又は第1の読み出し電圧に設定して、動作を行う。制御回路は、第1の場合よりもメモリセルの劣化が進んだ第2の場合に、選択ワード線に印加する電圧を第2の書き込みベリファイ電圧又は第2の読み出し電圧に設定して、動作を行う。制御回路は、第1の書き込みベリファイ電圧の最大値と第1の読み出し電圧の最大値との差を、第2の書き込みベリファイ電圧の最大値と第2の読み出し電圧の最大値との差よりも大きい値に設定する。

(もっと読む)

不揮発性半導体記憶装置

【課題】容量素子が占有する回路面積の増大を抑制する。

【解決手段】メモリストリングは、複数の第1導電層、メモリゲート絶縁層、及び半導体層を有する。複数の第1導電層は、半導体基板に対して実質的に垂直方向に所定ピッチをもって配列され、メモリトランジスタのゲートとして機能する。半導体層は、複数の第1導電層と共にメモリゲート絶縁層を一方の側面で挟み、半導体基板に対して実質的に垂直方向に延び、メモリトランジスタのボディとして機能する。第1キャパシタは、複数の第2導電層を有する。複数の第2導電層は、半導体基板に対して実質的に垂直方向に所定ピッチをもって配列され、第1キャパシタの電極として機能する。制御回路は、複数の第1導電層に印加される電圧に応じて、複数の第2導電層の各々に印加する電圧を制御し、これにより第1キャパシタの容量を変化させる。

(もっと読む)

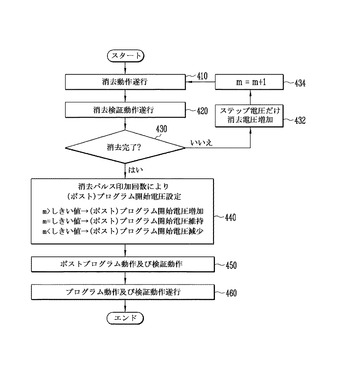

不揮発性メモリ装置のプログラム方法

【課題】 本発明の不揮発性メモリ装置のプログラム方法は、各セルのプログラム速度に応じてプログラム開始電圧を異なって設定する不揮発性メモリ装置のプログラム方法を提供することを目的としている。

【解決手段】 消去動作を行う段階と、前記消去動作が完了するまで消去パルス印加回数をカウントする段階と、前記カウントされた消去パルス印加回数としきい値を比較してプログラム開始電圧を設定する段階と、前記設定されたプログラム開始電圧に応じてプログラム動作を行う段階とを含む構成としたことを特徴とする。

【選択図】 図4  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】動作信頼性を向上出来る半導体記憶装置を提供すること。

【解決手段】実施形態の半導体記憶装置1は、メモリセルMTと、複数のワード線WLと、ドライバ回路12と、制御回路15とを備える。メモリセルMTは、半導体基板20上に積層されると共に、電流経路が直列接続され、電荷蓄積層25bと制御ゲート23a〜23dとを含む。ワード線WLは、制御ゲートにそれぞれ接続される。ドライバ回路12は、選択ワード線に第1電圧VPGMを印加すると共に、第1非選択ワード線に第2電圧VPASSAを印加し、第2非選択ワード線に第3電圧VPASS、VISOを印加するプログラム動作を繰り返すことにより、選択ワード線に接続されたメモリセルMTにデータを書き込む。制御回路15は、プログラム動作が繰り返される過程において、第1電圧VPGMを上昇させ、第2電圧VPASSAを低下させる。

(もっと読む)

1 - 20 / 722

[ Back to top ]