Fターム[5B125DE17]の内容

リードオンリーメモリ (43,397) | その他の動作 (2,583) | キャッシュ動作 (134)

Fターム[5B125DE17]に分類される特許

1 - 20 / 134

メモリカード、ストレージメディア、及びコントローラ

不揮発性半導体メモリおよびそのデータの読出し方法

ホスト装置、装置、システム

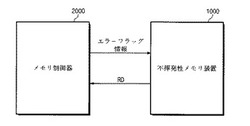

メモリシステム及びそれの動作方法

【課題】動作速度及び電力消耗を減らすことができるメモリシステム及びそれの動作方法が提供される。

【解決手段】本発明の実施形態によるメモリシステムは不揮発性メモリ装置と、前記不揮発性メモリ装置を制御するように構成されたメモリ制御器と、を含み、前記メモリ制御器は前記不揮発性メモリ装置から読み出されたデータのエラーの位置情報を含むエラーフラッグ情報を前記不揮発性メモリ装置へ提供する。

(もっと読む)

半導体ディスク寿命監視装置

【課題】不揮発性の半導体ディスクの寿命を監視する半導体ディスク寿命監視装置を提供する。

【解決手段】半導体ディスク5−1〜5−Kの書込み制御を行うファイルシステム3と、当該ファイルシステム3と前記半導体ディスク5−1〜5−Kを接続するインタフェースドライバ4を備え、当該インタフェースドライバ4により書込みが行われる半導体ディスク5−1〜5−Kの寿命を予測する半導体ディスク寿命監視装置1であって、前記ファイルシステム3からの書込みを書込情報として測定する測定部7と、前記測定結果を累積し第1の保存データ32として保存する保存部8と、前記保存した累積書込情報に基づいて、半導体ディスク5−1〜5−Kの寿命を予測する。

(もっと読む)

不揮発性メモリ装置のデータリード方法、及びそれを行う装置

【課題】新たなリードパラメータで不揮発性メモリ装置をリードするリードリトライを行う方法、該方法を行う装置を提供する。

【解決手段】リードリトライ動作及び/またはその部属的なリードリトライ動作は、リードリトライ動作が保証(warranted)されるか否かを判断する前に初期化されるか、完了することができる。例えば、NANDフラッシュメモリ装置のページは、新たなリード電圧レベルをページのワードラインに印加して、リードリトライ動作でリードされうる。例えば、リードリトライ動作は、エラー訂正動作でターゲットページのデータの以前リードページのエラーを訂正不能と判断される前に、ターゲットページで行われる。

(もっと読む)

メモリシステム

【課題】

実施形態は、動作効率の低減を防止可能なメモリシステムを提供する。

【解決手段】

本実施形態のメモリシステムによれば、半導体チップの内部温度とアクセス可否とを対応づけたデータを保持する第1記憶部と、前記半導体チップの内部温度を計測する温度計測部と、前記データから、計測された内部温度に対応するアクセス可否を算出し、アクセス可の半導体チップに対して、シーケンスを実行し、アクセス否の半導体チップに対して、シーケンスを実行しない制御部とを備えることを特徴とする。

(もっと読む)

半導体記憶装置

【課題】1つの実施形態は、例えば、出荷後においてメモリセルの動作特性を変更できる半導体記憶装置を提供することを目的とする。

【解決手段】1つの実施形態によれば、メモリセルアレイと記憶部と選択部と起動処理部と動作制御部とを有することを特徴とする半導体記憶装置が提供される。メモリセルアレイでは、複数のメモリセルが配列されている。記憶部は、選択される候補となる複数の動作パラメータを予め記憶する。選択部は、ユーザからの変更指示に応じて、前記複数の動作パラメータのうち前記メモリセルを動作させるために使用すべき動作パラメータを選択する。起動処理部は、ユーザからの起動指示に応じて、電源を起動するとともに、前記選択部により選択された動作パラメータを前記記憶部から読み出して使用可能な状態に設定する。動作制御部は、前記起動処理部により使用可能な状態に設定された動作パラメータを使用して、前記メモリセルを動作させる。

(もっと読む)

半導体記憶システム

【課題】 複数のチップを実装した場合において、消費電流の増加を抑制することが可能な半導体記憶システムを提供する。

【解決手段】 半導体記憶システムは、第1の半導体記憶装置71aと、第2の半導体記憶装置71bと、配線83とを有している。配線83は、第1の半導体記憶装置71aと第2の半導体記憶装置間71bに接続されている。第1、第2の半導体記憶装置71a,71bの一方が電荷を放電するとき、第1、第2の半導体記憶装置71a,71bの他方は、配線83を介して放電された電荷を受ける。

(もっと読む)

ページ内・ページ間オンチップデータ擬似ランダム化のための不揮発性メモリおよび方法

【課題】集積回路メモリチップ内の機構により、不揮発性メモリセルアレイに蓄積されるデータのスクランブリングまたはランダム化を可能にする。

【解決手段】一実施形態において、検知中のソース負荷誤差と近傍セルのフローティングゲート間結合を抑制するため、ページ内ランダム化を役立てる。ページ単位ランダム化は、特定のデータパターンが繰り返し長期間にわたり蓄積されることから生じるプログラムディスターブ、ユーザリードディスターブ、フローティングゲート間結合を抑えるのに役立つ。別の実施形態では、ページ内ランダム化とページ単位ランダム化の両方を実施する。実施形態によってはスクランブリングまたはランダム化が予め決定されるか、あるいは符号生成擬似ランダム化となるか、あるいはユーザ主導ランダム化となる。これらの機構は、集積回路メモリチップの限られたリソースおよびバジェットの中で達成される。

(もっと読む)

半導体記憶装置

【課題】 各種のデータ転送が可能な半導体記憶装置を提供する。

【解決手段】 メモリセルアレイ10は、複数の不揮発性メモリセルが配置されている。RAM(Random Access Memory)30は、メモリセルアレイ10に書き込まれるデータ、又は読み出されたデータを保持する。制御部4は、RAMを用いた第1の動作モードと、RAMを用いない第2の動作モードを制御する。データ転送部17は、第2の動作モードにおいて、データの書き込み時、データバスDIRを介して入出力部40から供給されたデータをバッファ部12に転送し、バッファ部12に転送されたデータをエラー訂正部20に転送し、エラー訂正部20において、生成されたパリティデータをバッファ部12に転送する。

(もっと読む)

半導体記憶装置

【課題】セットアップ及びホールド時間のマージンを確保する。

【解決手段】半導体記憶装置1は、第1のクロックを受け、かつデータの入出力を行う第1のバッファ12を有する第1のメモリ10と、データの入出力を行う第2のバッファ22を有する第2のメモリ20とを含む。第1のメモリ10は、第1のクロックを用いて第2のメモリ20に第2のクロックを転送する。第1のバッファ12は、第1のクロックに応答して第2のメモリ20にデータを転送する。第2のバッファ22は、第2のクロックに応答してデータを受ける。

(もっと読む)

半導体記憶装置、及び記憶媒体

【課題】ガベージコレクション処理による処理負荷を軽減し、ガベージコレクション処理の処理時間を短縮する。

【解決手段】フラッシュメモリ10は、予め定められたデータサイズ領域を示すページ単位でデータを書き込み可能な不揮発性記憶部11と、不揮発性記憶部11の指定された領域であって、複数のページを含む該指定された領域における有効データを一時記憶する記憶部12と、不揮発性記憶部11のページに有効なデータがあるか否かを示すアドレスマップ情報に基づいて、指定された領域における有効データを記憶部12に記憶させた後に、記憶部12に記憶された有効データを連続したページに書き込むガベージコレクション処理、及びガベージコレクション処理によって変更されたアドレスマップ情報を出力する処理を実行するコントロールロジック部13とを備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】ブートロードを必要とするシステムに用いる不揮発性半導体記憶装置においてブートロード時間を短縮することを課題とする。

【解決手段】ブートデータを記憶した記憶領域10aと、ブートデータを格納する第1のRAM(ブートRAM21)と、ブートデータが第1のRAMの記憶容量を超える場合にブートデータのうちの残りのデータを格納する第2のRAM(バッファRAM22またはバッファRAM23)と、第2のRAMに格納動作をさせるか否かを示すフラグ情報と、第2のRAMに格納されるブートデータの第1の記憶領域における位置を示すアドレス情報と、を記憶した不揮発性領域40と、ブートデータを第1の記憶領域から第1のRAMへ転送し、続いて、フラグ情報とアドレス情報に基づいて、ブートデータの残りのブートデータを第1の記憶領域から第2のRAMへ転送する制御部30と、を備える。

(もっと読む)

メモリシステム

【課題】SLCフラッシュメモリとMLCフラッシュメモリとのそれぞれのメリットを状況に応じて得る。

【解決手段】実施の形態によるメモリシステム1は、MLCフラッシュメモリ112と、ブロック管理部102と、転記部(107、108および109)と、を備える。MLCフラッシュメモリ112は、SLCモードおよびMLCモードのいずれでもデータの書込みが可能な複数のブロックを含む。ブロック管理部102は、有効データを格納しないブロックをフリーブロックとして管理する。転記部は、ブロック管理部102が管理するフリーブロックの数が所定の閾値Tbf以下である場合、有効データを格納する1つ以上の使用ブロックを転記元ブロックとして選択し、転記元ブロックに格納されている有効データをフリーブロックにMLCモードで転記する。

(もっと読む)

複合メモリ

【課題】 製造コストの上昇を招くことなくNANDフラッシュメモリにDRAMを混載することができ、且つチップ面積の増大を招くことなくシステム性能の向上をはかる。

【解決手段】 半導体基板10上に、NANDセルユニットからなる第1のメモリセルアレイとDRAMセルからなる第2のメモリセルアレイとを搭載した複合メモリであって、NANDセルユニットは、第1のゲート14と第2のゲート16を積層した2層ゲート構成の不揮発性メモリセル100と不揮発性メモリセル100の第1及び第2のゲート14,16間を接続した選択トランジスタ200で構成され、DRAMセルは、選択トランジスタ200と同じ構成のセルトランジスタ300と、不揮発性メモリセル100又は選択トランジスタ200と同じ構成のMOSキャパシタ400で構成されている。

(もっと読む)

多値不揮発性半導体メモリシステム

【課題】コントローラから不揮発性半導体メモリへのデータ転送時間を短縮する。

【解決手段】実施形態に係わるメモリシステムは、x(xは3以上の整数)ビットを記憶する複数のメモリセルを有し、2x個の閾値分布にビット割り付けが行われるメモリセルアレイ11を備える不揮発性半導体メモリ1と、書き込み時に不揮発性半導体メモリ1の動作を制御するコントローラ2とを備える。コントローラ2は、第1、第2及び第3ステップにより書き込みを実行し、第1ステップにより2y個(yは整数、かつ、y<x)の閾値分布を生成し、第2及び第3ステップにより2x個の閾値分布を生成し、第1ステップ時にxビットに基づいて2y個の閾値分布を生成するためのyビットを生成するデータ変換回路22を備え、第1ステップ時にyビットを不揮発性半導体メモリ1に転送する。

(もっと読む)

不揮発性半導体記憶装置

【課題】 本実施形態は、消去動作中に読み出し又は書き込み動作要求が発生した場合、要求発生から短時間で読み出し又は書き込み動作を実行することが可能であり、しかも、消去動作再開後、過消去状態の発生を防止可能な不揮発性半導体記憶装置を提供する。

【解決手段】 メモリセルアレイ1は、複数のメモリセルがマトリックス状に配置されている。制御部7は、メモリセルMCのデータを消去する。制御部7は、メモリセルMCの消去動作中に、第1のコマンドに応じて消去動作を中断させ、前記中断前の消去条件を保持し、第2のコマンドに応じて保持された消去条件に基づき消去動作を再開させる。

(もっと読む)

データ処理装置

【課題】チップ占有面積の増大及び消費電力増大を生ずることなく、比較的容易にオンチップのEEPROMのリードアクセスを高速化することができるデータ処理装置を提供する。

【解決手段】データ処理装置にオンチップされた前記不揮発性メモリには、不揮発性メモリセルのアレイ(10)からロウアドレス系選択動作でビット線に読み出されたデータの全部又は一部をラッチするプリリードキャッシュ部(15)と、プリリードキャッシュ部にラッチされたデータの一部をカラム系選択動作で選択する選択回路(16)とを設け、プリリードキャッシュ部にラッチされたデータのアドレス情報を保持し、保持したアドレス情報と同一のアドレス情報による不揮発性メモリに対するリードアクセスに際してプリリードキャッシュ部への新たなデータのラッチを抑制すると共に、プリリードキャッシュ部にラッチされているデータを前記選択部に選択させる制御を行う。

(もっと読む)

インターフェース回路及びインターフェース回路を備えるメモリコントローラ

【課題】ロックアップ時間無しでDDRインターフェースを備えたメモリにアクセスすることのできるインターフェース回路及びインターフェース回路を備えるメモリコントローラを提供する

【解決手段】データストローブ信号(DQS)の周期が基本クロックの周期の4n倍(nは1以上の整数)になるようにする。このようにすることにより、データストローブ信号(DQS)がハイレベルの期間又はローレベルの期間は、基本クロックの2n周期分の期間と一致する。そして、データストローブ信号(DQS)の立ち上がりエッジ又は立ち下がりエッジから基本クロックのn周期分に対応する時間が経過した時点を中心として、半周期分未満の時間差で読み出しデータ(DQ)の信号がラッチする。

(もっと読む)

1 - 20 / 134

[ Back to top ]