Fターム[5C024GZ01]の内容

光信号から電気信号への変換 (72,976) | 撮像素子の細部(信号読出し) (2,481) | 電荷の外部への排出、除去 (602)

Fターム[5C024GZ01]の下位に属するFターム

ドレイン、オーバーフロードレイン (349)

Fターム[5C024GZ01]に分類される特許

1 - 20 / 253

光電変換装置のリセット方法と、光電変換装置、光電変換アレイ、および撮像装置

イメージセンサおよび制御方法

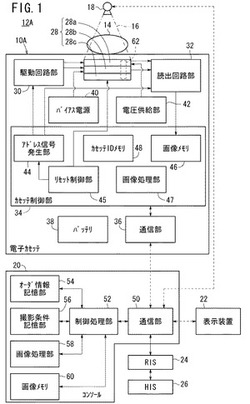

放射線撮影装置

【課題】放射線画像を取得できない状態が発生しないようにリセット処理を実行する。

【解決手段】放射線撮影装置(10A)は、放射線(16)の入射方向に沿って積層され、該放射線(16)を放射線画像に変換可能な2つの放射線変換パネル(28a、28b)と、2つの放射線変換パネル(28a、28b)に対して残像の発生を抑制するためのリセット処理を実行可能なリセット処理部(28c、30、32、40)と、2つの放射線変換パネル(28a、28b)に対するリセット処理を互いに異なる時間帯に実行するようにリセット処理部(28c、30、32、40)を制御するリセット制御部(45)とを有する。

(もっと読む)

放射線撮影装置

【課題】放射線画像を取得できない状態が発生しないようにリセット処理を実行する。

【解決手段】放射線撮影装置(10A)は、放射線(16)を放射線画像に変換可能な少なくとも1つの放射線変換パネル(28a、28b)と、放射線変換パネル(28a、28b)に対して残像の発生を抑制するためのリセット処理を実行可能なリセット処理部(30、32)と、放射線変換パネル(28a、28b)内の少なくとも2つの領域に対するリセット処理を互いに異なる時間帯に実行するようにリセット処理部(30、32)を制御するリセット制御部(45)とを有する。

(もっと読む)

撮像装置および撮像表示システム

【課題】撮像画像の高画質化を実現することが可能な撮像装置、およびそのような撮像装置を備えた撮像表示システムを提供する。

【解決手段】撮像装置は、各々が光電変換素子と電界効果型のトランジスタとを含む複数の画素を有する撮像部と、トランジスタのオン動作およびオフ動作を切り替えることにより、画素内に蓄積された信号電荷の読み出し駆動およびリセット駆動を行う駆動部とを備える。リセット駆動を1フレーム期間内で間欠的に複数回行い、トランジスタのゲートに対し、1フレーム期間の1回目のリセット駆動時には第1の電圧、他の回のリセット駆動時には、第1の電圧よりも低い第2の電圧を印加してトランジスタのオン動作を行う。各画素において光電変換がなされ、信号電荷の読み出し駆動およびリセット駆動がなされ、入射光に基づく撮像画像が得られる。リセット駆動時に生じるチャージインジェクションを低減する。

(もっと読む)

光検出素子、光検出素子の制御方法

【課題】光電変換部での飽和の可能性を低減して光電変換部の小型化を可能にし、全体としてのサイズの小型化を可能にする。

【解決手段】分離電極14aと蓄積電極14bとが障壁制御電極14cを挟んで配置される。分離電極14aと蓄積電極14bと障壁制御電極14cとに正極性の電圧が印加されてウェル12にポテンシャル井戸が形成された状態で光照射による電子が集積される。その後、障壁制御電極14cに印加された電圧に応じて形成されるポテンシャル障壁の高さが調節されることにより、規定した一定量の不要電荷が電荷分離部で分離される。電子の集積と不要電荷の分離とが複数回繰り返された後、蓄電電極14bに対応して形成された電荷蓄積部に流れ込んだ有効電荷が受光出力として取り出される。

(もっと読む)

画素をバーストリセット動作と統合することにより改善された性能を有するCMOSイメージセンサ

【課題】小型画素及び高性能CMOSイメージセンサアレイで使用することができる実質

的な画素設計を提供すること。

【解決手段】本発明のリセットトランジスタは、電荷を検出するフローティング拡散領域

と、電荷を排出する接合領域と、リセット信号の制御を受けて、前記フローティング拡散

領域から前記接合領域への電荷転送を制御するゲートと、該ゲートの下部に統合された電

位井戸とを備えることを特徴とする。

(もっと読む)

撮像装置および撮像表示システム

【課題】撮像駆動の際の動作の自由度を向上させることが可能な撮像装置等を提供する。

【解決手段】撮像装置は、各々が光電変換素子を含む複数の画素を有する撮像部と、光電変換素子により得られた信号電荷を画素から読み出す読み出し動作を線順次で行うための線順次読み出し駆動と、画素内の信号電荷をリセットするためのリセット動作を線順次で行うための線順次リセット駆動とを行う駆動部とを備えている。駆動部は、線順次リセット駆動を、1フレーム期間内で間欠的に複数回行う。また、一の線順次リセット駆動の際の駆動期間と他の一の線順次リセット駆動の際の駆動期間とのオーバーラップ期間内におけるリセット動作の期間において、上記一の線順次リセット駆動による各リセット動作と上記他の一の線順次リセット駆動による各リセット動作とがいずれも重ならない非オーバーラップ期間が少なくとも一部に設けられるように、複数回の線順次リセット駆動を行う。

(もっと読む)

固体撮像素子および電子機器

【課題】より良好な色再現性を有する固体撮像素子および電子機器を提供する。

【解決手段】同一の半導体基板22の内部における1画素ごとに、それぞれ異なる深さに、それぞれ異なる波長域の光を光電変換する複数の光電変換領域23B、23G、23Rが積層され、複数の光電変換領域23B、23G、23Rのうち、半導体基板の深さ方向に隣接する光電変換領域23Bおよび23G、または23Gおよび23Rの間に、その光電変換領域23Bおよび23G、または23Gおよび23Rの間の領域における光電変換で発生した電荷を排出する排出領域24が形成される。

(もっと読む)

固体撮像装置、電子機器、及び、固体撮像装置の製造方法

【課題】 例えばブルーミングや混色などの発生をさらに抑制することのできる固体撮像装置を提供する。

【解決手段】 本開示の固体撮像装置100では、キャリア極性が第1の導電型である第1不純物層5を含む光電変換部11上に、キャリア極性が第2の導電型である第2不純物層6、及び、キャリア極性が第1の導電型である第3不純物層7をこの順で形成する。さらに、第3不純物層7を不純物領域部16と接続し、かつ、第3不純物層7を覆うようにゲート電極3を形成する。この構成により、光電変換期間中に、光電変換部11から第2不純物層6を介して第3不純物層7に向かう方向に余剰電子のオーバーフロー経路を形成して光電変換部11の余剰電子を排出する。

(もっと読む)

固体撮像装置

【課題】飽和信号レベルの低下を抑制しつつ、ブルーミングを低減する。

【解決手段】画素アレイ部1は、光電変換した電荷を蓄積する画素PCがマトリックス状に配置され、垂直駆動回路2は、各画素のPCの蓄積期間に画素PCを複数のラインごとに一括して駆動し、画素PCに蓄積された所定レベル以上の電荷を排出させる。前記垂直駆動回路は、前記画素の読み出し期間に前記画素を1ラインごとに駆動し、前記画素に蓄積された全ての電荷を読み出させる。

(もっと読む)

固体撮像装置

【課題】画素の駆動精度を低下させることなく、高速に連続してグローバルシャッタ動作を行う固体撮像装置を提供する。

【解決手段】光電変換素子を有する単位画素が1次元又は2次元に配列された画素アレイと、前記単位画素に与えられる信号電圧を選択的に切り換える切換スイッチと、第1信号電圧、第1信号電圧より高い第2信号電圧、及びその第3信号電圧を、前記切換スイッチを切り換えて選択的に前記単位画素に印加して前記単位画素を駆動する画素駆動部とを備え、前記画素駆動部は、前記第1信号電圧と前記第2信号電圧とを交互に前記複数の単位画素に印加するとともに、前記第1信号電圧から前記第2信号電圧に切り換える際、及び、前記第2信号電圧から前記第1信号電圧に切り換える際に、前記単位画素に前記第3信号電圧を経由して印加することで、複数の前記単位画素の前記光電変換素子に発生する前記光電子の蓄積、保持、転送、リセット、排出のいずれかを一斉に行う。

(もっと読む)

固体イメージセンサおよびその製造方法

【課題】チップサイズ・パッケージを持ち、容易に製造することができる固体イメージセンサである。

【解決手段】受光素子層(20)の半導体基板(21)に複数の画素領域に対応して素子形成領域を形成し、それら素子形成領域内に半導体受光素子(PD)を形成して、透光性絶縁膜(25a)、(25b)、(26)で覆う。絶縁膜(26)上に、複数のマイクロレンズ(43)を内蔵した光導入用キャビティ(42)と、それを閉鎖する石英キャップ(51)を持つ光導入層(40)を形成する。半導体受光素子(PD)の出力電気信号は、半導体基板(21)の埋込配線を介してその底面に取り出し、出力層(10)またはインターポーザ(10A)を介して固体イメージセンサの外部に取り出す。

(もっと読む)

撮像装置

【課題】像消失期間を短縮することができる撮像装置を提供する。

【解決手段】撮像装置は、静止画撮影による画素信号の読み出しと動画撮影による画素信号の読み出しとを並行して行うことが可能である。動画撮影の露光開始時刻から静止画撮影の露光期間内の所定の時刻までに画素28の光電変換素子に蓄積された第1の信号電荷に基づく第1の画素信号と、所定の時刻から動画撮影の露光終了時刻までに画素28の光電変換素子に蓄積された第2の信号電荷に基づく第2の画素信号とが読み出される。加算器29は、第1の画素信号と第2の画素信号とを加算し、加算後の画素信号を動画用信号として出力する。

(もっと読む)

固体撮像装置および固体撮像装置の駆動方法

【課題】出力特性のばらつきを抑えつつ、遅延効果による課題を解決することができる固体撮像装置、および固体撮像装置の駆動方法を提供する。

【解決手段】制御部6は、M行のうち或る行を構成する各画素Pm、nの読出用スイッチSW1を接続状態とすることによって、当該行において発生した電荷を積分回路Snに入力させ、積分回路Snから出力された電圧値を第1の保持回路HO1、nに保持させたのち、転送用スイッチSW32を接続状態にして該電圧値を第2の保持回路HO2、nに転送し、その後、該電圧値を第2の保持回路HO2、nから順次に出力させる動作と、M行のうち他の行を構成する各画素Pm+1、nの読出用スイッチSW1を接続状態とすることによって、当該行において発生した電荷を積分回路Snに入力させる動作とを並行して実施する。

(もっと読む)

放射線画像撮影装置、放射線画像撮影プログラム、及び放射線画像撮影方法

【課題】1フレーム当たりの読み出し期間が長くなるのを抑制すると共に、残像特性の影響を抑制できる。

【解決手段】画素20は、フォトダイオードとなる半導体層21を短絡させるために、行毎に、制御端子が走査配線52に接続されたTFTスイッチ50を備えている。TFTスイッチ4及びTFTスイッチ50がオフ状態において、センサ部103では、放射線に応じて半導体層21で発生した電荷が下部電極11に蓄積される。TFTスイッチ50をオフ状態のまま、TFTスイッチ4をオン状態にし、センサ部103に蓄積された電荷を読み出す。電荷の読み出し終了後、TFTスイッチ4をオフ状態にし、TFTスイッチ50をオン状態にし、センサ部103を短絡させてセンサ部103に飽和量である電荷量Qを蓄積させる。センサ部103の短絡動作が終了すると、TFTスイッチ50をオフ状態にし、TFTスイッチ4をオン状態にして、センサ部103から電荷を放出させてリセットする。

(もっと読む)

固体撮像素子および駆動方法、並びに電子機器

【課題】撮像画像の高画質化を図る。

【解決手段】CMOSイメージセンサの画素アレイ部には、フォトダイオード61と、フォトダイオード61により生成された電荷を浮遊拡散領域65に転送する転送ゲート64と、浮遊拡散領域65の電荷を排出するリセットトランジスタ66とを少なくとも備える複数の単位画素50が配列されている。また、単位画素50における配線層より下層には、フォトダイオード61の受光部を除く単位画素50の略全ての表面を遮光する遮光膜73が形成される。リセットトランジスタ66による電荷排出時には、遮光膜73に印加される電圧が第1の電圧とされ、転送ゲート64による電荷転送時には、遮光膜73に印加される電圧が前記第1の電圧より高い第2の電圧とされる。本発明は、例えば、CMOSイメージセンサに適用することができる。

(もっと読む)

撮像装置

【課題】 CMOSセンサの画素を複数のグループに分割する分割方法と、分割して読み出した画像の合成方法を制御することで、分割した画像間で歪みの程度が違うことによる画像の劣化を低減する。

【解決手段】 光を受光し画像信号に変換する複数の画素を有するCMOSセンサと、前記CMOSセンサの蓄積及び読み出しを制御する駆動制御手段と、前記CMOSセンサから読み出された画像信号に現像処理を行うカメラ信号処理手段を備え、前記駆動制御手段は前記CMOSセンサから読み出す画素を第1の画素グループと第2の画素グループに分けて、第1の画素グループを読み出した後に第2の画素グループを読み出すことを特徴とする。

(もっと読む)

固体撮像装置

【課題】固体撮像装置においてフォトダイオードの面積のばらつきに伴う不都合を抑制しつつ、2つの画素間でリセットトランジスターを共有化する。

【解決手段】第1の色の光を受光する第1のフォトダイオードと、第1のフォトダイオードの第1の方向の隣に配置された第2の色の光を受光する第2のフォトダイオードと、第2のフォトダイオードの第2の方向の隣に配置された第1の色の光を受光する第3のフォトダイオードと、第3のフォトダイオードの第1の方向の隣に配置された第3の色の光を受光する第4のフォトダイオードと、第1及び第2のフォトダイオードにおいて発生した電荷を排出させる第1のリセットトランジスターと、第3及び第4のフォトダイオードにおいて発生した電荷を排出させる第2のリセットトランジスターと、を具備し、第1のフォトダイオードの面積と第3のフォトダイオードの面積との差が小さい。

(もっと読む)

固体撮像装置

【課題】リニアログ特性を持つ固体撮像装置において、対数特性部のみの感度を制御する。

【解決手段】転送部を直列接続された2段の転送トランジスタTXL,TXHで構成する。転送トランジスタTXHは転送トランジスタTXLよりもオン抵抗が大きい。よって、転送トランジスタTXHを中間電圧VMで駆動させた場合、光電変換素子PDから浮遊拡散層FDに漏れ出る信号電荷は少なくなるため、対数特性部の感度が上がる。一方、転送トランジスタTXLは転送トランジスタTXHよりもオン抵抗が小さい。よって、転送トランジスタTXLを中間電圧VMで駆動させた場合、光電変換素子PDから浮遊拡散層FDに漏れ出る信号電荷は多くなるため、対数特性部の感度が下がる。

(もっと読む)

1 - 20 / 253

[ Back to top ]