Fターム[5C024HX03]の内容

光信号から電気信号への変換 (72,976) | 回路構成 (15,472) | 遅延、移相 (123)

Fターム[5C024HX03]に分類される特許

1 - 20 / 123

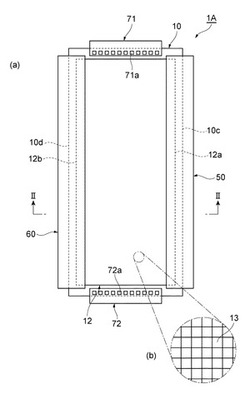

固体撮像装置

【課題】TDI動作によって撮像を行う際に、撮像に要する時間を短くすることができる固体撮像装置を提供する。

【解決手段】固体撮像装置1Aは、M×N個(M,Nは2以上の整数)の画素がM行N列に2次元配列されて成る撮像面12、撮像面12に対して列方向の一端側に各列毎に配置されたN個の信号読出回路20、及び、撮像面に対して列方向の他端側に各列毎に配置されたN個の信号読出回路30を有するCCD型の固体撮像素子10と、信号読出回路20から各列毎に出力される電気信号をディジタル変換したのちシリアル信号として順次出力する半導体素子50と、信号読出回路30から各列毎に出力される電気信号をディジタル変換したのちシリアル信号として順次出力する半導体素子60とを備える。

(もっと読む)

固体撮像装置及び撮像システム

【課題】カウント値の伝搬遅延が異なることに起因する列毎の固定のノイズ成分を低減することができる固体撮像装置を提供することを課題とする。

【解決手段】行列状に配列され、光電変換により信号を生成する複数の画素と、行列状に配列された複数の画素の各列に設けられ、複数の画素の信号を列毎に読み出す複数の読み出し回路と、複数の読み出し回路から出力される信号と時間的にレベルが変化する参照信号とを比較する複数の比較部と、参照信号のレベルが変化を開始してからの時間をカウントするカウンタと、カウンタのカウント値をバッファリングする第1のバッファ(9n)と、カウンタのカウント値をバッファリングする第2のバッファ(9s)と、複数の比較部に接続され、複数の読み出し回路から出力される信号と参照信号との大小関係が逆転したときのカウンタのカウント値を記憶する複数の記憶手段(6)とを有する。

(もっと読む)

AD変換回路および撮像装置

【課題】カウントした計数値の誤差の発生を抑制することができるAD変換回路および撮像装置を提供する。

【解決手段】上位カウンタ101は、遅延回路から出力される第1の下位位相信号を構成する1つの出力信号をカウントクロックとしてカウントを行って第1の上位計数値を取得する。第1の上位計数値を構成する各ビットの値が反転された後、上位カウンタ101は、遅延回路から出力される第2の下位位相信号を構成する1つの出力信号をカウントクロックとしてカウントを行い、さらに下位カウンタ104から出力される上位用カウントクロックに基づいてカウントを行って第2の上位計数値を取得する。変更部103は、上位カウンタ101のカウントクロックの切換えの際に、カウントクロックの論理状態を所定の状態に変更する。

(もっと読む)

撮像装置

【課題】列毎にA/D変換回路を搭載した撮像装置において、基準電圧が変動する場合でも、各列のA/D変換回路から出力されるデジタル値に適切な補正を行うことができる撮像装置を提供する。

【解決手段】入射した光量に応じた画素信号を出力する画素が二次元の行列状に複数配置された画素部と、画素信号に基づいたアナログ信号と基準電源との電位差に応じた遅延時間でパルス信号を伝播させる遅延素子が円環状に複数段接続された遅延回路を具備し、パルス信号が伝播した遅延素子の段数に基づいたデジタル信号を生成するアナログ・デジタル変換回路が、画素部の1列毎または複数列毎に配置されたアナログ・デジタル変換部と、各アナログ・デジタル変換回路から出力されたデジタル信号のそれぞれに対応する重み付け値を設定し、重み付け値と1行分のデジタル信号の平均値とに基づいて画素部の所定の列に対応したデジタル信号を補正する補正部と、を備える。

(もっと読む)

固体撮像装置

【課題】本発明は、画像デジタル信号をアナログ・デジタル変換器からレジスタに転送するときに生じる瞬時電流を低減し、アナログ・デジタル変換器や画素アレイへの回り込み雑音を軽減することができる固体撮像装置を提供する。

【解決手段】本発明は、画素アレイ11と、垂直走査回路14と、複数のコラムADC12と、複数のレジスタ17と、制御信号生成部とを備えている。制御信号生成部は、画素アレイ11の一辺に配置された複数のコラムADC12および複数のレジスタ17を複数に分けたグループごとに設け、変換した画像デジタル信号を、互いに並列に動作するコラムADC12からレジスタ17へ転送するタイミングを、少なくとも一つのグループを含む単位ごとにずらした制御信号を生成する。

(もっと読む)

撮像装置

【課題】冗長にラッチ回路の回路規模を増大させることなく駆動負荷を軽減し、内部の信号情報を確実に転送することができる回路構成を備えた撮像装置を提供する。

【解決手段】入射光量に応じた画素信号を出力する画素が二次元の行列状に複数配置された画素部と、画素部の1列毎または複数列毎に配置され、対応する列の画素の画素信号の大きさに応じたn(nは1以上の自然数)ビットのデジタル信号を出力するm(mは1より大きい自然数)個のデジタル信号出力回路と、デジタル信号出力回路のそれぞれに対応して配置され、対応するデジタル信号出力回路のデジタル信号の各ビットの信号をそれぞれ保持するn個のラッチユニットを具備したm個のラッチ回路と、ラッチユニットのそれぞれに対応して配置され、対応するラッチユニットが保持したデジタル信号を、隣接するラッチ回路内の対応するラッチユニットに転送するm−1個のスイッチと、を備える。

(もっと読む)

AD変換回路および固体撮像装置

【課題】消費電流を低減することができるAD変換回路および固体撮像装置を提供する。

【解決手段】比較部109は、AD変換の対象となるアナログ信号と、時間の経過とともに増加または減少する参照信号とを比較し、参照信号がアナログ信号に対して所定の条件を満たしたタイミングで比較処理を終了する。第1のカウント部18は、所定の周波数のクロック信号をカウントクロックとしてカウントを行い、カウント値を出力する。ラッチ部108は、第1のカウント部18から出力されるカウント値をラッチする。ラッチ制御部105は、比較処理の終了に係る第1のタイミングでラッチ部108を有効にし、第1のタイミングを所定の時間だけ遅延させた第2のタイミングでラッチ部108にラッチを実行させる。

(もっと読む)

固体撮像素子およびその駆動方法、カメラシステム

【課題】レート変換のためにバッファが不要で、低回路規模化、低消費電力化を図ることが可能な固体撮像素子およびその駆動方法、カメラシステムを提供する。

【解決手段】レート変換情報に応じて、カラム処理部で処理されたデータのレート変換制御を行うレート変換制御部を有し、レート変換制御部は、第2の周波数の第2のクロックである基準クロックを基に、第1のクロックを生成してカラム処理部に供給する第1のレート変換器と、第2の周波数の第2のクロックである基準クロックを基に、データレートに応じて変化する第3の周波数の第3のクロックを生成する第2のレート変換器と、カラム処理部で処理されたデータのレートを加算処理を含んだ処理により変換し、変換後または変換前のデータを第2のデータとして出力するデータレート変換部と、第3のクロックに同期してデータレート変換部による第2のデータを出力するデータ出力部と、を含む。

(もっと読む)

クロック生成回路および撮像装置

【課題】シュミットトリガー回路と同様な機能を有し、シュミットトリガー回路と比較して貫通電流を低減する。

【解決手段】インバータ回路INV1は、前段回路の回路閾値よりも低い第1の回路閾値を有し、前段回路から出力された入力クロックが入力され、入力クロックの論理状態および第1の回路閾値に応じた第1の出力信号を出力する。インバータ回路INV2は、前段回路の回路閾値よりも高い第2の回路閾値を有し、前段回路から出力された入力クロックが入力され、入力クロックの論理状態および第2の回路閾値に応じた第2の出力信号を出力する。スイッチ回路SWは、第1の出力信号および第2の出力信号が入力され、第1の出力信号および第2の出力信号の論理状態が、異なる状態から同じ状態に変化したときに、異なる論理状態に対応した第1の電圧および第2の電圧のいずれか一方を出力クロックとして出力する。

(もっと読む)

特異点判定装置

【課題】デジタルサンプリングデータの特異点の判定を行う装置の小型化を実現する。

【解決手段】特異点判定装置10は、入力信号G0を遅延させて出力するFF11と、入力信号G0とFF11からの出力信号G1との差分を出力する減算器12と、減算器12からの出力信号D1と、しきい値b1とを比較する比較回路14と、減算器12からの出力信号D1を遅延させて出力するFF13と、FF13からの出力信号D2と、しきい値b2とを比較する比較回路15と、各比較回路14,15の各々の比較結果に応じて、入力信号G0の特異点の有無を判定するAND回路16とを備える。

(もっと読む)

固体撮像装置

【課題】煩雑な位相合わせが必要なく、高速化や高画素数化が可能な固体撮像装置を提供する。

【解決手段】状態変化検出回路1002は、下位ラッチ回路9によってラッチされたパルス信号のうち、複数の遅延素子のうちの2つの遅延素子から出力されたパルス信号を順に比較し、2つのパルス信号の間で状態が異なるときに状態変化検出信号を出力する。エンコード信号ラッチ回路1003は、状態変化検出回路1002に入力されるパルス信号を出力した遅延素子に応じた状態を有するエンコード信号が入力され、状態変化検出信号が入力された場合にエンコード信号をラッチする。

(もっと読む)

撮像装置

【課題】突発性ノイズを精度よく検出する撮像装置の提供。

【解決手段】複数の撮像画素を備え映像信号を出力する撮像素子と、撮像素子が、第1のタイミングで撮像した第1映像信号、第1のタイミングよりも後の第2のタイミングで撮像した第2映像信号、および、第2のタイミングよりも後の第3のタイミングで撮像した第3映像信号に基づいて、第2映像信号において突発性ノイズが含まれる画素の候補である候補画素を抽出するノイズ画素抽出部と、第2映像信号において、ノイズ画素抽出部が抽出した候補画素の少なくとも1つの画素値を補正する補正部と、を有する撮像装置。

(もっと読む)

フィルタ回路

【課題】連続するノイズ画素がイメージセンサから入力された場合でも、ノイズ除去を行う事が可能なフィルタ回路を提供すること。

【解決手段】撮像素子回路2において、二次元配列されたイメージセンサ4により撮像された画像は、フィルタ回路6に入力される。フィルタ回路6のセレクタ部SL1ないしSL8は、画像を構成する25画素の画素データPDを第1フィルタ部FF1ないしFF8へ割り振る。縦1ラインに連続した状態のインパルス性ノイズの画素は、それぞれグループGR5、GR1、GR8、GR4、GR3に属する。フィルタ処理対象の画素群であるグループGR1ないしGR8中に、インパルス性ノイズが2画素以上含まれないようになる。

(もっと読む)

固体撮像装置

【課題】固体撮像装置を大型化させることなく、A/D変換回路の動作に起因する入力およびGNDの電圧レベルの変動を低減し、出力するデジタル値の変動(誤差)を低減することができる固体撮像装置を提供する。

【解決手段】光電変換素子のリセット信号と画素信号とを出力する画素が二次元の行列状に複数配置された画素部と、所定の1つの画素からのリセット信号および画素信号が順次入力される第1の容量と、画素信号とリセット信号との差を保持する第2の容量とを具備し、差分信号を出力するアナログ信号処理部と、差分信号の大きさに応じた遅延時間でパルス信号を遅延させる遅延素子がリング状に複数段接続された遅延回路と、パルス信号の遅延回路内の伝播を検出した結果に基づいたデジタル信号を生成するアナログ・デジタル変換器と、アナログ信号処理期間とサンプリング期間とで第1の容量の接続を切り替える切り替え回路と、を備える。

(もっと読む)

光電変換装置

【課題】光電変換装置を大型化させることなく、カラムA/D方式の光電変換装置と同等のデジタル値を出力することができる光電変換装置を提供する。

【解決手段】光電変換素子を有し、該光電変換素子への入射光量に応じた画素信号を出力する画素が、二次元のY行X列に複数配置された画素アレイと、画素アレイの列毎に読み出された画素信号の電圧の大きさに応じて周回するパルス信号を計測し、該計測したパルス信号の情報を出力するm(m≦X)個のパルス計測部と、パルス計測回路が計測したパルス信号の情報に基づいて、画素アレイの各列から読み出された画素信号に応じたデジタル値を出力するk(k<m)個のエンコーダ部と、m個のパルス計測部から出力されるパルス信号の情報を順次切り替えて、k個のエンコーダ部に入力させる切り替え部と、を備える。

(もっと読む)

パルス走行位置検出回路、A/D変換回路および固体撮像素子

【課題】高精度でパルス信号の走行位置を検出することができ、狭小な場所にも配置することができるパルス走行位置検出回路、これを用いたA/D変換回路、およびこのA/D変換回路を用いた固体撮像素子を提供する。

【解決手段】印加された電源または該電源に応じた電流源に応じた遅延時間でパルス信号を遅延させる複数の遅延素子を具備した同一の構成の遅延回路が、少なくとも1つのフィードフォワード回路が形成されるように、直列の円環状に複数段連結されたパルス走行回路と、複数の遅延回路のそれぞれから出力される出力信号を検出して保持した情報を走行位置の情報として出力するラッチ回路とを備え、それぞれの遅延回路は、第1の遅延素子と、構造が異なる第2の遅延素子とを具備し、少なくとも1つの遅延回路内にパルス信号の走行を開始させる起動信号を入力し、他の遅延回路内に、少なくともパルス信号が走行している間は所定の固定電圧を入力する。

(もっと読む)

画像処理装置及びその制御方法

【課題】 少ないメモリ容量で縮小RAW画像を生成可能な画像処理装置を提供する。

【解決手段】 各画素が単色輝度情報を有するRAW画像から、まず、水平方向の空間周波数の帯域制限を行い、かつ、水平方向の画素数を削減した水平縮小RAW画像を第1の生成部110で生成する。そして、水平縮小RAW画像をラインメモリ105に格納し、第2生成部120で水平縮小RAW画像に対して少なくとも垂直方向の画素を削減することにより、縮小RAW画像を生成する。

(もっと読む)

画像処理装置及びその制御方法

【課題】スジ状の固定パターンノイズを有する黒画像において、少なくともスジと平行な方向のランダムノイズを簡易な回路構成で適切に低減する。

【解決手段】遮光状態で撮像された黒画像を取得し、当該黒画像のスジと平行な方向のラインのそれぞれについて、巡回型のフィルタを適用することによりスジと平行な方向のランダムノイズを低減する。画像処理装置は、巡回型のフィルタを適用することにより得られた黒画像から、巡回型のフィルタの群遅延量分のスジと直交する方向のラインを削除する。さらに、群遅延量分のラインが削除された画像のスジと直交する方向の最終ラインを用いることにより、群遅延量分のライン数の画像を生成して、群遅延量分のラインが削除された画像に加えて出力する。

(もっと読む)

A/D変換回路及び固体撮像装置

【課題】小型化を実現したA/D変換回路及び固体撮像装置を提供する。

【解決手段】遅延回路42の複数の遅延素子の各々の第1のパルス入力端子は複数の遅延素子の対応する1つのパルス出力端子に接続される。また、複数の遅延素子は、第1のパルス入力端子に入力されたパルス出力信号を、アナログ信号入力端子に入力されたアナログ信号に応じて遅延させてパルス出力端子から出力し、複数の遅延素子のいずれか1つは外部からパルス信号が入力される。状態変化検出回路47は、複数の遅延素子のうちの連続する2つからのパルス出力信号を順に比較し、2つのパルス出力信号の間で状態が異なるときに状態変化検出信号を出力する。エンコード信号ラッチ回路48は、状態変化検出信号が入力された場合に、状態変化検出回路47にパルス出力信号を出力した遅延素子に応じた状態を有するエンコード信号をラッチする。

(もっと読む)

撮像装置

【課題】 製造コストを削減しつつ、撮像装置の動作を高速化する。

【解決手段】 撮像装置は、センサチップおよび信号処理チップを有している。センサチップは、複数の画素が2次元行列状に配置された画素アレイと、画素アレイの画素列毎に画素のアナログ信号を出力する複数のデータ出力端子により構成されるデータ出力端子群とを有している。信号処理チップは、データ出力端子群に電気的に接続されるデータ入力端子群と、データ入力端子群で受けた画素のアナログ信号を画素アレイの画素列毎にデジタル信号へ変換する複数のA/D変換器と、複数のA/D変換器の動作を制御する制御部とを有している。

(もっと読む)

1 - 20 / 123

[ Back to top ]