Fターム[5C024HX37]の内容

光信号から電気信号への変換 (72,976) | 回路構成 (15,472) | 発振回路 (65)

Fターム[5C024HX37]の下位に属するFターム

PLL (20)

Fターム[5C024HX37]に分類される特許

1 - 20 / 45

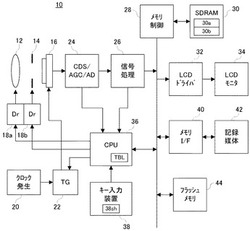

電子カメラ

【構成】基準クロックの周波数は当初、低域の周波数帯域FR1に属する周波数F1に設定される。TG22は、低解像度モードに従う態様でCCDイメージャ16を駆動する処理を初期設定された基準クロックに基づいて実行する。CCDイメージャ16の出力に基づくスルー画像は、LCDモニタ34に表示される。シャッタボタン38shが全押しされると、基準クロックの周波数は高域の周波数帯域FR2に属する周波数F2_1に変更される。TG22は、高解像度モードに従う態様でCCDイメージャ16を駆動する処理を変更後の基準クロックに基づいて実行する。ただし、変更後の基準クロックとの干渉に起因するノイズが検知されると、基準クロックの周波数が周波数帯域FR2において微調整される。その後のCCDイメージャ16の出力は、記録媒体42に記録される。

【効果】記録性能が向上する。

(もっと読む)

電子内視鏡装置

【課題】撮像と表示との同期を確保することができる。

【解決手段】画像処理プロセッサ20は、表示クロックを生成する表示発振回路206と、表示クロックに基づいてモニタ表示同期信号を生成するモニタ同期信号生成部207とを備える。内視鏡スコープ10は、光学情報を電気信号に変換し、シリアル形式のデジタルデータとして出力する画素115,A/D変換器116,P/S変換器117と、画素115を駆動する元となる撮像クロックを生成する撮像発振回路111と、モニタ表示同期信号と撮像クロックとの位相を比較し、撮像発振回路111の発振を制御する位相比較器113とを備える。

(もっと読む)

電子内視鏡装置

【課題】撮像と表示との同期を確保することができる電子内視鏡装置を提供する。

【解決手段】位相制御部111は、表示同期信号110と、撮像クロック生成部106が生成したクロック信号107から生成されたクロック信号113との位相を比較し、比較結果に基づいて撮像クロック生成部106の発振を制御する。駆動信号生成部125は、クロック信号107に同期した逓倍クロック信号120に基づいて、CMOSセンサ122を駆動する駆動信号121を生成する。

(もっと読む)

クロック生成回路および撮像装置

【課題】シュミットトリガー回路と同様な機能を有し、シュミットトリガー回路と比較して貫通電流を低減する。

【解決手段】インバータ回路INV1は、前段回路の回路閾値よりも低い第1の回路閾値を有し、前段回路から出力された入力クロックが入力され、入力クロックの論理状態および第1の回路閾値に応じた第1の出力信号を出力する。インバータ回路INV2は、前段回路の回路閾値よりも高い第2の回路閾値を有し、前段回路から出力された入力クロックが入力され、入力クロックの論理状態および第2の回路閾値に応じた第2の出力信号を出力する。スイッチ回路SWは、第1の出力信号および第2の出力信号が入力され、第1の出力信号および第2の出力信号の論理状態が、異なる状態から同じ状態に変化したときに、異なる論理状態に対応した第1の電圧および第2の電圧のいずれか一方を出力クロックとして出力する。

(もっと読む)

画像形成アレイ用ホストインタフェース

【課題】システムプロセッサがアクセスする画像形成データを直接的に受信することのできる画像形成アレイと共に累積可能なインタフェースを提供する。

【解決手段】画像形成アレイ12を有する画像センサとクロックジェネレータ1Aとからデータを受信し、このデータをプロセッサシステム10へ転送するインタフェース13は、画像形成アレイデータを、該クロック信号により決定された速度で記憶するメモリを備える。このメモリにおけるデータの量に応じて、信号ジェネレータが前記プロセッサシステム10へ伝送するための信号を生成し、また、回路が前記プロセッサシステム10により決定された速度で、前記メモリからのデータの転送を制御する。前記メモリは、先入れ先出し(FIFO)バッファ、または、アドレス可能メモリであり、このインタフェース13は、前記画像センサと同一のダイ上に集積される。

(もっと読む)

固体撮像装置

【課題】回路規模を増大させることなく、かつ、ダイナミックレンジを低下させることなく横筋状ノイズ補正を可能とする固体撮像装置を提供する。

【解決手段】所定の時間間隔で、複数のAD変換部により変換された単位画素のデジタル信号から光学的な黒レベルを示すクランプ値を演算するクランプ演算回路190と、前記クランプ値に基づき、列AD変換部120に、対応する列の単位画素のデジタル信号であってオフセット信号成分を除くデジタル信号に変換させる制御部とを備え、クランプ演算回路190は、前記クランプ値と、1つ前に演算した過去クランプ値との差が予め定められた下限値以下の場合には、所定の時間間隔を長くして前記クランプ値の次のクランプ値を演算し、前記クランプ値と過去クランプ値との差が予め定められた上限値以上の場合には、所定の時間間隔を短くして前記クランプ値の次のクランプ値を演算する。

(もっと読む)

撮像装置および撮像装置の制御プログラム

【課題】最適な駆動周波数で撮像素子を駆動した場合、設定された動画像のフレームレートとの差により、一定のフレーム間隔ごとに、同一フレームを連続させる重複処理などを行わなければならず、画質の劣化を招いていた。

【解決手段】上記課題を解決するために、撮像装置は、被写体像を光電変換してフレーム画像信号を出力する撮像部と、フレーム画像信号が順次書き込まれ、かつ、順次読み出される記憶部と、記憶部におけるフレーム画像信号の読み書き状況を監視する監視部と、監視部が監視する読み書き状況に基づいて、撮像部からフレーム画像信号を出力させるタイミングを規定する垂直同期信号の間隔を変化させる制御部とを備える。

(もっと読む)

撮像装置

【課題】カラム部内で2進化および減算を行うことが可能となり、信号の位相合わせを簡略化することができる撮像装置を提供する。

【解決手段】ラッチ部107は、VCO101から出力される第1の下位位相信号および第2の下位位相信号をラッチする。下位計数部21は、ラッチ部107に保持された第1の下位位相信号、第2の下位位相信号に応じて第1の下位計数信号、第2の下位計数信号を生成し、各下位計数信号に基づく計数値の差に応じて、フラグ信号を含む下位差分信号を生成して出力する。上位計数部22は、VCO101から所定の周期で第1の画素信号に応じて出力される第1の上位計数信号に基づく計数値と、VCO101から所定の周期で第2の画素信号に応じて出力される第2の上位計数信号に基づく計数値との差に応じて、上位差分信号を生成し、フラグ信号に基づいて上位差分信号から所定の数を減算処理し、減算処理後の上位差分信号を出力する。

(もっと読む)

光電変換装置

【課題】光電変換装置を大型化させることなく、カラムA/D方式の光電変換装置と同等のデジタル値を出力することができる光電変換装置を提供する。

【解決手段】光電変換素子を有し、該光電変換素子への入射光量に応じた画素信号を出力する画素が、二次元のY行X列に複数配置された画素アレイと、画素アレイの列毎に読み出された画素信号の電圧の大きさに応じて周回するパルス信号を計測し、該計測したパルス信号の情報を出力するm(m≦X)個のパルス計測部と、パルス計測回路が計測したパルス信号の情報に基づいて、画素アレイの各列から読み出された画素信号に応じたデジタル値を出力するk(k<m)個のエンコーダ部と、m個のパルス計測部から出力されるパルス信号の情報を順次切り替えて、k個のエンコーダ部に入力させる切り替え部と、を備える。

(もっと読む)

撮像装置

【課題】 製造コストを削減しつつ、撮像装置の動作を高速化する。

【解決手段】 撮像装置は、センサチップおよび信号処理チップを有している。センサチップは、複数の画素が2次元行列状に配置された画素アレイと、画素アレイの画素列毎に画素のアナログ信号を出力する複数のデータ出力端子により構成されるデータ出力端子群とを有している。信号処理チップは、データ出力端子群に電気的に接続されるデータ入力端子群と、データ入力端子群で受けた画素のアナログ信号を画素アレイの画素列毎にデジタル信号へ変換する複数のA/D変換器と、複数のA/D変換器の動作を制御する制御部とを有している。

(もっと読む)

光電変換装置および撮像システム

【課題】 従来の技術では、消費電力の増大や画質の低下を抑制しつつ、読み出しの高速化を実現することが困難であった。

【解決手段】 画素アレイの列に対応して設けられた、画素から出力された信号をデジタル信号に変換する複数のA/D変換部を少なくとも含む信号処理部と、2以上の出力端子を有し、出力端子の各々に対応して設けられた複数の出力ブロックを含む出力部と、同期信号を出力する同期信号生成部と、を含み、互いに隣接するまたは1列おきの複数の列の信号処理部をブロックとして、出力ブロックは、前記ブロックに属する複数の信号処理部から出力された信号を出力し、同期信号に同期して、出力ブロックから出力される信号に対して同期コードを付加する同期コード付加部をさらに有する。

(もっと読む)

画像センサ

【課題】状況に応じて取得する画像データのデータ量を変更することのできる画像センサを提供する。

【解決手段】所定の領域を撮像して画像データ5を取得する撮像部1と、撮像部1から得られた画像データ5を構成する各画素の有するデータに基づいて演算する制御部2とを備え、撮像部1は、画像データ5の各画素のデータと、一定の周波数の矩形波から成るピクセルクロック信号とを制御部2に送信し、制御部2は、画像データ5を各画素のデータとピクセルクロック信号とを同期させることで取得し、撮像部1と制御部2との間には、ピクセルクロック信号を分周する分周器3が設けられ、制御部2は、分周器3の分周比を指定する制御信号を分周器3に送信し、分周器3は、制御部2からの制御信号に基づいて分周比を変化させる。

(もっと読む)

固体撮像装置および固体撮像装置の駆動方法

【課題】TADが出力するデジタル信号の線形性を補正するための補正式の算出処理を軽減することができる。

【解決手段】第2の補正計算部210は、A/D変換器20が出力するデジタル信号に基づいて、A/D変換器20が出力するデジタル信号の線形性を補正するための第2の補正式を算出する。判定部220は、第2の補正計算部210が算出した第2の補正式の係数と、この第2の補正式よりも前に算出した第2の補正式の係数とを比較した結果に基づいて、第1の補正式を算出するか否かを判定する。アップデート信号出力部230は、第1の補正式を算出すると判定された場合、第1の補正計算部110に第1の補正式を算出させるための信号を出力する。

(もっと読む)

画像撮像装置

【課題】NTSC方式のフレーム周波数から外したフレーム周波数で撮像素子から画像データを取り込み、フレームメモリにプログレッシブで書込み、インタレースで読み出す撮像装置におけるインタレース特有のコムノイズの発生を防止、また、実装するクロック発振器はNTSC方式対応の発振器のみとして、低コストな撮像装置を提供する。

【解決手段】フレームメモリ105を少なくとも3つの領域に分ける。制御部10は、各領域を書込み領域・読出し領域として、その役割を順次切り替えるようにし、ある領域からの読出し終了時に、次に読出す領域への書込みが完了しているか確認して、読出し領域の切替えを行う。撮像素子101は、NTSC方式対応の発振器107のクロックで動作し、垂直方向のブランキング期間乃至水平方向のブランキング期間を変更することで、NTSC方式のフレーム周波数から外れたフレーム周波数で画像データを出力する。

(もっと読む)

画像撮像装置

【課題】NTSC方式対応の撮像装置において、撮像素子のフレーム周波数をNTSC方式のフレーム周波数から外したフレーム周波数とする際に、そのための特別のクロック発振器を不要とし、また、コムノイズ発生の影響を最小限にする。

【解決手段】NTSC方式対応のクロック信号発生用の発振器107のみ備える。制御部106は、前記発振器からのNTSC方式対応のクロック周波数のクロックを基に、NTSC方式のフレーム周波数でフレームメモリ105からの読出しを制御する。撮像素子102は、前記発振器からの同クロックを入力し、垂直方向のブランキング期間を変更することで、フレーム周波数をNTSC方式のフレーム周波数から外れたフレーム周波数とする。さらに、撮像素子102は、CPUの制御下で、露光時間が一定以下の場合のみ、NTSC方式のフレーム周波数から外れたフレーム周波数とする。

(もっと読む)

固体撮像装置

【課題】切り出し動作の高速化及び低消費電力化を実現するとともに、全画素読み出し動作の制御を容易に行う。

【解決手段】本発明に係る固体撮像装置500は、列毎に1つ設けられ、対応する列に配置された画素から読み出されたアナログの画素信号をデジタル信号に変換する複数のAD変換回路200と、列毎に1つ設けられ、対応する列のAD変換回路200により変換されたデジタル信号を保持する複数のディレイ・フリップ・フロップ202と、バイパス信号線601と、最終段のディレイ・フリップ・フロップ202以外の1つのディレイ・フリップ・フロップ202に保持されるデジタル信号をバイパス信号線601に出力するバッファ600と、最終段のディレイ・フリップ・フロップ202により保持されるデジタル信号と、バイパス信号線601のデジタル信号とのうち一方を出力する出力セレクタ603とを備える。

(もっと読む)

電子内視鏡

【課題】電子内視鏡装置において、アナログ伝送路の距離を短くして、映像信号の劣化を抑制する。

【解決手段】内視鏡挿入部の先端部11Aに撮像素子23を設ける。内視鏡操作部に、中継部26を設ける。中継部26に、初段増幅回路、相関二重サンプリング回路、ADコンバータを備えたアナログフロントエンド28を設ける。撮像素子23からのアナログ映像信号をアナログフロントエンド28で受信してデジタル映像信号に変換する。デジタル映像信号をシリアライザ29においてシリアル化し、ユニバーサルコード内に配設された差分伝送または光伝送を用いた映像信号伝送経路30を通して中継部26からコネクタ部13へと伝送する。

(もっと読む)

撮像装置

【課題】LVDS等の高速インターフェースを備えた撮像装置において、動作モードが突然変更された場合であっても撮像信号に正しく同期した信号処理を行うことが可能な撮像装置を提供すること。

【解決手段】並び替え部105において並び替えがなされた撮像データは書き込み制御部1073の制御により、撮像データに同期したクロックCLK1−1に同期したタイミングで記憶部1072に書き込まれる。並び替え部105から出力されるチャンネル当たりの撮像データのデータ量に応じた周波数となるようにマスク処理部106においてクロックCLK3に対するマスク処理がなされてクロックCLK2が生成される。記憶部1072に書き込まれた撮像データは読み出し制御部1074の制御により、クロックCLK2に同期したタイミングで読み出され、信号処理部1075において処理される。

(もっと読む)

固体撮像装置

【課題】電源/グランドの電位変動による回路ノイズを低減することができる。

【解決手段】撮像部2は、入射される電磁波の大きさに応じた画素信号を出力する画素3が複数、行列状に配されている。電圧補正部8は、画素信号をサンプルホールドするためのスイッチ素子と容量素子とを有する。RDL101は、第1の電源端子と第2の電源端子に供給される信号の電位差に応じて遅延時間が変化する反転回路が複数段連結され、画素信号が第1の電源端子に供給されると共に、反転回路の1つに対して、クロックの生成を開始させる起動信号と所定の段の反転回路からの出力信号とが入力され、画素信号の大きさに応じた周波数のクロックを生成する。カウンタ103は、クロックのカウント処理を行う。また、スイッチ素子に接続された容量素子の第1の端子と第1の電源端子との間にバッファ回路を有し、第2の電源端子に容量素子の第2の端子が接続されている。

(もっと読む)

バイナリ値変換回路およびその方法、AD変換装置、固体撮像素子、並びにカメラシステム

【課題】イメージセンサに集積しやすいよう小型で低消費電力であり、クロック位相情報をバイナリ値に変換し、かつデジタル加減算可能なバイナリ値変換回路およびその方法、AD変換装置、固体撮像素子、並びにカメラシステムを提供する。

【解決手段】状態に応じてレベルが反転する信号のレベルが反転した際に、少なくとも一つのクロック信号の位相情報をラッチするラッチ回路12と、ラッチ回路のラッチ位相情報を、パルス信号に応じてパルス列に変換する少なくとも一つの変換回路13と、変換回路の変換により得られたパルスをカウントクロックとして用いて、クロックの位相情報をバイナリコードに変換するリップルカウンタ部14と、を有する。

(もっと読む)

1 - 20 / 45

[ Back to top ]