Fターム[5C024HX52]の内容

光信号から電気信号への変換 (72,976) | 回路構成 (15,472) | 論理回路 (142) | AND回路、OR回路 (26)

Fターム[5C024HX52]に分類される特許

1 - 20 / 26

固体撮像装置

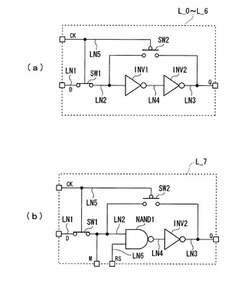

【課題】消費電流を低減することができる固体撮像装置を提供する。

【解決手段】画素信号のレベルに応じた論理状態の信号を出力する複数の遅延ユニットのいずれかの出力信号の論理状態をラッチするラッチ回路L_7において、複数の遅延ユニットのいずれかの出力信号が入力端子Dに入力される。NAND回路NAND1およびINV回路INV2は、画素信号のレベルに応じた制御信号が出力される制御信号出力タイミングまでは停止しており、制御信号出力タイミングの後に動作する。スイッチ回路SW1,SW2は、制御信号出力タイミングまでは複数の遅延ユニットのいずれかの出力信号を、信号線LN2を介して出力端子Mから出力し、制御信号出力タイミングから所定時間が経過した後のラッチタイミングで複数の遅延ユニットのいずれかの出力信号の論理状態をNAND回路NAND1およびINV回路INV2がラッチするように接続の切替を行う。

(もっと読む)

撮像装置および撮像表示システム

【課題】撮像画像の高画質化を実現することが可能な撮像装置、およびそのような撮像装置を備えた撮像表示システムを提供する。

【解決手段】撮像装置は、各々が光電変換素子と電界効果型のトランジスタとを含む複数の画素を有する撮像部と、トランジスタのオン動作およびオフ動作を切り替えて画素内に蓄積された信号電荷の読み出し駆動およびリセット駆動を行う駆動部とを備える。トランジスタは半導体層を間にして第1および第2のゲート電極を有し、駆動部は、トランジスタの第1のゲート電極に第1の電圧、第2のゲート電極に第2の電圧をそれぞれ印加し、かつリセット駆動の際には、第1および第2の電圧のそれぞれにおいて、オン電圧およびオフ電圧間の切り替え時期およびオン電圧値のうちの一方または両方が互いに異なるようにする。リセット駆動時に生じるチャージインジェクションを低減することができる。

(もっと読む)

固体撮像装置及びその駆動方法

【課題】簡易な回路構成でオーバーフロー処理を実現することができる固体撮像装置を提供することを課題とする。

【解決手段】2次元状に配列された複数の画素と、ランプ信号を生成する参照信号生成回路と、ランプ信号の出力に合わせてカウント動作を行うカウンター回路と、列毎に配置され画素から読み出された信号とランプ信号を比較する比較部と、列毎に配置されデジタルデータを記憶する記憶部とを有し、AD変換期間中に比較部の出力が反転しない場合には、所定の値のデジタルデータが記憶部に記憶されるようにし、簡易な回路構成でオーバーフロー処理を実現できるようにする。

(もっと読む)

固体撮像装置

【課題】本発明は、画像デジタル信号をアナログ・デジタル変換器からレジスタに転送するときに生じる瞬時電流を低減し、アナログ・デジタル変換器や画素アレイへの回り込み雑音を軽減することができる固体撮像装置を提供する。

【解決手段】本発明は、画素アレイ11と、垂直走査回路14と、複数のコラムADC12と、複数のレジスタ17と、制御信号生成部とを備えている。制御信号生成部は、画素アレイ11の一辺に配置された複数のコラムADC12および複数のレジスタ17を複数に分けたグループごとに設け、変換した画像デジタル信号を、互いに並列に動作するコラムADC12からレジスタ17へ転送するタイミングを、少なくとも一つのグループを含む単位ごとにずらした制御信号を生成する。

(もっと読む)

固体撮像装置

【課題】撮像領域に対する1水平走査期間内で電子シャッタ状態および読み出し状態を設定する垂直選択回路において、電子シャッタ動作用と読み出し動作用とで回路を共有化する。

【解決手段】画素アレイ部11は、光電変換した電荷を蓄積する画素12がマトリックス状に配置され、垂直信号線VLIN1〜VLINMは、画素12から読み出された画素信号を垂直方向に伝送し、垂直選択回路17は、画素アレイ部11の各選択行に対して電子シャッタ状態および読み出し状態を時分割多重で設定し、パルスセレクタ回路18は、選択行に属する画素12を電子シャッタ状態および前記読み出し状態に応じて駆動し、タイミングジェネレータ回路19は、垂直選択回路17およびパルスセレクタ回路18の動作タイミングを制御する。

(もっと読む)

電源回路、集積回路装置、固体撮像装置および電子機器

【課題】電源回路において、ソフトスタート回路による電源回路の回路規模を抑制する。

【解決手段】電源回路1の比較部11は、参照電圧と入力電圧とを比較して電圧差信号を出力し、出力電圧生成部12は、電圧差信号に基づいて出力電圧を生成し、入力電圧生成部14は、出力電圧から入力電圧を生成する。抵抗素子16は、電流出力部15の参照電流により参照電圧を生成する。キャパシタ17は、抵抗素子16と並列に接続され、参照電流により充電される。このような電源回路1において、電流出力部15は、起動する際の参照電流を、動作中の参照電流より小さくする。

(もっと読む)

信号処理方法及び固体撮像装置

【課題】AD変換に伴うノイズを低減すると共に、AD変換時間の短縮を可能とする信号処理方法及び固体撮像装置を提供する。

【解決手段】画素の黒レベルのアナログ信号を読み出す第1AD変換期間に、前記黒レベルのアナログ信号をM回繰り返し読み出して、分周切替回路68が、M回繰り返し読み出された前記黒レベルのアナログ信号に応じた各パルス列のパルス数を1/Mに分周し、カウンタ回路70が、1/Mに分周された各パルス列のパルス数をカウントする。その後、前記画素の信号レベルのアナログ信号を読み出す第2AD変換期間に、前記信号レベルの前記アナログ信号を、N回繰り返し読み出して、分周切替回路68が、N回繰り返し読み出された前記信号レベルのアナログ信号に応じた各パルス列のパルス数を1/Nに分周し、カウンタ回路70が、1/Nに分周された各パルス列のパルス数をカウントする。前記M及び前記Nは、N≦Mの関係を満たす。

(もっと読む)

固体撮像装置

【課題】画素アレイの列毎に配置されるサンプルホールド信号変換回路の幾つかが故障した場合に、それを救済できる構成を備えた固体撮像装置を提供すること。

【解決手段】画素アレイの列毎に配置され、画素からの画素信号を伝搬する複数の垂直信号線と、前記複数の垂直信号線それぞれから画素信号を受け取る、該複数の垂直信号線よりも数が多い複数のサンプルホールド信号変換回路と、1本の前記垂直信号線が前記複数のサンプルホールド信号変換回路の2以上に接続されるように、前記複数の垂直信号線と前記複数のサンプルホールド信号変換回路とを接続する複数のスイッチ回路と、1本の前記垂直信号線が1つの前記サンプルホールド信号変換回路に接続されるように前記複数のスイッチ回路を個別に切り替える制御回路とを備えた。

(もっと読む)

撮像素子およびカメラ

【課題】デジタル回路で用いられる高速なクロック信号で動作する回路によって、各画素から読み出される微弱な画像信号にノイズが混入し、画像信号のSN比が劣化するという問題を解決する。

【解決手段】光を電気信号に変換する画素部と、画素部のダーク信号を読み出して保持するダーク信号保持部Ctdと、画素部の画像信号を読み出して保持する画像信号保持部Ctsと、基準信号を発生する基準信号発生部105と、ダーク信号と基準信号とを比較するダーク信号比較部106と、画像信号と基準信号とを比較する画像信号比較部107と、ダーク信号比較部の出力と画像信号比較部の出力との排他的論理和を演算する排他的論理和演算部108とを設けた。

(もっと読む)

固体撮像装置

【課題】静止画撮影時に露光ムラを生じることなく高速な初期リセット動作を行うことができ、高速メカニカルシャッタ動作に対応できるようにした固体撮像装置を提供する。

【解決手段】光信号を信号電荷に変換し蓄積するフォトダイオード101と、フォトダイオードの蓄積信号電荷を増幅し画素信号として出力する増幅トランジスタ104と、蓄積電荷を増幅トランジスタに転送する転送トランジスタ102と、信号電荷をリセットするリセットトランジスタ103とを備えた画素100を2次元状に配列した画素部と、画素部を行毎に駆動制御するための垂直走査信号を出力する垂直走査回路202と、垂直走査信号に基づいて転送トランジスタを駆動する行転送信号を生成すると共に、行転送信号に対して立ち下がりを所定量遅延させたリセットトランジスタを駆動する行リセット信号を生成する垂直選択部203とで固体撮像装置を構成する。

(もっと読む)

固体撮像装置及びその処理方法

【課題】フレームレートを低下させずに広いダイナミックレンジを得ることができる固体撮像装置及びその処理方法を提供することを課題とする。

【解決手段】光電変換により電荷を生成する光電変換素子と、前記生成された電荷の信号を読み出す読み出し手段と、前記生成された電荷量が基準値より少ないときの信号と基準値より多いときの信号とが相互に逆極性になるように前記読み出された信号に極性を付与する極性付与手段とを有することを特徴とする固体撮像装置が提供される。

(もっと読む)

固体撮像装置及び撮像装置

【課題】間引き読み出し駆動時に、走査回路内に配置されたレベルシフタ回路に一斉に電流が流れることを回避でき、誤動作などを防止する。

【解決手段】画素アレイ部2の各画素をレベルシフタ回路33を介して駆動制御して画素信号の読み出しを行う画素駆動制御回路部において、画素アレイ部2の行単位または列単位で選択し、画素信号の読み出しを行う間引き読み出し制御を行う場合に、この間引き読み出し制御によって選択されない非読出し画素行または非読出し画素列をリセットする。この場合、画素駆動制御回路部からレベルシフタ回路を介さずに駆動制御させるOR回路等を設けることにより、間引き読み出し駆動時にレベルシフタ回路に一斉に電流が流れることを回避し、レベルシフタ回路を起因で起こる大電流を抑制する。

(もっと読む)

撮像装置

【課題】遮光領域の信号レベルが異常に変動した場合、特に遮光領域に輝度の高い被写体が撮像されても安定した撮像信号を得る。

【解決手段】高輝度被写体の画像cが遮光領域aにある場合、撮像素子201の出力Soutは、遮光領域aであっても高いレベルd2を出力し、検出判定回路705における検出回路801は検出タイミングパルスJ1に同期して撮像素子の出力レベルを検出するが、このときの検出結果は通常より高いレベルとなる。判定回路802はクランプ回路202のクランプレベル更新を禁止すべくクランプ許可パルスCPENBを Low レベルにし、クランプタイミングパルスCPOB1はANDゲート706で制限( Low レベルに)され、クランプ回路にはクランプパルスが供給されず、クランプ回路はクランプレベル(黒基準)を更新せず、それ以前のクランプレベル、例えばd1を基準にクランプ動作を続ける。

(もっと読む)

巡回型アナログ・ディジタル変換器およびイメージセンサデバイス

【課題】3値のディジタル値を用いることない回路構成を可能にする巡回型アナログ・ディジタル変換器が提供される。

【解決手段】巡回型A/D変換器11は、M+1ビットのディジタル値を生成するためにN回(N>M+1)の巡回動作を行う。ゲインステージ13の利得が2未満の所定値であるので、変換結果が、A/D変換おいて許容される最大値または最小値を超えることはなく、比較回路15におけるオフセット誤差を小さくするための負担が軽減される。補正回路19は、比較回路15からのN個のディジタル値を受けると共に、利得Gに関連づけられた補正係数を用いて比較回路15からのN個のディジタル値を補正して、M+1ビットのディジタル値を生成する。2未満の利得のゲインステージ13を用いることによる変換誤差は、追加のディジタル値(N−M−1)を生成すると共に、補正係数を用いてA/D変換値(Nビット)を補正することにより除去できる。

(もっと読む)

垂直CCDドライバ及びそれを備えた撮像装置

【課題】垂直CCDにおける高速駆動モードと小信号電荷量時の完全転送との両立を実現する垂直CCDドライバを提供する。

【解決手段】垂直CCDドライバは、3値の電圧レベルを出力するため、3種類のトランジスタを用いて構成される。VH電圧レベルを決定するp型トランジスタ10はVH電源と出力ノードとに接続されており、ゲートHに信号電圧が印加される。VM電圧レベルを決定するn型トランジスタ11aはVH電源と出力ノードとに接続されており、ゲートHに信号電圧が印加される。同様に、VL電圧レベルを決定するn型トランジスタ11b、11cはそれぞれVL電源と出力ノードとに接続されており、ゲートL1、L2に独立して信号電圧が印加される。

(もっと読む)

タイミングパルス発生装置及びそれを用いたCCD撮像装置、CMOS撮像装置、LCD表示装置、撮像素子セット。

【課題】駆動パルスの変化点の数の変動に対応でき、かつ、メモリの使用効率を高めることが可能なタイミングパルス発生装置及びそれを用いた撮像装置を提供することを目的とする。

【解決手段】メモリ2中に単位パルスパターン長を規定するLENデータと、単位パルスの繰り返し数を規定するループデータと、単位パルスパターンを繰り返させるRETURNデータと駆動パルスのレベルを表す駆動パルスデータを格納する。アドレス発生回路1に応じた各データをメモリ2は出力し、その出力結果に応じて駆動パルスが形成され、タイミングパルスが生成される。

(もっと読む)

撮像装置および集積回路

【課題】画面の一部のみが動きの早い被写体であっても画面全体の蓄積時間を短くするため、動きのない部分についてはSN比が劣化する。

【解決手段】基準時間のN倍の速度で動作する撮像部1と、撮像部1の出力を記憶する記憶部2と、これらのN枚の画像データを用いて静止画部分と動画部分を識別する識別部3と、動画領域についてはN枚中1枚を選択して出力する動画部処理部5と、静止画領域については加算平均処理等の高SN化処理を施した後、出力する動画部処理部5と、動画部処理部5の出力と静止画部処理部4の出力を合成する合成部6と、合成部6の出力を基準時間に変更する時間伸長部7を備えている。

(もっと読む)

固体撮像装置

【課題】信号出力の高速化を実現することが可能な2次元の固体撮像装置を提供する。

【解決手段】列選択信号列6a−1…、6b−1…を相異なる位相で並行して出力する水平走査回路6a、6bと、列選択信号列6a−1…に同期する相異なる並列制御信号を伝送する並列制御信号線5a、5b、列選択信号列6b−1…に同期する相異なる並列制御信号を伝送する並列制御信号線5c、5d、列選択信号6a−1と同期する並列制御信号のそれぞれとの論理積を細分化列選択信号5a−1、5b−1として出力する論理積回路51、52、列選択信号6b−1と同期する並列制御信号のそれぞれとの論理積を細分化列選択信号5c−1、5d−1として出力する論理積回路53、54、各細分化列選択信号に応じて、隣接2列の画素回路に蓄積されている各電荷を複数の水平信号線を介して並行して読み出す水平読み出し回路4を備える。

(もっと読む)

撮像素子の同期回路

【課題】画素ずれの発生しない撮像素子の同期回路を提供することを目的とする。

【解決手段】クロック7を分周して分周クロック9を発生する分周器8と、水平同期信号6と垂直同期信号16を生成する信号処理回路4と、前記分周クロック9と前記水平同期信号6と前記垂直同期信号16から撮像素子駆動信号18を生成するタイミング・ジェネレータ2と、を有する撮像素子3の同期回路であって、前記タイミング・ジェネレータ2はゲート信号12を生成し、前記クロック7と前記分周クロック9と前記水平同期信号6と前記ゲート信号12から補正クロック15を生成し前記信号処理回路4に供給するクロック補正回路を備えたことを特徴とする。

(もっと読む)

3値パルス発生回路

【課題】スイッチング素子の貫通電流を抑制し、消費電力を低減させた3値パルス発生回路を実現する。

【解決手段】3つの論理素子14a,14b,14cを含む論理回路部10と、3つの論理素子14a,14b,14cの各々の出力によって制御される3つのスイッチング素子22,24,26を含むスイッチング制御部20とを備え、3つのスイッチング素子22,24,26が同時にオン状態とならないように制御することによって互いに異なる3つの電圧値Vhigh,Vmid,Vlowを切り替えて出力する3値パルス発生回路100によって上記課題を解決することができる。

(もっと読む)

1 - 20 / 26

[ Back to top ]