Fターム[5C082EA15]の内容

表示装置の制御、回路 (141,802) | 被応用技術、関連技術、その他の観点 (914) | メモリアクセス競合対策技術 (223) | 非同期制御によるもの(例;CPU優先) (26)

Fターム[5C082EA15]に分類される特許

1 - 20 / 26

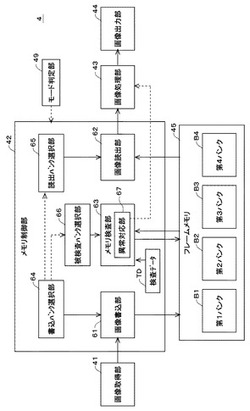

画像処理装置、画像表示システム及び画像処理方法

【課題】バンクの競合を回避しながらメモリを検査する。

【解決手段】画像表示システムでは、表示装置の表示モードに、撮影画像を表示するバックモニタモードと、撮影画像以外の非撮影画像であるナビ画像を表示するナビゲーションモードとがある。画像書込部61は、バックモニタモードとナビゲーションモードとの双方において書込バンクに撮影画像を周期的に書き込む。また、画像読出部62は、バックモニタモードのみにおいて、書込バンクとは異なる読出バンクから撮影画像を周期的に読み出す。一方、メモリ検査部63は、ナビゲーションモードのみにおいて、書込バンクとは異なる被検査バンクを検査する。したがって、メモリ検査部63は、読出バンクを考慮せずに被検査バンクを選択できるため、バンクの競合を回避しながらフレームメモリ45を検査することができる。

(もっと読む)

データ処理装置

【課題】画像メモリのアクセス量の低減や、LCDコントローラでの消費電力の低減を図る。

【解決手段】LCDコントローラ(23)と、CPU(25)と、退避エリア(WT)とを含んでデータ処理装置(2)を構成する。上記LCDコントローラは、上記画像メモリから読み出された複数の画像データをブレンド処理可能な処理部(233)を含む。上記LCDコントローラは、上記処理部でのブレンド処理の対象とされる画像データの変更の有無、及び上記処理部でのブレンド処理におけるブレンド位置の変更の有無を判別し、その判別結果に応じて、上記処理部の動作を停止させるとともに、上記退避エリアに退避されている画像データを上記LCDパネルに表示させることにより、画像メモリのアクセス量の低減や、LCDコントローラでの消費電力の低減を図る。

(もっと読む)

画像処理装置

【課題】 ティアリングの発生を防止するとともに、コマ落ちからの復帰時に最新のフレーム画像を表示する。

【解決手段】

3以上のフレームバッファ22a〜22cからなる画像記憶部22と、フレーム画像を画像記憶部22へ周期的に書き込む画像書込部212と、画像記憶部22からフレーム画像を周期的に読み出す画像読出部232と、最後に書き込みが終了したフレームバッファを示す前回書込先情報WS1及び読出中のフレームバッファを示す読出先情報RSを保持するアクセス先記憶部24と、前回書込先情報WS1に基づいて、次の読出先となるフレームバッファを選択し、読出先情報RSを更新する読出先選択部231と、前回書込先情報WS1及び読出先情RS報に基づいて、次の書込先となるフレームバッファを選択する書込先選択部211とを備える。

(もっと読む)

描画装置及び描画方法

【課題】 インタレーススキャンを行う場合、少ない記憶容量の描画のためのバッファを用い、品質の高い三次元イメージの表示を可能とする描画装置を提供する。

【解決手段】 奇数フィールド表示のため、第二番目の奇数ラインに初めて表示されるポリゴン#2の最小Y座標とその1つ前の偶数ラインに初めて表示されるポリゴン#1の最小Y座標とが同一であるとみなして、デプス値の大きい順に、ポリゴン構造体インスタンス#2、次にポリゴン構造体インスタンス#1と並べられる。偶数フィールド表示のため、一番上の偶数ラインに初めて表示されるポリゴン#1の最小Y座標とその1つ前の奇数ラインに初めて表示されるポリゴン#0の最小Y座標とが同一であるとみなして、デプス値の大きい順に、ポリゴン構造体インスタンス#1、次にポリゴン構造体インスタンス#0と並べられる。

(もっと読む)

画像表示装置およびプログラム並びに画像表示制御方法

【課題】画像の表示をより適切に行なう。

【解決手段】VRAMからの1画素分のデータの読み出しタイミングがVRAMへの1画素分のデータの書き込みタイミングよりも速いLCDコントローラーにおいて、通常時は読み出しタイミング(クロック信号DCLK)にデフォルト値Ddefを設定し(S320)、書き込み用のアドレスカウンターAc1と読み込み用のアドレスカウンターAc2との差分(Ac1−Ac2)が所定値Aref以下となったときに読み出しタイミングを書き込みタイミングと同一の設定値Dlowに設定する(S330)。これにより、データの読み出しが書き込みを追い越す追い越し現象が生じるのを回避でき、液晶ディスプレイへの画像の表示をより適切に行なうことができる。

(もっと読む)

画像表示装置

【課題】ラインバッファーからVRAMの画像データの書き込みを効率よく行なう。

【解決手段】ラインバッファー32を1ライン分の画像データの左半分(左画像)と右半分(右画像)とを各々保持する2つのラインバッファーBL0,BL1により構成し、各々にVRAMのデータの読み出しと競合しないよう書き込み禁止期間を設けて各々を独立して動作させる。BL0からVRAMに左画像が書き込まれる前にBL1から同一ラインの右画像を書き込む場合には右画像の先頭画素を無圧縮とし2番目以降の画素を左隣の画素の画像データとの差分に基づいて圧縮し、BL0からVRAMに左画像が書き込まれた後にBL1から右画像を書き込む場合には右画像の先頭画素を既にVRAMに書き込み済みの右画像の最終画素の画像データとの差分に基づいて圧縮し2番目以降の画素を左隣の画素の画像データとの差分に基づいて圧縮する。

(もっと読む)

遊技台

【課題】描画制御手段を待つ期間を短縮することにより、フレーム落ちの発生頻度を低減させ、遊技者により違和感を与えない画像表示を行なうことができる遊技台を提供する。

【解決手段】本発明に係る遊技台は、画像情報に基づいて表示情報を生成する表示情報生成手段と、表示情報に基づいて描画情報を生成する描画制御手段と、描画情報に基づいて、所定の画像を表示する画像表示装置と、を備え、表示情報は、一次情報と、一次情報から生成される二次情報と、を含み、表示情報生成手段は、画像情報から一次情報を生成する一次情報生成手段と、一次情報から二次情報を生成する二次情報生成手段と、を含み、描画制御手段は、描画情報を生成可能な状態になった場合に、二次情報生成手段による二次情報の生成が開始された後であれば、二次情報に基づいて描画情報を生成し、二次情報の生成を開始する前であれば、一次情報に基づいて描画情報を生成する。

(もっと読む)

画像処理装置

【課題】画像の切り出しを画像の入力と並行して行う処理において、入力画像に含まれる切出領域の位置やサイズに依存することなく、表示画像の適切な表示を可能にする。

【解決手段】領域切出回路32aは、時系列的に順次入力される入力画像Dinから、表示装置の表示画像を規定する切出領域を切り出す。クロック生成回路35aは、入力ドットクロックDCKinを切出領域のサイズに応じて分周することにより、出力ドットクロックDCKaを生成する。画像出力回路34aは、切出領域内の画素データを出力ドットクロックDCKaに基づいて表示装置に順次出力する。同期信号生成回路36aは、入力画像のスキャン開始点を基準とした切出領域の水平/垂直方向のオフセット量と、切出領域のサイズとに応じた水平/垂直同期信号HSa,VSaを生成して表示装置に出力する。

(もっと読む)

LCDコントローラ

【課題】LCDコントローラにおいて、あるピクセルに関して、表示情報と非表示情報の両方の情報を格納するために、使用するメモリ容量を削減する。

【解決手段】任意のピクセルに関して色情報と非表示情報を制御するCPUと、CPUのメインメモリであり且つVRAMを兼ねるUMAであるメモリを用い、LCDに描画を行うLCDコントローラの構成であって、メモリからピクセルデータを読み出すメモリ読み出し部と、CPUから非表示情報のビット数を通知されることによってマスク処理を行うマスクビット数が可変であるマスク部と、LCDを制御する制御信号生成部と、からなる。

(もっと読む)

電気光学表示デバイスの制御方法、電気光学表示デバイスの制御装置

【課題】画像ソースと双安定電気光学ディスプレイ装置間のインターフェイスを簡略化す

る新規な方法を提供すること。

【解決手段】画像のピクセルと前の画像のピクセルとから合成されたピクセルデータを生

成し、設定可能な少なくとも1つの条件が真であるか決定するために前記画像のピクセル

と前記前の画像の対応するピクセルとを比較するとともに、前記少なくとも1つの条件が

真である場合に2つ以上の更新モードから1つの更新モードを選択し、パイプラインに前

記画像の各ピクセルに対し波形を決定させて前記波形を画像データとして表示装置に伝送

させる。

(もっと読む)

画面表示制御装置

【課題】画像データの部分的な書換えを効率よく行うことのできる技術を提供する。

【解決手段】VRAM766から読み出されて伸長部により復元されたベース画像IMGの画像データのうち部分画像pIMGに相当する部分が部分書込データにデータ置換制御手段により置換された後、圧縮部により圧縮されてVRAM766に格納される。そして、一部が部分書込データに置換された圧縮データがVRAM766から読出されて伸長部により復元されることにより、ベース画像IMGの一部が部分画像pIMGに置換された画像が表示部22に表示される。したがって、VRAM766内の圧縮データを復元して得たベース画像IMGの画像データを利用することで、部分画像pIMGの部分書込データのみで画像データを部分的に書換えることができるため、非常に効率よくベース画像IMGの一部を部分画像pIMGに置換できる。

(もっと読む)

表示データ処理装置、画像表示装置、表示データ処理方法、およびプログラム

【課題】例えばデータバスのトラフィックがあがった場合など、プロセッサ外部の外部メモリからのデータ読み込みが間に合わなくなる虞がある状況であっても、表示データ処理を確実にできるようにし、表示性能を確保することができるようにする。

【解決手段】プロセッサ内部の制御手段は、プロセッサ外部の外部メモリからの表示データ読み込みの遅延時間が予め定められた閾値を越えると、その外部メモリ内の表示データの少なくとも一部をプロセッサ内部の内部メモリに転送する。

(もっと読む)

半導体集積回路

【課題】表示系アクセスの要求に係る信号のアクティブ期間が通常期間に比べて変動するような場合でも、所定の表示系アクセスの期間を確保できる半導体集積回路の提供。

【解決手段】CPU系制御回路24は、LCDパネル30に対する読出し要求に基づくデータの読み出しが行われていない場合に、CPU10からの書込み要求又は読出し要求に基づくデータの書込み又は読出しが行われるように書込み/読出し回路を制御する。表示系制御回路26Aは、LCDパネル30に対する表示データの読出し要求に係る読出し要求信号が有効であって表示データの読出し動作を行う場合には、表示データの読出し動作は、読出し要求信号の有効期間の開始時に開始され、読出し要求信号の有効期間の長さに無関係に所定時間の経過後に終了されるように、読出し回路を制御する。

(もっと読む)

映像信号処理装置

【課題】映像信号処理装置においてメモリへのアクセスをより適切に処理する。

【解決手段】映像信号を処理するためのCPU20と、映像信号を表示する際に重畳されるオンスクリーン画像データを処理するOSD処理部22と、CPU20及びOSD処理部22からアクセスされるSRAM28と、CPU20とOSD処理部22とのアドレスバス及びデータバスを排他的に切り替えてSRAM28にアクセス可能に接続するアクセス制御部24と、を備える。アクセス制御部24は、CPU20及びOSD処理部22からSRAM28へのアクセスが同時に要求されたときには、OSD処理部22から出力される占有要求信号が出力されていればOSD処理部22をSRAM28にアクセス可能に接続し、占有要求信号が出力されていないときにはCPU20をSRAM28にアクセス可能に接続する。

(もっと読む)

半導体集積回路

【課題】表示系アクセスの開始直後にCPU系アクセスの要求がある場合などに、表示系アクセスの期間を確保できる半導体集積回路の提供。

【解決手段】CPU系制御回路24は、LCDパネル30に対する読出し要求に基づくデータの読み出しが行われていない場合に、CPU10からの書込み要求又は読出し要求に基づくデータの書込み又は読出しが行われるように書込み/読出し回路を制御する。表示系制御回路26Aは、LCDパネル30に対して表示データの読出し中であって、表示データの所定の読出し期間を経過する前に、CPU10からの書込み要求又は読出し要求がある場合には、所定の読出し期間を経過するまで表示データの読出し動作を継続するように、読出し回路を制御する。

(もっと読む)

電気機器およびその制御方法

【課題】 できるだけ安価なCPUを使用しながら表示の乱れを防ぐことができる電気機器およびその制御方法を提供する。

【解決手段】 RISC CPU1のVGA機能による表示用データをそのRISC CPU1からデータバス20によりSDRAM21に供給して一旦格納し、そのSDRAM21内の表示用データをデータバス20を介してRISC CPU1に取込み、取込んだ表示用データをRISC CPU1から液晶表示器12に供給して表示する。

(もっと読む)

半導体集積回路

【課題】表示系アクセスからCPU系アクセスに移行する場合に、CPU系アクセスのデータ読出しの誤動作を防止し、データ書込み時の速度を上げてサイクルタイムの短縮。

【解決手段】CPU系制御回路24Aは、LCDパネル30に対する読出し要求に基づくデータの読み出しが行われていない場合であって、CPU10からの書込み要求又は読出し要求に基づくデータの書込み又は読出しを行う場合に、データの書込みの開始タイミングとデータの読出しの開始タイミングとが別個になるように書込み/読出し回路を制御する。表示系制御回路26は、CPU11からの書込み要求又は読出し要求に基づくデータの書込み又は読出しが行われていない場合であって、LCDパネル30に対する読出し要求がある場合に、LCDパネル30に対してデータの読出しが行われるように読出し回路を制御する。

(もっと読む)

多色表示装置

【課題】表示パネルの大画面化、多階調化が求められている。また、N色(N>3)の表示パネルを利用する要求がある。これを実現するには、画面メモリが大容量化する問題がある。また、信号変換の対象とするデータ量が増加するので、信号変換の回路構成が複雑となる。

【解決手段】画像データを固定圧縮率の圧縮データ形式で画面メモリ103に蓄積して、圧縮した画像データの信号変換を行うことで、メモリ容量の削減と、信号変換回路の簡易化を実現する。この信号変換の効果として、表示の色再現特性の向上と、輪郭形状の平滑化による画質向上を得る。また、表示パネル105がN色のサブピクセルで構成する場合において、圧縮データ形式を利用して、サブピクセル単位の信号変換を行うことで、画質向上を実現する。

(もっと読む)

表示装置および表示プログラム

【課題】ティアリングの発生を抑えながら画面の更新速度の低下を軽減する。

【解決手段】表示装置は、表示部(LCDモジュール11)の更新領域が所定量(ティアリング発生確率に基づく)を超えた場合に表示制御部(LCDコントローラ13)により生成される垂直同期信号に同期して記憶部の表示情報を更新し、所定量未満の場合に垂直同期信号に非同期に記憶部の表示情報を更新する制御部14を有する。

(もっと読む)

映像信号出力装置及び方法

【課題】送信側から受信側に非同期で映像データを伝送する場合でも、送信側と受信側で同期のとれた映像を表示することのできる「映像信号出力装置及び方法」を提供する。

【解決手段】第1のクロックに同期して映像データを送信する送信装置から、通信手段を介して当該映像データを受信し、記憶手段に蓄積し、第2のクロックに同期して当該映像データを前記記憶手段から取り出して表示手段に映像を表示する映像信号出力装置は、1垂直同期区間における基準の映像データ量と、第2のクロックを使用するときの1垂直同期区間における映像データ量とから映像データ補正量を検出し、当該映像データ補正量に応じて所定の水平走査期間を調整する同期調整手段を有する。同期調整手段は、映像表示に寄与しない複数の無効水平走査期間に映像データ補正量を分配して、当該複数の無効水平走査期間を調整するようにしても良い。

(もっと読む)

1 - 20 / 26

[ Back to top ]