Fターム[5E034DB01]の内容

サーミスタ、バリスタ (5,260) | 構造(PTC、NTC、バリスタ) (356) | 素子自体の構造 (33)

Fターム[5E034DB01]に分類される特許

1 - 20 / 33

積層セラミック電子部品

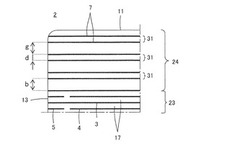

【課題】内部電極の露出部にめっき膜を析出させるにあたって、より確実なめっき成長を実現するため、いずれの内部電極も存在しない外層部にダミー導体を形成したとき、積層セラミック電子部品の信頼性、たとえばBDVが低下することがあった。

【解決手段】高さ方向に沿って2枚以上の外層ダミー導体7を所定間隔で連続的に配置することにより、複数の外層ダミー群31を形成する。外層ダミー群31内における外層ダミー導体7同士の間隔をd、外層ダミー群31同士の間隔をg、としたとき、gがdより大きくなるようにする。これによって、めっき析出ポイントを確保しつつ、外層ダミー群31同士の間隔を遠ざけることにより、外層ダミー導体7による内部電極3,4の押圧を緩和することができ、局所的に内部電極間距離が短くなることを防止でき、BDVの低下を防止できる。

(もっと読む)

発光ダイオード、レーザーダイオード、フォトデテクタに適した電気的抵抗素子

本発明は電気的な抵抗素子に関している。この抵抗素子は、半導体材料によって形成された基体(2)と、この基体(2)と導電的に接続されている第1のコンタクト素子(5)と第2のコンタクト素子(6)とを有している。さらに前記基体(2)は第1の主要面(2a)を有しており、該第1の主要面(2a)内には凹部(3)が設けられており、前記第1のコンタクト素子(5)は前記凹部(3)内で少なくとも部分的に前記基体(2)と導電的に接続されており、前記基体(2)は、第2の主要面(2b)を有しており、該第2の主要面(2b)は前記第1の主要面(2a)と対向的に設けられており、前記第2のコンタクト要素(6)は第2の主要面(2b)に少なくとも部分的に前記基体(2)と導電的に接続されている。  (もっと読む)

(もっと読む)

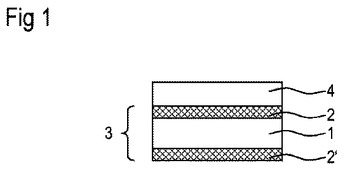

バラクタ、およびバラクタを製造する方法

バラクタは、次の各構成要素を含んでおり、すなわち、抵抗に関して正の温度係数を有する第1のPTC領域(4)と、コンデンサ領域(3)とを含んでおり、該コンデンサ領域は、第1の電極(2)と、第2の電極(2’)と、第1の電極(2)と第2の電極(2’)との間に配置された第1の誘電性層(1)とを含んでおり、

第1のPTC層(4)とコンデンサ領域(3)は熱伝導式に相互に結合されており、コンデンサ領域(3)のキャパシタンスは、第1のPTC領域(4)、コンデンサ領域(3)、または第1のPTC領域(4)およびコンデンサ領域(3)へのバイアス電圧の印加によって変更可能である。  (もっと読む)

(もっと読む)

表面実装型過電流保護素子

本発明は、第一PTC素子材12、第一PTC素子材12の両表面に貼り付けた第一金属箔層11および第二金属箔層13からなる単層PTC複合チップ10と、第二PTC素子材16、第二PTC素子材16に貼り付けた第三金属箔層15および第四金属箔層17からなる単層PTC複合チップ10’と、を備える表面実装型過電流保護素子において、二つの単層PTC複合チップ10、10’の間の第三絶縁層14により、第二金属箔層13と第三金属箔層15を電気的に隔離かつ粘着結合させ、二層PTC複層チップ20を構成し、二層PTC複合チップ20の中心部より端部に偏る位置であって、第一金属箔層11と第四金属箔層17の上下対称位置に、それぞれエッチング図形18、19を形成することにより、内側の第一PTC素子材12と第二PTC素子材16を露出させ、単位複合チップ30を構成し、単位複合チップ30の穴開けと実装により、PTC特性を有する表面実装型過電流保護素子を構成することを特徴とする表面実装型過電流保護素子、を提供する。 (もっと読む)

LED実装用基板

【課題】小型化された照明用のLED回路を実現するためのLED実装用基板を提供する。

【解決手段】LED実装用基板10は、それぞれLED1のアノード及びカソードが接続されるアノード電極11及びカソード電極12からなるLED実装用電極対と、アノード電極11に接続される第1の端子電極21と、カソード電極12に接続される第2の端子電極22と、第3の端子電極23と、LED1と並列に接続され、LED1の発光電圧より高いトリガ電圧を有するバイパス素子31が形成されたバイパス層30と、第1の端子電極21と第3の端子電極23との間に接続され、上記トリガ電圧より高いバリスタ電圧を有し、バイパス素子31より応答速度の速い第1のバリスタ素子41が形成されたバリスタ層40とを備える。

(もっと読む)

電流−電圧非直線抵抗体およびその製造方法

【課題】非直線抵抗特性に優れた電流−電圧非直線抵抗体およびその製造方法を提供する。

【解決手段】電流−電圧非直線抵抗体10は、酸化亜鉛を主成分とし、副成分として少なくともビスマス(Bi)、アンチモン(Sb)を含んだ混合物の焼結体20を備える。また、電流−電圧非直線抵抗体10における焼結体20は、焼結体20の所定の断面における、焼結体20の微細構造を主に構成する各酸化亜鉛粒子21の断面において、断面に亘って最長となる最長直線の長さ(L)と、この最長直線の中点で直交し、断面に亘る直交直線の長さ(S)との比(S/L)を平均した値が0.66以上となるように構成されている。

(もっと読む)

薄膜抵抗温度センサ

【課題】基板に応力が加わって薄膜パターンが変形しても、温度検出精度への影響が少ない薄膜抵抗温度センサを提供する。

【解決手段】長方形状の基板2に、抵抗体を往復形状に接合した薄膜パターン3を形成する。薄膜パターン3は、往路部4と、往路部4に平行な復路部5と、これら往路部4と復路部5とを互い違いに接続する折り返し部6とから構成され、これら往路部4および復路部5の基板2短手方向に対する傾斜角度は、基板2の材料のポアソン比に基づいて決定される。

(もっと読む)

温度センサ

【課題】広範囲な温度域にわたる温度計測と、特定の温度域における温度の高精度計測とを、従来より好適に両立できる温度センサを提供すること。

【解決手段】第1のサーミスタ素子54と第2のサーミスタ素子56とを、電気的に並列に接続した温度センサ1において、第1のサーミスタ素子54のB定数は1000〜2000Kで、第2のサーミスタ素子56のB定数は4000〜8000Kであり、且つ、第1のサーミスタ素子54のB定数と第2のサーミスタ素子56のB定数とが3.0倍以上異なる特性を有する。更に、所定温度より低温側にて、第1のサーミスタ素子54の抵抗値が第2のサーミスタ素子56の抵抗値より低く、且つ、所定温度より高温側にて、第1のサーミスタ素子54の抵抗値が第2のサーミスタ素子56の抵抗値より高い特性を有する。

(もっと読む)

リニアサーミスタ

【課題】 リニアサーミスタにおいて、熱結合端子が高電圧回路に接合されていても高電圧回路と温度検出回路との高い絶縁性を確保すること。

【解決手段】 サーミスタ素子部1と該サーミスタ素子部1に接続された第1の抵抗2及び第2の抵抗3とが設けられた複合サーミスタチップ11と、該複合サーミスタチップ11に電気的に接続されたグランド端子GND、電源端子VCC、出力端子OUT、複合サーミスタチップ11に電気的に絶縁されている熱結合端子5を有したリードフレーム6と、複合サーミスタチップ11を封止した直方体形状の樹脂封止部7と、を備え、樹脂封止部7の一つの側面に、グランド端子GNDと電源端子VCCと出力端子OUTとが配されていると共に、この側面の反対側の側面に熱結合端子5が配されている。

(もっと読む)

静電気対策素子

【課題】静電容量が小さく、且つ、放電特性に優れるのみならず、耐熱性及び耐候性が高められた、静電気対策素子等を提供すること。

【解決手段】絶縁性基板11上において相互に離間して対向配置された電極21,22の間に、絶縁性無機材料32のマトリックス中に導電性無機材料33が不連続に分散したコンポジットである機能層31を配設する。

(もっと読む)

サーミスタ素子及びその製造方法

【課題】 サーミスタ素子及びその製造方法において、電極線とサーミスタとの接触面積を増やし、高い接合強度によってヒートサイクルによる素子の破壊を防ぎ、製法においては、厚さ調整が容易で抵抗値ばらつきを抑えること。

【解決手段】 サーミスタ材料であるセラミックス粉体のチップ状の成型体が焼成され形成された金属酸化物焼結体4と、該金属酸化物焼結体4の両側面に接続された少なくとも一対の電極線5と、を備え、金属酸化物焼結体4の両側面に溝部2aが形成され、電極線5が、溝部2aに嵌め込まれた状態で接続されている。

(もっと読む)

複合電子部品

【課題】静電容量が小さく且つ放電特性に優れた静電気対策素子とコモンモードフィルタとを組み合わせて構成された小型で高性能な複合電子部品を提供する。

【解決手段】複合電子部品100は、第1及び第2の磁性基体11a、11bに挟まれたコモンモードフィルタ層12a及び静電気対策素子層12bによって構成されている。コモンモードフィルタ層12aは互いに磁気結合されたスパイラル導体17,18を備えている。静電気対策素子層12bは、下地絶縁層27の表面に形成されたギャップ電極28,29と、ギャップ電極を覆う静電気吸収層30とを備えている。ギャップ電極28,29のギャップはインダクタンス素子の導体パターンと重ならない位置に配置されている。静電気吸収層30は低電圧放電タイプの静電気保護材料として機能し、静電気などの過電圧が印加された際に、この静電気吸収層30を介して電極間で初期放電が確保される。

(もっと読む)

PTC素子およびその製造方法

【課題】抵抗値のバラツキが少ないPTC素子を提供すること。

【解決手段】第1および第2電極板10および12で覆われていない素子本体4の外周面に、幅が0.02mm以上で深さが0.05mm以上の凹部4aを、少なくとも一つ以上形成してあるポリマーPTC素子。

(もっと読む)

積層型チップバリスタ

【課題】クラックの発生及び、内部電極とスルーホール導体の接続不良を抑制することができる積層型チップバリスタを提供する。

【解決手段】内部電極21を、スルーホール導体27との接続部28において、スルーホール10の貫通方向に湾曲するように構成する。これにより、接続部28の湾曲面28aとスルーホール導体27との間に挟まれる領域Tを接続部28付近のバリスタ層9に形成する。この領域Tでは、バリスタ層9に対して内部電極21とスルーホール導体27の金属が拡散することによって金属濃度が高くなるため、焼成終了時において、内部電極41及びスルーホール導体47の収縮率と、バリスタ層9の他の領域の収縮率の中間の収縮率を有することとなる。これにより、内部電極41とスルーホール導体47とバリスタ層9が密集してクラックが発生し易い接続部28付近で、領域Tにより応力緩和する。

(もっと読む)

積層チップバリスタおよびその製造方法

【課題】素体の表面を保護しつつ、端子電極の形成部位以外の部位へのめっき金属の析出を抑制可能な積層チップバリスタおよびその製造方法を提供する。

【解決手段】本実施形態に係る積層チップバリスタ1は、半導体を主組成とした素体2と、素体2上に形成された端子電極8と、少なくとも端子電極8の形成部位以外の素体2の表層に形成された、アルカリ金属を含有する高抵抗層5と、高抵抗層5上に形成されたガラス層6と、を有する。

(もっと読む)

電子機器

【課題】実装面積を縮小することが可能な電子機器を提供することを目的とする。

【解決手段】積層型チップバリスタV1は、バリスタ素体1と、第1及び第2の外部電極7,8とを備える。第2の外部電極7,8は、バリスタ素体1の他方の主面3に形成される。バリスタ素体1は、バリスタ特性を発現するバリスタ層と、第1及び第2の内部電極とが積層された積層体として構成される。第1の内部電極は、スルーホール導体を通して第1及び第2の外部電極7に電気的に接続される。第2の内部電極は、スルーホール導体を通して第1及び第2の外部電極8に電気的に接続される。半導体発光素子51が、積層型チップバリスタV1における第2の外部電極7,8に対向するように複数の第2の外部電極7,8上に配され、積層型チップバリスタV1に並列接続されるように第2の外部電極7,8に接続されている。

(もっと読む)

薄膜サーミスタ及び薄膜サーミスタの製造方法

【課題】 高温環境下での抵抗値変化を抑制しながら電極の接合不良をなくすことができ、品質及び信頼性が向上すること。

【解決手段】 表面にSiO2層2が形成されたシリコン基板3と、SiO2層2の上面にパターン形成されたサーミスタ薄膜4と、貴金属以外の金属材料で形成され、SiO2層2の上面にパターン形成された接合層5と、該接合層5上にパターン形成された貴金属からなる電極6と、を備え、サーミスタ薄膜4の内部に、サーミスタ薄膜4が形成されない薄膜非形成領域4aを有し、接合層5及び電極6が、薄膜非形成領域4a内に埋め込み形成され側面がサーミスタ薄膜4の内側面に接合され、薄膜非形成領域4a内の接合層5及び電極6の一部が、除去されて抵抗値調整されている。

(もっと読む)

薄膜サーミスタ及び薄膜サーミスタの製造方法

【課題】 高温環境下での抵抗値変化を抑制しながら電極の接合不良をなくすことができ、品質及び信頼性が向上すること。

【解決手段】 表面にSiO2層2が形成されたシリコン基板3と、SiO2層2の上面にパターン形成されたサーミスタ薄膜4と、貴金属以外の金属材料で形成され、SiO2層2の上面にパターン形成された接合層5と、該接合層5上にパターン形成された貴金属からなる電極6と、を備え、サーミスタ薄膜4の内部に、サーミスタ薄膜4が形成されない薄膜非形成領域4aを有し、接合層5及び電極6が、薄膜非形成領域4a内に埋め込み形成され側面がサーミスタ薄膜4の内側面に接合されている。

(もっと読む)

多層素子及び多層素子を製造する方法

多層素子は、少なくとも1つの第1内部電極1及び少なくとも1つの第2内部電極2が配置された本体5を有する。これらの内部電極1、2は、少なくとも1つの側面において、本体5の表面まで広がる重複領域12を有する。さらに、内部電極1、2は本体の角領域5に凹部7を有する。 (もっと読む)

集合基板の製造方法及び集合基板

【課題】量産に適した集合基板の製造方法及び集合基板を提供すること。

【解決手段】集合基板の製造方法は、第1グリーン体形成工程、第2グリーン体形成工程、挿入工程、及び焼成工程を備える。第1グリーン体形成工程では、互いに対向する一対の主面を有すると共に一対の主面の対向方向に伸びる複数の貫通孔が設けられた基板状の第1のグリーン体を形成する。第1グリーン体形成工程では、チップ状の複数の第2のグリーン体を形成する。挿入工程では、第1のグリーン体に設けられた複数の貫通孔に複数の第2のグリーン体をそれぞれ挿入する。焼成工程では、複数の第2のグリーン体が複数の貫通孔にそれぞれ挿入された第1のグリーン体を焼成し、集合基板40を製造する。

(もっと読む)

1 - 20 / 33

[ Back to top ]