Fターム[5E034DC03]の内容

サーミスタ、バリスタ (5,260) | 電極端子(PTC、NTC、バリスタ) (667) | 電極形成法 (47)

Fターム[5E034DC03]に分類される特許

1 - 20 / 47

電気PTCサーミスタ部品とその製造方法

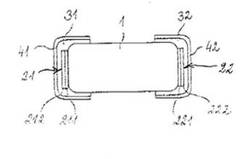

【課題】特性許容誤差を低くするPTCサーミスタ部品とその製造方法を提供する。

【解決手段】ベース本体1と、それぞれ前記ベース本体1の端面上に配置された第1の導電層と第2の導電層とを有する。第1の導電層は空乏層を破壊するバリア層21、22である。ベースの周面は第1の導電層がなく、第2の導電層はベースの各端面上に配置されたキャップ31、32を形成する。さらに、前記第1の導電層は、部品領域の分割前に基板の主要面上にスパッタを通じて生成される。キャップの形状をした第2の導電層は、分割された部品領域の端面上に、浸漬過程で生成される。

(もっと読む)

チップ部品およびその製造方法

【課題】大型でも、高性能で高品質で、実装状態で高い信頼性を確保することのできるチップ部品を提供する。

【解決手段】誘電体素子11と、該誘電体素子の内部に設けた内部電極11aと、該内部電極と電気的に接続した外部電極層15とを備え、誘電体素子11と外部電極層15の間に誘電体素子11の全面を覆うガラス層12を有し、外部電極層15は、金属成分を含む下地電極13と、樹脂電極14とからなり、樹脂電極14は、下地電極13を覆い、かつ誘電体素子11にガラス層12を介して接合する。ガラス層12は、結晶化ガラスからなることが好ましい。

(もっと読む)

チップ型電子部品の製造方法

【課題】素子本体とメディアとを分離する作業が不要であり、素子本体の端面に形成してある下地電極層の表面にメッキ膜を確実に形成することが可能であり、しかも素子本体の表面にダメージを与えるおそれが少ないチップ型電子部品の製造方法を提供すること。

【解決手段】内部電極4,6が内部に形成された素子本体10と、内部電極4,6が露出する素子本体10の端面を覆う端子電極12,14とを有するチップ型電子部品2を製造する方法である。素子本体10の端面に下地電極層12p,14pを形成する。下地電極層12p,14pがそれぞれ形成された複数の素子本体10を、凹状容器20aの内部に収容する。凹状容器20aの内部に液体を入れた状態で、凹状容器20aを第1回転速度で回転させ、素子本体10を、凹状容器の底面20aで内側壁面近くに移動させる。凹状容器20aを第1回転速度よりも高速な第2回転速度で回転させ、素子本体10を内側壁面23aに沿って上方に移動させる。凹状容器20aの回転を停止させる。

(もっと読む)

薄膜バリスタ及びその製造方法

【課題】サージ耐量の向上を図ることにより特性劣化や破壊を防止することが可能な薄膜バリスタ及びその製造方法を提供する。

【解決手段】薄膜バリスタ1は、ニッケル層10と、酸化ニッケル層12と、酸化亜鉛層14と、電極層16,18とを備える。ニッケル層10は、主としてニッケルによって構成されている。酸化ニッケル層12は、ニッケル層10に由来するニッケルが酸化した酸化ニッケルによって構成されており、ニッケル層10と隣接してニッケル層10上に配置されている。酸化亜鉛層14は、酸化ニッケル層12と隣接して酸化ニッケル層12上に配置されている。電極層16は、酸化亜鉛層14と隣接して酸化亜鉛層14上に配置されている。電極層18は、ニッケル層10の表面のうち酸化ニッケル層12によって覆われていない部分を覆うように、ニッケル層10と隣接してニッケル層10上に配置されている。

(もっと読む)

半導体磁器組成物の製造方法及び半導体磁器組成物を用いたヒータ

【課題】BaTiO3−(Bi1/2Na1/2)TiO3系材料のジャンプ特性を向上させる。

【解決手段】BaTiO3のBaの一部をBi-Naで置換した半導体磁器組成物の製造方法であって、(BaQ)TiO3仮焼粉(Qは半導体化元素)を用意する工程、(BiNa)TiO3仮焼粉を用意する工程、前記(BaQ)TiO3仮焼粉及び前記(BiNa)TiO3仮焼粉を混合する工程、混合した仮焼粉を成形し焼結する工程、得られた焼結体を600℃以下で熱処理する工程、前記工程で作製した素子を用いたPTCヒータを含む。

(もっと読む)

静電気対策部品

【課題】本発明は、引出電極を構成する第1の電極の発熱および損傷を低減させることができ、かつ第2の電極のギャップ幅を狭くかつ精度良く形成でき、これにより、静電気の繰り返し印加に対して耐性があり、かつ静電気対策部品にかかるピーク電圧が低く静電気放電(ESD)の抑制特性が安定している静電気対策部品を提供することを目的とするものである。

【解決手段】本発明の静電気対策部品は、絶縁基板1の上面に設けられた一対の第1の電極2を比抵抗が小さい材料を用いて膜厚の厚い状態に構成し、かつ前記一対の第1の電極2間に位置して第2の電極3を設け、さらにこの第2の電極3を高融点金属からなる薄膜を積層した積層膜で構成するとともに、この第2の電極3にギャップ4を形成したものである。

(もっと読む)

多層素子の製造方法

酸化パラジウムを含む内部電極2が付されたグリーンホイル積層体が焼結される、多層素子1の製造方法が記載される。焼結された積層体は、さらなる加熱段階で焼結積層体へと焼成される、外部電極3のための銀ペーストを2面以上に付されて提供される。 (もっと読む)

積層バリスタとその製造方法

【課題】例えば車載用の電子デバイスなどの厳しい使用環境に耐えられる、信頼性の高い積層バリスタとその製造方法を提供することを目的とする。

【解決手段】バリスタ層12と内部電極13を交互に積層した積層体を焼結した焼結体11と、この焼結体11の少なくとも両端面に、前記内部電極13が交互に接続された一対の外部電極とを備え、前記一対の外部電極はガラス量の異なる2層よりなり、前記2層よりなる外部電極のうち、内部電極に接続される内側の第1の外部電極14のガラス含有量が5重量%以下(0を含む)であり、かつ前記第1の外部電極14の上で外側に形成される第2の外部電極15のガラス含有量を10重量%〜30重量%とすることにより外部からの水分浸入を防止し、信頼性の高い積層バリスタを得ることができる。

(もっと読む)

薄膜サーミスタ及び薄膜サーミスタの製造方法

【課題】 高温環境下での抵抗値変化を抑制しながら電極の接合不良をなくすことができ、品質及び信頼性が向上すること。

【解決手段】 表面にSiO2層2が形成されたシリコン基板3と、SiO2層2の上面にパターン形成されたサーミスタ薄膜4と、貴金属以外の金属材料で形成され、SiO2層2の上面にパターン形成された接合層5と、該接合層5上にパターン形成された貴金属からなる電極6と、を備え、サーミスタ薄膜4の内部に、サーミスタ薄膜4が形成されない薄膜非形成領域4aを有し、接合層5及び電極6が、薄膜非形成領域4a内に埋め込み形成され側面がサーミスタ薄膜4の内側面に接合され、薄膜非形成領域4a内の接合層5及び電極6の一部が、除去されて抵抗値調整されている。

(もっと読む)

薄膜サーミスタ及び薄膜サーミスタの製造方法

【課題】 高温環境下での抵抗値変化を抑制しながら電極の接合不良をなくすことができ、品質及び信頼性が向上すること。

【解決手段】 表面にSiO2層2が形成されたシリコン基板3と、SiO2層2の上面にパターン形成されたサーミスタ薄膜4と、貴金属以外の金属材料で形成され、SiO2層2の上面にパターン形成された接合層5と、該接合層5上にパターン形成された貴金属からなる電極6と、を備え、サーミスタ薄膜4の内部に、サーミスタ薄膜4が形成されない薄膜非形成領域4aを有し、接合層5及び電極6が、薄膜非形成領域4a内に埋め込み形成され側面がサーミスタ薄膜4の内側面に接合されている。

(もっと読む)

PTC素子および電池保護システム

【課題】電極板と端子板とを溶接等によって接合する際に、素子本体が熱劣化することを防止できると共に、クラッド板を用いることなく、電極板と端子板とを容易に接続でき、素子本来の機能を有効に発揮することができるPTC素子を提供すること。

【解決手段】所定の温度領域において温度上昇に伴い抵抗値が増加する素子本体4と、前記素子本体4の表裏面に接合された一対の第1電極板10および第2電極板12と、を有するPTC素子2であって、前記第1電極板10における外部に露出する表面の少なくとも一部に、アルミニウムを含む第1端子接合膜14が形成してある。

(もっと読む)

電気PTCサーミスタ部品とその製造方法

開示された電気PTCサーミスタ部品は、ベース1と、それぞれ前記ベース本体1の端面上に配置された第1の導電層と第2の導電層とを有する。前記ベース1の周面は第1の導電層がなく、第2の導電層は前記ベース1の各端面上に配置されたキャップ31、32を形成する。さらに、前記PTCサーミスタ部品の製造方法が明示される。前記第1の導電層21、22は、部品領域の分割前に基板10の主要面上にスパッタを通じて生成される。キャップの形状をした第2の導電層は、浸漬過程で分割された部品領域の端面上に生成される。 (もっと読む)

導電性ペースト及びセラミック電子部品

【課題】セラミック素体に対する接触抵抗の増大を招き難い、単板型のセラミック素体を用いた外部電極形成用導電性ペーストを提供する。

【解決手段】内部電極を有しない単板型のセラミック素体1と、セラミック素体1の表面に形成される外部電極2,3とを備えるセラミック電子部品の外部電極2,3を形成するのに用いられる導電性ペーストであって、導電性成分と、ガラスフリットと、有機ビヒクルとを含有しており、ガラスフリットの塩基度が0.39以上であり、Pb成分を含有しない、導電性ペースト。

(もっと読む)

バリスタ素体及びバリスタ

【課題】 めっき伸びやめっき付着が少ないバリスタを確実に得ることのできるバリスタ素体を提供すること。

【解決手段】 好適なバリスタ素体2は、内部電極層12及びバリスタ層14が交互に積層された構成を有する。バリスタ層14は、主成分としてZnOを含み、副成分としてCo、Pr及びZrを含む組成を有している。そして、バリスタ素体2を、その表面から深さ方向に分析したときにZrの含有量が略一定となる深さ位置を基準深さ位置としたとき、基準深さ位置におけるZrの含有量Z0、基準深さ位置よりも2μm表面側の深さ位置におけるZrの含有量Z1、基準深さ位置におけるPrの含有量P0、及び、基準深さ位置よりも2μm表面側の深さ位置におけるPrの含有量P1が、下記式(1)及び(2)を満たしている。

0.4×Z1/Z0+0.5≦P1/P0≦0.4×Z1/Z0+0.9 …(1)

1<Z1/Z0<2.2 …(2)

(もっと読む)

温度センサ素子、温度センサ、半導体装置および表示装置

【課題】良好な特性を有する温度センサ素子及び温度センサを提供することを課題とする。また、作製工程や作製時間を増加させることなく、低コストで作製できる温度センサ素子及び温度センサを提供することを課題とする。

【解決手段】一対の電極間に有機化合物を含む層を挟む構造であることを特徴とする。具体的には、第1の電極と、第2の電極と、前記第1の電極と前記第2の電極との間に設けられた有機化合物と金属酸化物とを含む混合層と、を有する構造とする。

(もっと読む)

チップ形正特性サーミスタ

【課題】チップ形正特性サーミスタの対向電極間距離を均一とし、磁器内の電界分布の乱れを抑えるとともに、電極の短絡を防止できる電極構造を提供する。

【解決手段】チタン酸バリウム系半導体からなるチップ形正特性サーミスタにおいて、

該チップ形正特性サーミスタの素子の電極が対向する2面にあり、該電極を3層で形成し、第1層としてオーミック接触するニッケル電極を対向端面の全面に形成し、該対向端面を除く側面にセラミックス系、ガラス系、または樹脂系の絶縁材料を用いて絶縁層を形成し、第2層として上記ニッケル表面を被覆する銀電極を、第3層として上記銀表面を被覆するはんだ電極を形成したことを特徴とする。

(もっと読む)

サーミスタの製造方法

【課題】耐電圧を向上できるサーミスタの製造方法を提供する。

【解決手段】このサーミスタの製造方法では、まず、樹脂及び導電性粒子を含むサーミスタ素体シート1aの一方の面4及び他方の面5の少なくとも一方に切り込み6を形成する。次に、切り込み6が形成されたサーミスタ素体シート1aを、一対の電極2及び電極3を用いて挟んで熱圧着する。

(もっと読む)

バリスタ及びバリスタの製造方法

【課題】ZnOを主成分とするバリスタ素体と外部電極との接合強度を向上させることが可能なバリスタ及びバリスタの製造方法を提供すること。

【解決手段】積層型チップバリスタ1は、バリスタ素体3と、該バリスタ素体3に形成された一対の外部電極5とを備えている。バリスタ素体3は、バリスタ部7と、該バリスタ部7を挟むように配置される一対の外層部9とを有している。バリスタ部7及び一対の外層部9は、ZnOを主成分とすると共に希土類元素及びCaを含んでいる。一対の外部電極5は、バリスタ素体3の外表面に焼き付けにより形成されており、Ptを含んでいる。

(もっと読む)

バリスタ素子

【課題】BGAパッケージとされた場合でも、適切且つ容易に実装することが可能なバリスタ素子を提供すること。

【解決手段】積層型チップバリスタ1は、バリスタ素体11、複数の内部電極対、接続導体41及び複数の端子電極51を備える。バリスタ素体11、互いに対向する第1及び第2の主面13,15を有する。各内部電極対は、少なくともその一部同士が互いに対向するようにバリスタ素体11内に配された第1及び第2の内部電極23,33を有する。接続導体41は、複数の内部電極対のうちの所定の内部電極対の第1の内部電極23同士を電気的に接続するように第1の主面13に形成されている。端子電極51は、複数の内部電極対の各第2の内部電極33に対応して設けられ、該第2の内部電極33に電気的に接続されるように第2の主面15に形成されている。

(もっと読む)

チップ形正特性サーミスタ

【課題】チップ形正特性サーミスタの対向電極間距離を均一とし、磁器内の電界分布の乱れを抑えるとともに、電極の短絡を防止できる電極構造を提供する。

【解決手段】チップ形正特性サーミスタ素子の電極が対向する2面にあり、該電極を3層で形成し、第1層としてオーミック接触するニッケル層を対向端面に形成し、第2層として上記ニッケル層表面を被覆する銀層を、第3層として上記銀層表面を被覆するはんだ層を形成し、かつ、対向する電極間にセラミックス系、ガラス系、または樹脂系の絶縁材料を用いて絶縁層を形成し、サーミスタ素子を被覆したことを特徴とする。

(もっと読む)

1 - 20 / 47

[ Back to top ]