Fターム[5F003AP02]の内容

バイポーラトランジスタ (11,930) | 目的 (494) | 短絡防止 (14)

Fターム[5F003AP02]に分類される特許

1 - 14 / 14

ヘテロ接合バイポーラトランジスタの製造方法、及びヘテロ接合バイポーラトランジスタを用いた電力増幅器

【課題】InGaPをエミッタ層として有し、熱的安定性と通電に対する信頼性を両立することの出来るHBTを用いた電力増幅器を提供する。

【解決手段】InGaPエミッタ層を有するHBTにおいて、InGaPエミッタ層5とAlGaAsバラスト抵抗層7の間にGaAs層6を挿入し、ベース層4から逆注入された正孔がAlGaAsバラスト抵抗層7まで拡散、到達することを抑制する。

(もっと読む)

半導体装置および半導体集積回路装置

【課題】半導体集積回路装置の高集積化及び低コスト化を可能にする複数のトランジスタセルを含む半導体装置を提供することを第1の目的とし、高密度に集積化された小型の半導体集積回路装置を安価に提供する。

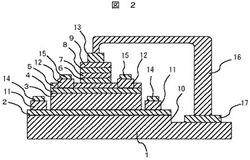

【解決手段】基板上に、それぞれ第1層、ベース層、及び、第2層を順に有し、前記第1層、及び、前記第2層の一方がコレクタ層であり、他方がエミッタ層であるトランジスタセルを複数含み、前記各トランジスタセルの前記第1層に接続される第1電極が、前記第1層に形成されたエッチング溝に形成された半導体装置において、前記エッチング溝は、その長手方向に沿った側面が順メサ面となっており、複数のトランジスタセル間の前記第1電極が、前記各順メサ面に交差するように設けられた、まとめ配線によって接続される半導体装置である。

(もっと読む)

ヘテロ接合バイポーラトランジスタおよびその製造方法

【課題】良好なコンタクト特性を有するベース電極を再現性良く実現できるヘテロ接合バイポーラトランジスタとその製造方法を提供することにある。

【解決手段】

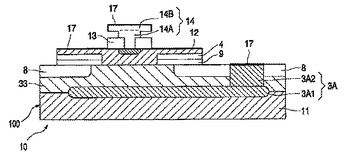

本発明のヘテロ接合バイポーラトランジスタは、半絶縁性InP基板1上に、N−型InGaAs/InAlGaAs/InPコレクタ層3、P+型InGaAsベース層4およびN型InPエミッタ層5が順次積層されている。更に、N型InPエミッタ層5はInPレッジ層構造7を備え、ベース電極10は、内部ベース電極12と外部ベース電極13から構成されており、内部ベース電極12は、コレクタメサ領域の外周部を自己整合的に規定しつつ、InPレッジ層構造7と接触し、外部ベース電極13の一部が、内部ベース電極12上に形成され、かつ、外部ベース電極13の残りの部分が、コレクタメサ領域外に形成された埋め込み層14上に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】バイポーラトランジスタの製造歩留まりを向上する。

【解決手段】半導体基板Subの主面上に、バイポーラトランジスタのコレクタを構成するコレクタ層CL、ベースを構成するベース層BLおよびキャップSi層BCL、およびエミッタを構成するエミッタ層ELが設けられている。このうち、ベース層BLとしてSiGe層を選択性エピタキシャル成長によって形成した後、キャップSi層BCLとしてSi層を非選択性エピタキシャル成長によって形成する。

(もっと読む)

SiGeバイポーラの歩留りを向上させるC打込み

【課題】SiGeヘテロ接合バイポーラ・トランジスタを製造するだけでなく、SiGeバイポーラの歩留まりも向上させる方法を提供すること。

【解決手段】本発明の方法は、以下の素子領域、すなわちコレクタ領域、サブコレクタ領域、外部ベース領域、およびコレクタ−ベース接合領域の1つへの、炭素、Cのイオン打込みを含む。好ましい実施形態では、前記領域のそれぞれに打込みCを含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】トレンチ構造のトランジスタの電極を確実に分離することができる半導体装置及び該半導体装置の製造方法を提供する。

【解決手段】各凹部10aの側面及び各凹部10a周辺のシリコン基板10上面には、シリコン酸化膜11が形成してあり、さらに、シリコン酸化膜11の上面には、シリコン窒化膜13が形成されている。シリコン窒化膜13の縁辺は、シリコン酸化膜11の縁辺より突出させてオーバハング形状(庇状)にしてある。また、各凹部10aの開口部周りのシリコン酸化膜11は、等方性エッチングによってオーバハング形状にしてある。すなわち、各凹部10aの開口部周りは、シリコン窒化膜13によるオーバハングとシリコン酸化膜11によるオーバハングが形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】庇部を有する電極の庇部下の空洞を絶縁膜で埋め込むことで、層間絶縁膜や配線の段切れ、配線の短絡等を防止することを可能とする。

【解決手段】基板10に形成された導電層(エミッタキャップ層15)に接続されるもので庇部20a有するコンタクト電極(エミッタ電極)20と、エミッタ電極20の庇部20a下の空洞28部分に埋め込まれた絶縁膜31と、エミッタ電極20および絶縁膜31側部を被覆する層間絶縁膜21と、層間絶縁膜21に形成された接続孔24を通じてエミッタ電極20に接続されるとともに、層間絶縁膜21上をエミッタ電極20上より電極周辺部に配設されている配線27とを備えたことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、分離領域を構成するP型の埋込拡散層の横方向拡散幅が広がる等により、所望の耐圧特性を得難いという問題があった。

【解決手段】本発明の半導体装置では、P型の単結晶シリコン基板6上に2層のエピタキシャル層7、8が形成され、エピタキシャル層8はエピタキシャル層7よりも高不純物濃度である。エピタキシャル層7、8は、分離領域3、4、5により複数の素子形成領域に区分され、素子形成領域の1つには、NPNトランジスタ1が形成されている。そして、NPNトランジスタ1のベース領域として用いられるP型の拡散層12とP型の分離領域3との間にはN型の拡散層14が形成されている。この構造により、ベース領域−分離領域間がショートし難くなり、NPNトランジスタ1の耐圧特性を向上させることができる。

(もっと読む)

縦型バイポーラ素子の製造方法

【課題】ベース領域が小さい場合でも、ベース領域の低濃度部分によるトランジスタ動作や、低濃度部分に起因するパンチスルーの発生を防ぎ、素子動作が高速で、かつ確実な縦型バイポーラ素子の製造方法を提供する。

【課題の解決手段】縦型バイポーラ素子の製造工程において、コレクタ層1を形成したシリコン基板上に素子分離用のフィールド酸化膜2を形成する工程と、シリコン基板に対してフィールド酸化膜2をマスクとしてベース領域3を形成するためにベース不純物をイオン注入する工程と、このイオン注入工程の後になされたフィールド酸化膜2の膜厚調整のためのエッチング工程等によって後退したフィールド酸化膜2をマスクとして、ベース領域3に再度同一導電型のベース不純物を同一条件でイオン注入する工程と、再度イオン注入を行ったベース領域3にエミッタ不純物を注入してエミッタ領域4を形成する工程とを含むものである。

(もっと読む)

ヘテロ接合型半導体装置及びその製造方法

【課題】 ベース・コレクタ間容量及びベースコンタクト抵抗を共に減少させて、高周波特性等の特性の向上を図ることができる、ヘテロ接合型半導体装置及びその製造方法を提供すること。

【解決手段】少なくともコレクタ層3とベース層4とエミッタ層5とからなる積層体を有するヘテロ接合型バイポーラトランジスタ24aであって、エミッタキャップ層6、エミッタ層5及びコレクタ層3がアンダーカット形状をなし、各アンダーカット部に有機絶縁膜9A、9Bが充填されていると共に、エミッタ電極7に対して自己整合的に形成されたベース層4の側面から上面の一部にかけてベース電極12が全方向蒸着後のリフトオフによって形成されている、ヘテロ接合型バイポーラトランジスタ24a。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】 ヘテロ接合バイポーラトランジスタにおいて、信頼性が高く、低コストのトランジスタを提供する。

【解決手段】 基板と、前記基板上に形成された第1導電型のコレクタ領域と、前記コレクタ領域上に形成された第2導電型のベース領域と、前記ベース領域上に形成された第1導電型のエミッタ領域と、を有するヘテロ接合バイポーラトランジスタであって、前記エミッタ領域が、Inx(GayAl1−y)1−xAs(0≦x≦1、0≦y≦1)からなるアンドープ層と、前記アンドープ層の表面の一部にメサ状に形成され前記アンドープ層と格子整合する材料からなり前記アンドープ層よりも第1導電型不純物濃度が高い第1導電型のメサ構造部と、を有し、前記メサ構造部の側面と、前記アンドープ層の前記表面のうちの前記メサ構造部を囲む領域と、が金属保護層により覆われ、前記金属保護層が、前記アンドープ層とショットキー接合を形成し、真空蒸着により形成可能な材料からなることを特徴とするヘテロ接合バイポーラトランジスタを提供する。

(もっと読む)

半導体装置

【課題】 高性能な半導体装置を提供する。

【解決手段】 シリコン基板1上に素子分離膜3に周囲を囲まれた活性領域2aを設ける。活性領域2aの上に、ベース層として機能するSiGe合金層4およびエミッタ層として機能するn型拡散層5を設ける。SiGe合金層4およびn型拡散層5は、シリコン酸化膜からなる側壁膜6で囲われる。n型拡散層5の上の多結晶シリコン膜7およびシリサイド膜8は、n型拡散層5、側壁膜6、及び素子分離膜3にまたがって設けられる。尚、多結晶シリコン膜7の下に位置する側壁膜6は、活性領域2aと素子分離膜3との境界50にまたがって設けられる。そして層間絶縁膜10を設けて平坦化した後、素子分離膜3の上のシリサイド膜8に接続するように、エミッタ層(n型拡散層5)につながるエミッタ引き出し電極21を形成する。ここで、エミッタ引き出し電極21は、一方の素子分離膜3の上から活性領域2aの上を通って反対側の素子分離膜3の上にまで連続して設けられた多結晶シリコン膜7の両側に配置されている。

(もっと読む)

半導体装置

【課題】 高性能な半導体装置を提供する。

【解決手段】 シリコン基板1に、素子分離膜3に囲まれた活性領域2aが設けられる。活性領域2aの上には、ベース層として機能するSiGe合金層4およびエミッタ層として機能するn型拡散層5を設け、SiGe合金層4と素子分離膜3との間の活性領域2aの表面に溝60が設けられる。またSiGe合金層4およびn型拡散層5は、シリコン酸化膜からなる側壁膜6で囲われる。この側壁膜6は、活性領域2aの表面に設けられた溝60を埋め込むとともに、溝60と素子分離膜3との境界50にまたがって設けられる。n型拡散層5の上の多結晶シリコン膜7およびシリサイド膜8は、n型拡散層5、側壁膜6、及び素子分離膜3にまたがって設けられる。そして層間絶縁膜10を設けて平坦化した後、素子分離膜3の上のシリサイド膜8に接続するように、エミッタ層(n型拡散層5)につながる引き出し電極21が設けられる。

(もっと読む)

バイポーラ・トランジスタを有する半導体装置の製造方法及びバイポーラ・トランジスタを有する装置

本発明は、バイポーラ・トランジスタ装置(10)の製造に関し、この装置内に、絶縁層(13)内のウィンドウ内に存在し絶縁層(13)を覆って横方向に延びる多結晶シリコン領域(14)を用いて、エミッタが形成される。シリコン領域(14)、並びに、絶縁領域(13)及びシリコン領域(14)のスタックに隣接する別のシリコン領域(12)が、この構造を覆って堆積される金属層(16)によってシリサイド化される。形成されるシリサイド(17)のブリッジを回避する手段がスタックの側面に形成される。本発明によれば、形成されるシリサイドのブリッジを回避するための手段は、シリコン領域(14)の上面とスタックの側面の表面に沿った他のシリコン領域(12)の上面との間の間隔が、絶縁層(13)と半導体層(14)の厚さの合計よりも大きく形成されるように、スタックの側面が構築されることを備える。スタック側面の正又は負の傾斜によって増大された通路によりシリサイドのブリッジが回避される。好ましい実施形態は、スタックの側面がどのように構築されるかに関する。  (もっと読む)

(もっと読む)

1 - 14 / 14

[ Back to top ]