Fターム[5F003BC02]の内容

バイポーラトランジスタ (11,930) | コレクタ (1,152) | 付加領域(PN接合、絶縁物、溝、キラー) (104)

Fターム[5F003BC02]に分類される特許

1 - 20 / 104

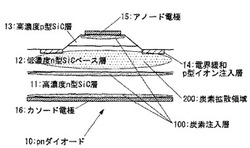

SiCバイポーラ型半導体素子

【課題】キャリア捕獲中心の少ないSiC半導体素子を提供する。

【解決手段】n型またはp型のSiC基板11と、n型またはp型の少なくとも1つのSiCエピタキシャル層12、あるいはn型またはp型の少なくとも1つのイオン注入層14と、を有し、pn接合界面付近および伝導度変調層(ベース層)内を除いた、SiC基板表面付近、SiC基板とSiCエピタキシャル層との界面付近、およびSiCエピタキシャル層の表面付近のうち少なくとも1つの領域100に、炭素注入層、珪素注入層、水素注入層、またはヘリウム注入層を有し、かつ、炭素原子、珪素原子、水素原子、またはヘリウム原子をイオン注入することで導入した格子間炭素原子をアニーリングにより伝導度変調層内へ拡散させるとともに格子間炭素原子と点欠陥とを結合させることで、電気的に活性な点欠陥が低減された領域を伝導度変調層内に有するSiCバイポーラ型半導体素子。

(もっと読む)

炭化珪素半導体装置

【課題】エミッタ層からコレクタ層を経由してベース層へ移動する電荷の移動を阻止し、エミッタ層からコレクタ層を経由してベース層に注入される電荷を無くすことで、コレクタ層における欠陥の成長を防止することが可能な炭化珪素半導体装置を提供する。

【解決手段】本発明の炭化珪素半導体装置は、炭化珪素半導体基板により構成された炭化珪素半導体装置であり、第1の導電型のコレクタ層102と、コレクタ層の上部に設けられた第2の導電型のベース層104と、ベース層の一部として設けられたベース電極105と、ベース層上に設けられベース電極と離間して設けられたエミッタ層107と、ベース電極からエミッタ層に対して移動する電荷の経路において、コレクタ層内に設けられた、コレクタ層内における電荷の経路を遮断する絶縁体層112とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】少工数で製造可能で且つ高い耐圧性能を有する半導体装置を提供する。

【解決手段】素子形成領域と、素子形成領域を外部領域から絶縁分離するべく素子形成領域表面から基板表面までの深さで素子形成領域側面を包囲するよう形成された第1絶縁トレンチ領域10aとを備える半導体装置であって、素子形成領域は、埋め込みコレクタ領域と、コレクタ耐圧領域4と、ベース領域5と、表面コレクタ領域8bと、エミッタ領域8aと、ベース領域と表面コレクタ領域との間におけるキャリアの直線的な移動を遮るよう、当該領域間において素子形成領域表面から基板表面にまでの深さで形成される第2絶縁トレンチ領域10bとを備え、半導体装置を平面視した際、第2絶縁トレンチと第1絶縁トレンチ領域との間には、キャリアが第2絶縁トレンチを迂回してベース領域と表面コレクタ領域との間を移動するためのキャリア迂回領域12a,12bが形成される。

(もっと読む)

バイポーラ半導体素子

【課題】高温や電流密度が高い条件下でも基板へ少数キャリアが到達するのを防いで、順方向電圧の増大を防ぐことができるバイポーラ半導体素子を提供する。

【解決手段】このSiC pinダイオード20では、n型SiC基板21とn型バッファ層22との間に形成したn型少数キャリア消滅層31は、n型バッファ層22よりも炭素空孔欠陥の濃度が高く、少数キャリア消滅層31の炭素空孔欠陥はp型のアノード層24,25からの正孔のトラップとして働く。よって、小数キャリア消滅層31に達した正孔(少数キャリア)がトラップされ、小数キャリア消滅層31において正孔密度K2が急激に減衰する。これにより、正孔(少数キャリア)が基板21へ到達することを防いで、基板21から積層欠陥が拡大するのを防いで、順方向電圧の増大を防止できる。

(もっと読む)

半導体基板

【課題】AlGaAs/InGaP界面の遷移層の形成を抑制する。

【解決手段】ヒ素化合物からなる第2半導体と、リン化合物からなる第3半導体とを含み、前記第2半導体と前記第3半導体とが接触しており、前記第2半導体が第1原子を第2濃度で含有し、かつ第2原子を含有し、前記第1原子が前記第2半導体に第1伝導型のキャリアを発生させ、前記第2濃度が、前記第2半導体にドープする前記第1原子の量を増加するに従い増加するキャリア数が飽和し始める前記第1原子の濃度以上の濃度であり、前記第2原子が前記第2半導体におけるフェルミ準位と電荷中性準位との差を小さくする半導体基板提供する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】バイポーラトランジスタが動作する際に、ベース領域のうちコレクタ側の端部が破壊されることを抑制する。

【解決手段】ベース領域150は、ウェル110内に形成されている。エミッタ領域170はベース領域150の中に形成され、ベース領域150より浅い。コレクタ領域140はウェル110内に形成され、ベース領域150の外側に位置している。第1埋込領域180は、少なくとも一部がベース領域150の中に位置しており、ベース領域150よりも不純物濃度が高い。そして第1埋込領域180は、平面視において、エミッタ領域170とコレクタ領域140の間に少なくとも一部が位置している。また第1埋込領域180は、エミッタ領域170の縁のうち少なくとも一辺と重なっており、かつエミッタ領域170の全面には重なっていない。

(もっと読む)

バイポーラトランジスタ

【課題】表面酸化膜下の界面近傍で発生する降伏を防ぎ、ツェナー降伏によるブレークダウン電圧の経時変動を防ぐバイポーラトランジスタを提供することを目的としている。

【解決手段】第一導電型半導体基体3内に不純物濃度が第一導電型半導体基体3より高い第一導電型の電流経路領域4と、電流経路領域4内に第二導電型の表面降伏防止領域5と、第一導電型半導体基体3表面に電流経路領域4と表面降伏防止領域5に接し不純物濃度が表面降伏防止領域5より高い第二導電型のベース領域6と、第一導電型半導体基体3表面に電流経路領域4と表面降伏防止領域5に接する第一導電型コレクタ領域7と、第一導電型半導体基体3表面かつ表面降伏防止領域5内に不純物濃度が電流経路領域4より高い第一導電型のエミッタ領域8と、表面降伏防止領域5内かつエミッタ領域8に接する不純物濃度が表面降伏防止領域5より高い第一導電型内部降伏誘導領域9を備える。

(もっと読む)

化合物半導体エピタキシャル基板

【課題】電流増幅率を向上させ、基板種に影響されず良好な特性のデバイスを製造できる化合物半導体エピタキシャル基板を提供すること。

【解決手段】GaAs基板2上に、サブコレクタ層41、コレクタ層42、ベース層43、エミッタ層44、エミッタコンタクト層46、47がこの順序で形成されている化合物半導体エピタキシャル基板1において、GaAs基板2とサブコレクタ層41との間に形成されるバッファ層3を酸素を含むAlx Ga1-x As (0≦X≦1)層とし、酸素を含むバッファ層3によりGaAs基板2に存在する欠陥の伝播を抑制し、ベース層43の結晶性を基板種によらず安定かつ良好にできるようにした。

(もっと読む)

バイポーラトランジスタの製造方法

【課題】最終的なコレクタを薄層化しつつ、広い線幅のSiO2細線を例とする絶縁物細線の埋め込みを可能にし、低消費電力での超高速動作が可能なバイポーラトランジスタの製造方法を提供すること。

【解決手段】半絶縁性基板1上にサブコレクタ層2を形成する工程と、サブコレクタ層2上に絶縁物3の細線を形成する工程と、サブコレクタ層2および絶縁物3の細線を覆うコレクタ層4を形成する工程とを有するバイポーラトランジスタの製造方法において、前記サブコレクタ層2および絶縁物3の細線を覆うコレクタ層4を形成する工程は、コレクタ層2の表面をエッチングする工程を含むことを特徴とするバイポーラトランジスタの製造方法を構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の特性を向上できると共に、製造コストを低減できる。

【解決手段】本発明の例に関わる半導体装置は、半導体基板1上に順次積層されたコレクタ層2A、ベース層3A及びエミッタ層4Aと、コレクタ層2Aの側面上に設けられ、コレクタ層に対して歪み応力を与える第1ストレスソース膜15Aと、ベース層3Aの側面上に設けられ、ベース層3Aに対して歪み応力を与える第2ストレスソース膜17と、を具備し、第1ストレスソース膜15A上端及び前記ベース層上端は、半導体基板表面から同じ高さに位置し、第2ストレスソース膜17は、ベース層3Aの側面と第1ストレスソース膜15Aの側面との間に設けられる。

(もっと読む)

半導体装置、光ディスク装置

【課題】電流利得のばらつきを低減することができる半導体装置を提供する。

【解決手段】第1導電型の半導体基体1と、この半導体基体1の表面の一部に形成された、バイポーラトランジスタの第2導電型のコレクタ層2と、このコレクタ層2の一部に形成された、バイポーラトランジスタの第1導電型のベース層6と、このベース層6の一部に形成された、バイポーラトランジスタの第2導電型のエミッタ層7と、このエミッタ層7の直下の領域を除いた部分の半導体基体1に形成された、第1導電型の半導体層9とを含む半導体装置を構成する。

(もっと読む)

バイポーラトランジスタ及びその製造方法

【課題】バイポーラトランジスタの高周波特性の向上を図る。

【解決手段】p型シリコン基板10上に形成されたn型導電型の第1コレクタ層14と、第1コレクタ層14上に形成された、第1コレクタ層14より幅の狭い、n型導電型の第2コレクタ層21と、第1コレクタ層14上に、第2コレクタ層21側面に接して形成された絶縁膜層20と、第2コレクタ層21上に形成された、p型導電型のベース層22と、ベース層22側面に接してに形成された、p型導電型のベース引き出し層25と、ベース層22上に形成された、n型導電型のエミッタ領域32とを備える。第1コレクタ層14とベース層22の間、又は第1コレクタ層14とベース引き出し層25の間に、絶縁膜層20が形成されていることにより、ベース・コレクタ間の接合容量を低減させる。

(もっと読む)

n型ベースを有するバイポーラトランジスタ及びその製造方法

【解決手段】ベースコンタクト接続部(12)、エミッタ部(4、5)及びコレクタ部がn層(3)上に配置され、当該n層は、更なるnpnバイポーラトランジスタために用いることができる。当該コレクタ部はエミッタ部に対して側方に配置され、当該エミッタ部及びコレクタ部の少なくとも一方は、当該n層の表面領域上でショットキーコンタクト(14)を備える。 (もっと読む)

半導体装置およびその製造方法

【課題】 シリコン基板上にゲルマニウムを主成分とする半導体素子を形成する際に、バッファ層を薄くすることで段差を減らし、同一基板上にシリコン系半導体素子を混載することを容易にする。

【解決手段】 具体例を述べれば、バッファ層をゲルマニウム層とシリコン層の2層とし、シリコン層のみを溶融することでゲルマニウムの面内原子間隔を安定的に保持するバッファ層を形成し、その上にゲルマニウム層を形成することで転位密度等の結晶欠陥を低減する。

(もっと読む)

ポリエミッタ型バイポーラトランジスタ、BCD素子、ポリエミッタ型バイポーラトランジスタの製造方法及びBCD素子の製造方法

【課題】複合高電圧素子工程を用いたポリエミッタ型バイポーラトランジスタ及びその製造方法、BCD(複合高圧)素子及びその製造方法を提供する。

【解決手段】実施の形態に係るポリエミッタ型バイポーラトランジスタは、半導体基板100の上側の一部に形成された埋込層110と、上記半導体基板の上に形成されたエピ層120と、上記エピ層に形成され、上記埋込層と連結されるコレクタ領域130と、上記エピ層の上側の一部に形成されたベース領域140と、上記ベース領域の基板の表面に形成され、ポリシリコン材質からなるポリエミッタ領域170と、を含む。実施の形態に係るBCD素子は、ポリシリコン材質からなるポリエミッタ領域を含むポリエミッタ型バイポーラトランジスタを含み、上記バイポーラトランジスタと同一な単一ウエハ上に形成されたCMOSとDMOSのうちの1つ以上のMOSを含む。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】自己発熱および高電流密度動作下においても劣化を生じにくく、高電流密度まで安定して通電可能な高信頼電極を有し、より高い信頼度を達成可能なヘテロ接合バイポーラトランジスタを提供すること。

【解決手段】半導体基板1上に、サブコレクタ層2、コレクタ層3、ベース層4、エミッタ層5およびエミッタコンタクト層6が順次積層されたヘテロ接合バイポーラトランジスタにおいて、エミッタコンタクト層6とエミッタ電極7との間に、Moの融点以上の融点を有する単体金属または合金からなるバリア金属層13−2(図2に示す)を有するバリア複合層13が介在することを特徴とするヘテロ接合バイポーラトランジスタを構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、エミッタ拡散層等を形成する際のマスクずれにより、デバイスサイズが縮小され難く、高耐圧化が達成され難いという問題があった。

【解決手段】本発明の半導体装置では、エミッタ領域としてのP型の拡散層18の周囲には、LOCOS酸化膜14、15、N型の拡散層22、23が形成される。N型の拡散層22、23の周囲には、コレクタ領域としてのP型の拡散層19、20が、N型の拡散層22、23と離間して形成される。この構造により、P型の拡散層18〜20、N型の拡散層22、23が位置精度良く形成され、ベース領域幅Wb1が狭められ、高耐圧の横型PNPトランジスタが形成される。

(もっと読む)

半導体装置の製造方法

【課題】バイポーラトランジスタの特性が劣化するのを抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置100の製造方法は、シリコン基板11の領域A上にプレーナ型のバイポーラトランジスタ1を形成する工程と、プレーナ型バイポーラトランジスタ1が形成される領域を覆うようにシリコン窒化膜からなるカバー膜32aを形成する工程と、その後、プレーナ型のバイポーラトランジスタ1が形成される領域Aがカバー膜32aに覆われた状態で、バイポーラトランジスタ1が形成される領域にイオン注入する工程とを備える。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】コレクタ電流が流れている状態でのオン抵抗および耐圧を両方同時に向上させることが可能なHBTを提供する。

【解決手段】n型のGaAsサブコレクタ層101と、GaAsサブコレクタ層101上に形成されたInGaPコレクタ層102と、InGaPコレクタ層102上に形成されたn型のGaAsスペーサ層103と、GaAsスペーサ層103上に形成されたn型のGaAs第2コレクタ層104およびGaAs第1コレクタ層105と、GaAs第1コレクタ層105上に形成されたp型のGaAsベース層110と、GaAsベース層110上に形成されたn型のInGaPエミッタ層111とを備え、GaAsサブコレクタ層101は、GaAs第2コレクタ層104およびGaAs第1コレクタ層105より高いキャリア濃度を有し、GaAs第2コレクタ層104はGaAs第1コレクタ層105より高いキャリア濃度を有する。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】コレクタ電流が流れている状態でのオン抵抗および耐圧を両方同時に向上させることが可能なHBTを提供する。

【解決手段】n型GaAsサブコレクタ層101と、GaAsサブコレクタ層101上に形成されたInGaPコレクタ層102と、InGaPコレクタ層102上に形成されたn型GaAsコレクタ層103と、GaAsコレクタ層103上に形成されたp型GaAsベース層104と、GaAsベース層104上に形成されたn型GaAsエミッタ層105とを備え、GaAsサブコレクタ層101のキャリア濃度は、GaAsコレクタ層103のキャリア濃度より高く、InGaPコレクタ層102とGaAsサブコレクタ層101との間には、p型GaAsスペーサ層110が挿入される。

(もっと読む)

1 - 20 / 104

[ Back to top ]