Fターム[5F004EA26]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711) | フロー工程 (20) | 液体塗布 (14)

Fターム[5F004EA26]に分類される特許

1 - 14 / 14

半導体装置の作製方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等の膜パターンを有する基板を作製する方法、さらには、低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供することを目的とする。

【解決手段】基板上に形成された絶縁膜、半導体膜又は導電膜上に接して第1の膜を形成する工程と、第1の膜上に第1のマスク材料を含有する溶液を吐出して第1の膜上に第1のマスクを形成する工程と、第1のマスクを用いて第1の膜をパターニングして絶縁膜、半導体膜又は導電膜表面上に塗れ性の低い領域と塗れ性の高い領域を形成する工程と、第1のマスクを除去する工程と、塗れ性の低い領域に挟まれた塗れ性の高い領域に、第2のマスク材料を含有する溶液を吐出して第2のマスクを形成する工程と、第2のマスクを用いて、パターニングされた第1の膜をエッチングするとともに絶縁膜、半導体膜又は導電膜をエッチングする。

(もっと読む)

半導体装置の製造方法

【課題】サイドウォールスペーサを利用してリソグラフィー解像限界未満のパターンと任意の寸法のパターンとが混在するパターンを形成する。

【解決手段】アモルファスカーボン膜3及びシリコン酸窒化膜4からなる被エッチング部材上に塗布膜5をスピン塗布法により成膜し、塗布膜5をパターニングすることによってサイドウォールコアを形成し、サイドウォールコアの少なくとも側面を覆うシリコン酸化膜7を成膜し、シリコン酸化膜7上に有機反射防止膜8をスピン塗布法により成膜する。次いで、有機反射防止膜8をエッチングすることによって、シリコン酸化膜7の凹部7aを覆う埋込マスクを形成し、シリコン酸化膜7をエッチングすることにより、サイドウォールコアまたは埋込マスクと重ならない被エッチング部材を露出させ、被エッチング部材をエッチングすることでフォトリソグラフィー解像限界未満のパターンを得る。

(もっと読む)

半導体素子の微細パターン形成方法

【課題】半導体素子の微細パターン形成方法を提供する。

【解決手段】半導体素子の微細パターン形成方法はパターン対象層上に多数の第1感光膜パターンを形成しS100、パターン対象層および多数の第1感光膜パターン上に境界膜を形成しS110、境界膜上に平坦化膜を形成しS120、平坦化膜上に多数の第2感光膜パターンを形成しS130、多数の第2感光膜パターンを利用して多数の平坦化膜パターンを形成しS140、多数の平坦化膜パターンおよび多数の第1感光膜パターンを利用して多数のパターン対象層パターンを形成するS150ことを含む。

(もっと読む)

基板上のシリコン含有反射防止コーティング層の再加工方法

半導体デバイス製造においてシリコン含有反射防止コーティング(SiARC)層を有する膜構造を再加工する方法が供される。当該方法は、上にSiARC層を有する膜積層体を含む基板、及び、前記SiARC層上に形成されるレジストパターンを供する工程を有する。当該方法はさらに、前記SiARC層から前記レジストパターンを除去する工程、前記SiARC層を、オゾン(O3)気体を含む処理気体に曝露することで、前記SiARC層を改質する工程、希釈フッ化水素(DHF)液体によって前記の改質されたSiARC層を処理する工程、及び、遠心力により、前記基板から前記の改質されたSiARC層を除去する工程を有する。  (もっと読む)

(もっと読む)

シリコン化合物の製造方法

【課題】シリコン及び/又はその化合物表面に残存する水酸基を、より完全性よくメトキシ基に置換した表面を形成し、疎水性、安定性及び電気化学的質に優れたシリコン化合物の製造方法を提供すること。また、極めて穏和な条件にてシリコン及び/又はその化合物表面に残存する水酸基をメトキシ化でき、表面を疎水性へ改質するシリコン化合物の表面改質方法を提供すること。

【解決手段】表面に、水酸基を有したシリコン及び/又はその化合物を、トリフルオロメタンスルホン酸メチル、フルオロスルホン酸メチル等からなる有機メトキシ化剤及び塩基化合物に接触させ、該水酸基をメトキシ化する。

(もっと読む)

使用済み半導体ウエハ又は基板の再生方法

【課題】使用済みの半導体ウエハを、より少ない損失量で使用済み半導体ウエハや基板を再生する技術を提供すること。

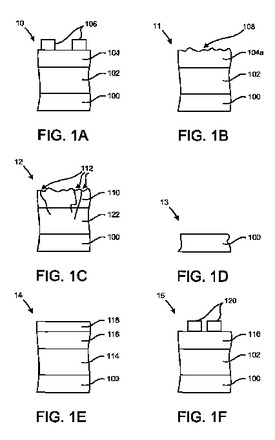

【解決手段】(a)表面に機能層を有する使用済みの半導体ウエハ1を粗削りし、機能層を除去する工程と、(b)粗削りした半導体ウエハ1の表面に、ドライエッチングにより除去可能な保護層2を形成する工程と、(c)保護層2を形成した半導体ウエハ1をドライエッチングし、保護層2と、ウエハ1表面のうち保護層2により被覆されずに露出する部分とを除去する工程と、(d)ドライエッチングした半導体ウエハ1の平坦度を計測する工程と、を含み、(d)工程において所望の平坦度が得られない場合、所望の平坦度が得られるまで(b)から(d)までの工程を繰り返す。

(もっと読む)

半導体素子の微細パターン形成方法

【課題】本発明は、半導体素子の微細パターン形成方法に関する。

【解決手段】より具体的には被食刻層が備えられた基板上に第1〜第3のマスクパターンからなる積層パターンを形成する段階と、前記第3のマスク膜を食刻バリアに利用して第2のマスクパターンを側面食刻する段階と、前記第3のマスクパターンを除去する段階と、前記第2のマスクパターンの上部を露出するスピンオンカーボン層を形成する段階と、前記スピンオンカーボン層を食刻バリアに利用して被食刻層を露出させる段階と、前記スピンオンカーボン層を除去する段階とを含む半導体素子の微細パターン形成方法に関する。

(もっと読む)

半導体製造装置

【課題】RIE処理時に発生する反応生成物を効率よく除去できるようにする。

【解決手段】ガス供給機構10が、処理基板Sの周縁部Saに向けて不活性ガスを噴出するため、多量の反応生成物が付着したとしても2工程以上の薬液処理を行う必要なく不活性ガスの噴出処理によって反応生成物を除去することができる。

(もっと読む)

シリコン基板の粗面化方法および光起電力装置の製造方法

【課題】従来の方法では困難だった15cm角程度あるいはそれ以上の大面積基板を対象にしても、シリコン基板に均一な凹凸を再現性良く、低コストで形成すること。

【解決手段】有機金属溶液あるいは有機金属の分散液を基板にインクジェット法でドット状に塗布する工程と、上記基板を乾燥する工程と、上記基板の表面にプラズマを照射する工程と、上記基板をエッチング処理する工程とを備えたシリコン基板の粗面化方法である。

(もっと読む)

半導体素子のハードマスクパターン形成方法

【課題】露光装備の解像能力以下のピッチを持つハードマスクパターンを形成するための、半導体素子のハードマスクパターン形成方法を提供すること。

【解決手段】エッチング対象層が形成された半導体基板上に第1ハードマスク層及び第2ハードマスク層を順次形成し、前記第2ハードマスク層上に第1パターンを形成し、前記第1パターンの表面にスペーサを形成し、前記スペーサが形成された前記第1パターン同士の間に第2パターンを形成し、前記スペーサを除去し、前記第1パターン及び前記第2パターンをエッチングマスクとして用いるエッチング工程によって前記第2ハードマスク層及び前記第1ハードマスク層をエッチングしてハードマスクパターンを形成することを含む、半導体素子のハードマスクパターン形成方法を提供する。

(もっと読む)

構造体の製造方法

【課題】ハードマスクの除去を必要としない構造体の製造方法を提供する。

【解決手段】 酸化ケイ素を有する構造体の製造方法である。基板上に、有機SOGからなる第一の層を形成する工程と、この第一の層の上に、無機SOGからなる第二の層を形成する工程を有する。その後、第二の層に形成された前記パターンをマスクとして、第一の層をエッチングし、第一の層と第二の層とを焼成することにより、酸化ケイ素を有する構造体を作製する。

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等の膜パターンを有する基板を作製する方法、さらには、低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供する。

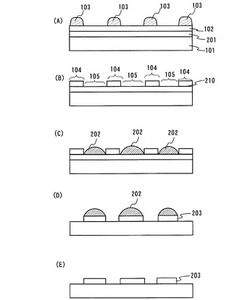

【解決手段】基板101上に第1の膜102を形成する工程と、前記第1の膜102上にマスク材料を含有する溶液を吐出して前記第1の膜102上にマスク103を形成する工程と、前記マスク103を用いて前記第1の膜102をパターニングして前記基板101上に塗れ性の低い領域104と塗れ性の高い領域105を形成する工程と、前記マスク103を除去する工程と、前記塗れ性の低い領域104に挟まれた前記塗れ性の高い領域105に、絶縁膜、半導体膜又は導電膜材料を含有する溶液106を吐出して絶縁膜、半導体膜又は導電膜のパターンを形成する工程とを有する。

(もっと読む)

近接場露光によるレジストパターンの形成方法、及び該レジストパターンの形成方法を用いた基板の加工方法、デバイスの作製方法

【課題】高アスペクトなパターンの形成が可能となる近接場露光によるレジストパターンの形成方法、及び該レジストパターンの形成方法を用いた基板の加工方法、デバイスの作製方法を提供する。

【解決手段】近接場露光用マスクを基板上に形成したレジスト層に近接させ、該マスクの面側に光を照射した際に該マスクの微小開口から滲み出る近接場光を用いて露光し、前記レジスト層にマスクパターンを転写する近接場露光によるレジストパターンの形成方法において、前記基板上に、近接場光のしみ出し深さ以上の厚さのネガ型レジスト層を形成する工程と、前記ネガ型レジスト層を、前記近接場光を用いて露光する露光工程と、前記露光されたネガ型レジスト層を現像液で現像し、該ネガ型レジスト層の厚さよりも浅い領域にパターンを形成する現像工程と、を少なくとも有する構成とする。

(もっと読む)

半導体装置の製造方法

【課題】 シリル化プロセスを用いて微細なパターンの形成を可能とし、しかもシリル化部表面に形成されるSiOx 層の除去を支障なく行うことのできる、半導体装置の製造方法が提供が望まれている。

【解決手段】 下地基板20上の被パターニング層23上にレジスト層24を形成し、次にレジスト層24の所定箇所を露光し、次いでこの露光工程後のレジスト層24における未露光部分をシリル化する。続いて、露光した箇所のレジスト層24をドライ現像によって除去し、シリル化された部分に対応した積層パターン30を得る。次いで、積層パターン30からその表層部に形成されたSiOx層29を除去してレジストパターン32を形成する。その後、レジストパターン32をマスクにして被パターニング層23をエッチングする。

(もっと読む)

1 - 14 / 14

[ Back to top ]