Fターム[5F032CA13]の内容

Fターム[5F032CA13]の下位に属するFターム

受動素子(L、C、R) (148)

ダイオード (188)

電界効果トランジスタ (1,841)

バイポーラトランジスタ (198)

サイリスタ (12)

相補型 (349)

その他の素子 (96)

Fターム[5F032CA13]に分類される特許

1 - 7 / 7

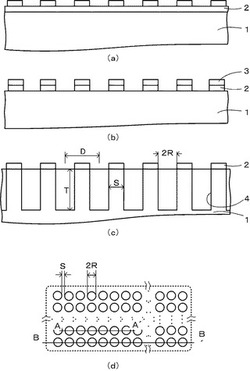

半導体基板または半導体装置の製造方法

【課題】平板状空洞を形成する際におけるホール半径Rと、ホールとホールの最短距離Sのプロセスマージンを広げ、信頼性の高い半導体装置の製造方法を提供すること。

【解決手段】半導体基板1の表面にホール4を複数形成し、非酸化性雰囲気のアニール処理により、該半導体基板1の表面を半導体の表面マイグレーションを利用して平坦化し、基板内部に平板状空洞6を形成する際に、前記ホール4の開口部が閉じる前に半導体のソースガスを供給する。

(もっと読む)

固体撮像装置およびその製造方法

【課題】本発明は、受光センサー部内のP型領域のホウ素がN型領域中へ拡散することを抑制して飽和電荷量の低下を抑えることを可能にする。

【解決手段】半導体基板11に形成されたN型領域13と、前記N型領域13上に形成された第1炭化シリコン層21と、前記炭化シリコン層21上に形成されたシリコン層22からなるP型領域14とで構成されたフォトダイオード15を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】SOI基板を用いてトレンチ素子分離構造を適用した場合、トレンチ側壁の酸化時にトレンチコーナー部の酸化膜が薄膜化し、応力集中により素子領域の半導体層に達する結晶欠陥が発生する。

【解決手段】本発明にかかる半導体装置は、SOI基板201と、SOI基板201の素子分離領域において基板表面部を貫通し第1の絶縁層204に達する複数の溝205と、溝205の側面を酸化することによって形成される酸化膜層219および酸化膜層219を被覆する第4の絶縁層220と、溝205の内側に酸化膜層219および絶縁層220とを介して形成された埋込層211と、前記埋込層を被覆し、かつ複数の溝205及び素子形成領域以外の他の領域を含む素子分離領域を被覆する第3の絶縁層212とを備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】サブコンタクトはプロセス上の制約から要する面積が大きくなる。

【解決手段】上層Si基板12、SiO2膜層14、下層Si基板16からなるSOI基板にSiO2膜22およびPoly−Si26からなる素子分離用絶縁膜を形成すると同時に埋め込みSiO224を埋め込んだサブコンタクト用のホールを形成する。ウェットエッチングにより埋め込みSiO224を途中までエッチングした後、トランジスタ28上の引き出し電極用コンタクトホールを形成すると同時に、SOI基板のSiO2膜層14まで貫通するサブコンタクト用のコンタクトホール40を形成する。その後、各コンタクトホールをWで埋め込むことにより、Wプラグ44と同時にサブコンタクト42を形成する。

(もっと読む)

半導体装置

【課題】駆動電圧の異なる集積回路を同一の半導体基板に親和性よく形成することを可能にした半導体装置を提供する。

【解決手段】周辺回路16の周囲を取り囲むように素子分離絶縁膜18が形成されている。周辺回路16は、半導体基板17の表面においてCCDイメージセンサ11との間で素子分離されている。周辺回路16下には、高エネルギー、高濃度で酸素イオンを注入し、熱処理を施してなる埋め込み絶縁層(SIMOX絶縁層)32が形成されている。この埋め込み絶縁層32は、素子分離絶縁膜18の下部に接続されている。周辺回路16は、CMOS回路からなり、駆動電圧が低い。周辺回路16は、駆動電圧の高いCCDイメージセンサ11から完全に絶縁分離されており、この絶縁分離により集積回路間の駆動電圧の影響が遮断されている。

(もっと読む)

半導体素子の製造方法

【課題】薄い半導体層に素子分離層を安定して形成することができると共に、バーズビークの形成を抑制する手段を提供する。

【解決手段】支持基板と、該支持基板上方の半導体層とを有する半導体基板に形成する形成する半導体素子の製造方法が、トランジスタ形成領域と素子分離領域とを設定した半導体基板を準備する工程と、半導体基板の半導体層上にパッド酸化膜を形成する工程と、パッド酸化膜上に耐酸化性マスク層を形成する工程と、耐酸化性マスク層上にトランジスタ形成領域を覆うレジストマスクを形成する工程と、このレジストマスクをマスクとして耐酸化性マスク層をエッチングして素子分離領域のパッド酸化膜を露出させる第1のエッチング工程と、レジストマスクを除去し、露出した耐酸化性マスク層をマスクとして露出させたパッド酸化膜の下の半導体層をLOCOS法により酸化し、素子分離層を形成する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】所望する微細な加工形状を得るための半導体装置の製造方法を提供する。

【解決手段】ナイトライド膜103及びレジストパターン104を覆うアモルファスカーボン膜にスパッタリングを行って、レジストパターン104の側壁上にアモルファスカーボン膜106を形成する。レジストパターン104とアモルファスカーボン膜106とをマスクにして、シリコン基板上101、酸化膜102及びナイトライド膜103をパターニングする。

(もっと読む)

1 - 7 / 7

[ Back to top ]