Fターム[5F032CA21]の内容

素子分離 (28,488) | 関連技術 (4,816) | 素子領域に形成される素子の種類 (2,839) | その他の素子 (96)

Fターム[5F032CA21]に分類される特許

1 - 20 / 96

半導体装置の製造方法

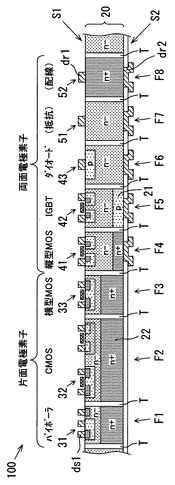

【課題】能動素子または受動素子が一つの半導体基板に複数個形成されてなる半導体装置およびその製造方法であって、両面電極素子についても絶縁分離と集積化が可能であり、安価に製造することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板20が、当該半導体基板20を貫通する絶縁分離トレンチTに取り囲まれて、複数のフィールド領域F1〜F8に分割されてなり、複数個の能動素子31〜33,41〜43または受動素子51,52が、それぞれ異なるフィールド領域F1〜F8に分散して配置されてなり、二個以上の素子が、当該素子に通電するための一組の電極dr1,dr2が半導体基板20の両側の表面S1,S2に分散して配置されてなる、両面電極素子41〜43,51,52である半導体装置100とする。

(もっと読む)

半導体装置

【課題】バルク半導体基板上に形成されるトンネルトランジスタ同士を電気的に分離することが可能な半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板内に形成された第1および第2の素子分離絶縁膜とを備える。さらに、前記装置は、前記第1および第2の素子分離絶縁膜間の前記半導体基板上に、ゲート絶縁膜を介して形成されたゲート電極を備える。さらに、前記装置は、前記半導体基板内に前記ゲート電極を挟むように形成された、第1導電型の第1の主端子領域および前記第1導電型とは逆導電型の第2導電型の第2の主端子領域を備える。さらに、前記装置は、前記半導体基板内に前記第1および第2の素子分離絶縁膜に接するように形成され、前記第1および第2の主端子領域の下面よりも深い位置に上面を有する、前記第2導電型の第1の拡散層を備える。

(もっと読む)

半導体装置の製造方法およびCMOSイメージセンサーの製造方法

【課題】 半導体装置に発生するノイズを低減する

【解決手段】 シリコン基板100の第1部分110を覆い、シリコン基板100の第1部分110に隣接する第2部分120を覆わない窒化シリコン膜200をマスクとしてシリコン基板100を熱酸化することにより、酸化シリコン膜300を形成する。窒化シリコン膜200をマスクとして酸化シリコン膜300のバーズビーク部310の下へ斜めイオン注入を行うことにより、不純物領域121を形成する。

(もっと読む)

半導体装置

【課題】より確実に画素間クロストークを抑制することが可能な、固体撮像素子を備える半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面上に配置された第1導電型の不純物層DPWと、不純物層DPW上に、第1導電型の不純物領域と第2導電型の不純物領域とが互いに接合する構成を含む光電変換素子と、光電変換素子を含む単位画素を構成し、光電変換素子と電気的に接続されるトランジスタM1〜M4とを備えている。平面視において光電変換素子の外周部の少なくとも一部には、内部に空隙AGが含まれ、光電変換素子と、光電変換素子に隣接する光電変換素子とを、互いに電気的に絶縁する分離絶縁層SIが配置されている。上記分離絶縁層SIは、第1導電型の不純物層DPWの最上面に接する。

(もっと読む)

半導体装置の製造方法

【課題】SON構造の半導体装置において、フォトリソグラフィー工程で高精度の位置合わせができ、プロセスラインの汚染を防止することができて、素子特性の劣化が防止され、信頼性の高い半導体装置の製造方法を提供する。

【解決手段】SON構造9上部のシリコン層32の段差18をアライメントマーク20として用いることによって、アライメントマーク20の形状崩れが防止されて、フォトリソグラフィー工程で高精度の位置合わせができるようになる。また、段差18が小さいためにフォトリソグラフィー工程で凹部へのレジストの残留やプロセス途中で発生するゴミの残留が防止され、プロセスラインの汚染が防止できる。その結果、素子特性の劣化が防止され、信頼性の高い半導体装置の製造方法を提供することができる。

(もっと読む)

半導体装置

【課題】従来に比してオン電圧性能に優れた横型IGBT、および順方向電圧特性に優れた横型FWDを同一基板上に構成可能とする半導体装置を提供する。

【解決手段】半導体基板上において、横型IGBTと、横型FWDとが、絶縁体であるトレンチ絶縁仕切り部を挟むように横方向に隣接配置されて成る半導体装置であって、横型IGBTは、平面視した場合に、エミッタ領域と当該横型IGBTのドリフト領域との境界面の幅がコレクタ領域と当該横型IGBTのドリフト領域との境界面の幅より狭くなるよう形成されており、横型FWDは、平面視した場合に、カソード領域と当該横型FWDのドリフト領域との境界面の幅がアノード領域と当該横型FWDのドリフト領域との境界面の幅より狭くなるよう形成されていることを特徴とする、半導体装置。

(もっと読む)

液晶表示装置、及びその作製方法

【課題】作製工程を削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】島状半導体層を形成するためのフォトリソグラフィ工程及びエッチング工程を省略し、ゲート電極(同一層で形成される配線等を含む)を形成する工程、ソース電極及びドレイン電極(同一層で形成される配線等含む)を形成する工程、コンタクトホールを形成する(コンタクトホール以外の絶縁層等の除去を含む)工程、画素電極(同一層で形成される配線等を含む)を形成する工程の4つのフォトリソグラフィ工程で液晶表示装置を作製する。コンタクトホールを形成する工程において、半導体層が除去された溝部を形成することで、寄生チャネルの形成を防ぐ。

(もっと読む)

固体撮像装置、及び固体撮像装置の製造方法。

【課題】 本発明は、リセットトランジスタまたは増幅トランジスタと光電変換部とを分離するための素子分離領域で発生する暗電流によるノイズを低減するとともに、画素の微細化に有利な固体撮像装置を提供することを目的とする。

【解決手段】 第1画素領域には光電変換部、FD、及び転送トランジスタが画素を単位として行列状に配される。第2画素領域には増幅トランジスタ、及びリセットトランジスタが配される。第1画素領域には第1素子分離部が配され、第2画素領域には第2素子分離部が配される。第1素子分離部において絶縁膜が半導体基板内部に突出する量が、第2素子分離部において絶縁膜が半導体基板内部に突出する量に比べて小さい。配線が配された第1主面側とは反対の第2主面側から、光電変換部に光が入射する。

(もっと読む)

半導体装置

【課題】IGBT素子領域とダイオード素子領域とを同一半導体基板に備えた逆導通型の半導体装置において、電流検知領域によるIGBT検知電流、ダイオード検知電流の検知精度を向上させる。IGBTとダイオードとの境界部分によって検知電流が不安定化することを抑制する。

【解決手段】電流検知領域を主活性領域のIGBT素子領域に隣接して配置し、IGBT素子領域のコレクタ領域を電流検知領域のコレクタ領域に接するまで伸ばす。IGBTとダイオードとの境界部分による影響を受けにくくなるため、IGBT検知電流が安定化する。同様に、電流検知領域を主活性領域のダイオード素子領域に隣接して配置し、ダイオード素子領域のカソード領域を電流検知領域のカソード領域に接するまで伸ばす。これによって、ダイオード検知電流が安定化する。

(もっと読む)

固体撮像装置及びその製造方法

【課題】素子を分離するための素子分離部による不具合の発生確率を低減する。

【解決手段】フォトダイオード310が内部に形成された半導体基板500と、素子分離部420とを備える。素子分離部420は、該素子分離部420の少なくとも一部が、半導体基板500に形成された溝410の内部に充填されるように形成される。素子分離部420は、溝410の内部の下方に形成されたシリコン酸化膜421と、溝410の内部の上方に形成されたシリコン酸化膜422とから構成される。シリコン酸化膜421の密度は、シリコン酸化膜422の密度より小さい。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ分離されたSOI基板にIGBTとその制御回路等が形成される半導体装置において、IGBTの高耐圧化及びターンオフ特性の改善等が必要になる。

【解決手段】ダミー半導体基板16にN型エピタキシャル層8を形成し、N型エピタキシャル層8にトレンチ30を形成し、トレンチ30側壁及びN型エピタキシャル層8表面にN型バッファ層7、次にP型埋め込みコレクタ層6を形成し、トレンチ30底面及びP+型埋め込みコレクタ層6上を埋め込み絶縁膜5で被覆する。埋め込み絶縁膜5上をポリシリコン膜3で被覆し、該ポリシリコン膜3と絶縁膜2を介してP型半導体基板1を貼り合わせた後、ダミー半導体基板16を除去し、略同一平面状に露出するトレンチ30底面の埋め込み絶縁膜5、P+型埋め込みコレクタ層6、N型バッファ層7、N型ドリフト層8a等を具備するSOI基板を形成する。該SOI基板にIGBT等を形成する。

(もっと読む)

半導体装置

【課題】小型化を実現し、かつ耐圧の高い半導体装置を提供すること。

【解決手段】活性領域10と分離領域30との間に設けられた耐圧構造部20は、順方向耐圧構造領域40と逆方向耐圧構造領域50とからなる。順方向耐圧構造領域40および逆方向耐圧構造領域50には、複数のフィールドリミッティングリング(FLR)41,51と、複数のフィールドプレート(FP)44,54が設けられている。複数のFP44のうち、最も逆方向耐圧構造領域50のFP(第1順方向FP)45は、分離領域30側に張り出すように設けられている。複数のFP54のうち、最も順方向耐圧構造領域40のFP(第1逆方向FP)55は、活性領域10側に張り出すように設けられている。順方向の電圧印加時、第1逆方向FP55は、分離領域30から伸びる空乏層を止める。逆方向の電圧印加時、第1順方向FP45は、活性領域10から伸びる空乏層を止める。

(もっと読む)

トレンチ分離型逆阻止MOS型半導体装置およびその製造方法

【課題】逆阻止用のトレンチを充填しなくても、ウエハプロセスを高良品率にすることのできるトレンチ分離型逆阻止MOS型半導体装置およびその製造方法を提供する。

【解決手段】第1導電型半導体基板と該半導体基板の第2主面に形成される第2導電型領域とにより構成される逆阻止接合を備え、前記半導体基板の第1主面から前記逆阻止接合に達する深さであって、該逆阻止接合を底面として前記半導体基板を囲む環状のトレンチと、該トレンチの側壁に、前記第2導電型領域と導電接続する第2導電型分離領域を有するトレンチ分離型逆阻止MOS型半導体装置において、高温水素アニール処理によりトレンチ103の開口部106をシリコン表面マイグレーションにより塞いでウエハ表面を平坦化させてトレンチ埋め込みレス分離構造とする。

(もっと読む)

半導体装置

【課題】dv/dtサージにより、支持基板と活性層との間の絶縁膜にて構成される寄生容量を充放電する変位電流による回路誤動作を防止する。

【解決手段】低電位基準回路部LVおよび高電位基準回路部HVを構成する絶縁分離された半導体素子の外周に、n型ガードリング42c等を形成すると共に、活性層2cの埋込絶縁膜2b側にn型ガードリング埋込層42c等と同じ導電型の深いn型拡散領域42b等を形成する。また、活性層2cにて構成されるn-型層42a等の中にp型ウェル42d等を形成し、このp型ウェル42d内に半導体素子を形成する。n型ガードリング42c等とp型ウェル42d等は、それぞれ逆バイアスまたは同電位となるように電位固定する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体支持基板界面の品質を向上する。

【解決手段】半導体支持基板12、絶縁層14及びシリコン層16の三層構造を有するSOI基板10と、シリコン層16及び絶縁層14を貫通する穴部20と、穴部20の底部に形成された熱酸化膜22と、半導体支持基板12の熱酸化膜22下で、熱酸化膜22と接触する拡散層28と、を備える

(もっと読む)

半導体装置及びその製造方法

【課題】不純物の拡散によるナローチャネル効果の発生を抑制することを可能にする半導体装置を提供する。

【解決手段】半導体基体1と、半導体基体1に少なくとも一部が埋め込まれた、素子分離のための絶縁層2と、半導体基体1内に形成された不純物領域を含んで成る能動素子と、絶縁層2と半導体基体1との間に形成された、負の固定電荷を有する膜11とを含んで半導体装置を構成する。

(もっと読む)

領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法

【課題】従来の領域分割基板と較べて部分領域を引き出し導電領域として利用した場合の抵抗値が小さく、導電性、半導電性または絶縁性の任意の基板材料を用いることができ、適用制限の少ない領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法を提供する。

【解決手段】基板30の第1表面S1から第2表面S2に亘って、当該基板30を貫通するように形成されたトレンチ31aによって、当該基板30が複数の部分領域Ceに分割され、トレンチ31aによって形成された部分領域Ceの側壁に、第1表面S1の側から第2表面S2の側に亘って、当該基板30より高い導電率を有する導電層35が形成され、導電層35を介して、トレンチ31a内に絶縁体31bが埋め込まれてなる領域分割基板A10とする。

(もっと読む)

固体撮像装置およびその製造方法

【課題】本発明は、受光センサー部内のP型領域のホウ素がN型領域中へ拡散することを抑制して飽和電荷量の低下を抑えることを可能にする。

【解決手段】半導体基板11に形成されたN型領域13と、前記N型領域13上に形成された第1炭化シリコン層21と、前記炭化シリコン層21上に形成されたシリコン層22からなるP型領域14とで構成されたフォトダイオード15を有する。

(もっと読む)

半導体装置

【課題】バイポーラの高耐圧縦型PNPプロセスをベースにして、寄生PNPトランジスタに起因する漏洩電流の発生しない高耐圧IGBTを形成する。

【手段】P型半導体基板1に、IGBTのコレクタ電極15と電気的に接続するP+型コレクタ層8と、当該P+型コレクタ層8と連続するP+型埋め込み層4と、該P+型埋め込み層4の下層のN型埋め込み層2と、該P+型埋め込み層4と該N型埋め込み層2の間のN+型埋め込み層3とを形成する。また、N+型埋め込み層3の端部と一体となり、前記P型半導体基板1上に形成されたN型エピタキシャル層5の表面まで延在し、コレクタ電極15と電気的に接続されたN+型導電層7を形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】特性の良い光電変換素子を有する半導体装置を提供することを目的の一とする。または、簡単な工程で、特性の良い光センサ光電変換装置を有する半導体装置を提供することを目的の一とする。

【解決手段】光透過性を有する基板と、光透過性を有する基板上の絶縁層と、絶縁層上の、光電変換を奏する半導体領域、第1の導電型を示す半導体領域、および、第2の導電型を示す半導体領域を有する単結晶半導体層と、第1の導電型を示す半導体領域と電気的に接続された第1の電極と、第2の導電型を示す半導体領域と電気的に接続された第2の電極とを有する光電変換素子とを備える半導体装置を提供する。

(もっと読む)

1 - 20 / 96

[ Back to top ]