Fターム[5F032CA14]の内容

素子分離 (28,488) | 関連技術 (4,816) | 素子領域に形成される素子の種類 (2,839) | 受動素子(L、C、R) (148)

Fターム[5F032CA14]に分類される特許

1 - 20 / 148

半導体装置の製造方法

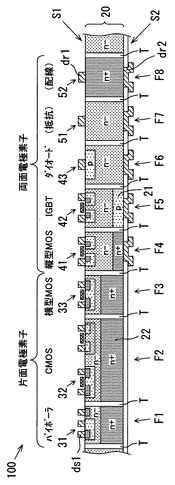

【課題】能動素子または受動素子が一つの半導体基板に複数個形成されてなる半導体装置およびその製造方法であって、両面電極素子についても絶縁分離と集積化が可能であり、安価に製造することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板20が、当該半導体基板20を貫通する絶縁分離トレンチTに取り囲まれて、複数のフィールド領域F1〜F8に分割されてなり、複数個の能動素子31〜33,41〜43または受動素子51,52が、それぞれ異なるフィールド領域F1〜F8に分散して配置されてなり、二個以上の素子が、当該素子に通電するための一組の電極dr1,dr2が半導体基板20の両側の表面S1,S2に分散して配置されてなる、両面電極素子41〜43,51,52である半導体装置100とする。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】トランジスタのオン電流を十分に確保することが可能な信頼性の高い半導体装置を提供する。

【解決手段】活性領域6を分断する2つの埋め込みゲート用の溝部8a,8bにゲート絶縁膜9を介して埋め込まれたゲート電極7a,7bと、2つの埋め込みゲート用の溝部8a,8bによって分断された3つの活性領域6a,6b,6cのうち、中央部に位置する活性領域6bを分断するビットコンタクト用の溝部11の両側面に、埋め込みゲート用の溝部8a,8bの底面と同程度の深さで不純物を拡散させることによって形成された第1の不純物拡散層13a,13bと、中央部を挟んだ両側に位置する活性領域6a,6cに、ゲート電極7a,7bの上面と同程度の深さで不純物を拡散させることによって形成された第2の不純物拡散層14a,14bとを備える。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】露光光源として真空紫外光を用いるホトリソ技術のパターン解像限界より微細な拡散抵抗を製造することはできないから、高抵抗の拡散抵抗は実現できなかった。

【解決手段】一組の薄膜構造体の対向する間隔に、サイドウォール形成用の絶縁膜を形成する際に生じる空隙を利用して露光光源として真空紫外光を用いるホトリソ技術のパターン解像限界より微細な拡散抵抗を形成する。薄膜構造体を配線抵抗として利用すれば、これらを接続して設けることにより温度特性に優れる抵抗素子を構成することもできる。

(もっと読む)

半導体装置

【課題】回路誤動作を防止できる半導体装置を提供する。

【解決手段】低電位基準回路部LVおよび高電位基準回路部HVを構成する絶縁分離された半導体素子の外周に、n型ガードリング42c等を形成する。また、活性層2cにて構成されるn-型層42a等の中にp型ウェル42d等を形成し、このp型ウェル42d内に半導体素子を形成する。また、外部電源61に接続されるラインを電源供給ラインとガードリング端子固定ラインとを分岐し、電源供給ラインの電流が流れないガードリング端子固定ラインに抵抗63を備えることで、バイパスコンデンサ64をディスクリート部品としなくても良い回路構成とする。

(もっと読む)

半導体装置

【課題】ブートストラップ方式のドライブ回路を有する半導体装置において、ブートストラップダイオードの順バイアス時にp-基板側に流れるホールによるリーク電流を抑制することができる半導体装置を提供することにある。

【解決手段】ブートストラップダイオードDb下にSON構造の空洞3を形成し、ブートストラップダイオードDbとグランド電位(GND)となるGNDp領域4との間のn-エピ層2にその空洞3に達するフローティングp領域5を形成することで、外部のブートストラップコンデンサC1充電時のp-基板1へのホールによるリーク電流を抑えることができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】信頼性の高い半導体装置を実現する。

【解決手段】半導体装置100は、基板30と、基板30に埋め込まれた絶縁膜20と、絶縁膜20上に形成された複数の抵抗素子10と、を備えている。基板30は、複数の抵抗素子10を有する抵抗素子形成領域40において複数の凸部32を有している。複数の凸部32は、絶縁膜20に入り込んでおり、かつ上端が絶縁膜20の表面よりも低い。このため、信頼性の高い半導体装置を実現することが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】素子分離用ゲート電極のみのしきい値電圧を高くすることができ、素子分離用ゲート電極の底部にチャネルが形成されない半導体装置を提供する。

【解決手段】半導体基板1に形成された複数の活性領域と、これら活性領域同士を区画する素子分離領域と、活性領域内を複数の素子領域に区画する第1素子分離用トレンチ32Aと、隣接する第1素子分離用トレンチ32A間に設けられ、第1素子分離用トレンチ32Aの深さよりも浅く形成されたゲートトレンチ31Aと、絶縁膜25を介して第1素子分離用トレンチ32A内に形成された素子分離用電極32と、ゲート絶縁膜26Aを介してゲートトレンチ31A内に形成されたゲート電極31と、を具備してなり、素子分離用電極32底部に成膜されている絶縁膜25の膜厚が、ゲート電極31の底部に成膜されているゲート絶縁膜26Aの膜厚よりも厚いことを特徴とする。

(もっと読む)

半導体装置及びその製造方法並びに抵抗器及び半導体素子

【課題】pn接合におけるリーク電流を抑制する。

【解決手段】N−型半導体層10と、シリサイド層20sがその表面に形成されたP−型半導体層20とが、絶縁体9上に形成される。半導体層10にはPMOSトランジスタを、半導体層20にはNMOSトランジスタを、それぞれ形成することができる。半導体層10,20がpn接合J50aを形成する場合、これはシリサイド層20sの端部から近く、結晶欠陥が小さい位置に存在するので、ここにおけるリーク電流は非常に小さい。半導体層10,20が形成するpn接合は、シリサイド層20sの端部から2μm以下の距離にあることが望ましい。

(もっと読む)

半導体装置

【課題】正確にメインセルに流れる電流を検出することができると共に、高い電圧が用いられる場合でもその影響を受け難い半導体装置を提供する。

【解決手段】メインセルとセンスセルとをトレンチ分離構造1dによって絶縁分離する。これにより、メインセルのコレクタに対して100V以上の高電圧が印加されても、それに起因するノイズが電流検出用の出力端子に誘起されないようにできる。また、センスセルのエミッタ電位がセンス抵抗Rsに流れる電流によって上昇しても、メインセルのエミッタと電気的に完全に分離されているため、寄生トランジスタが動作することもない。勿論、抵抗層14から発生させられたノイズが電流検出用の出力端子に誘起されることも抑制できる。したがって、正確にメインセルに流れる電流を検出することができると共に、高い電圧が用いられる場合でもその影響を受け難い半導体装置とすることが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】ダミーアクティブ領域の配置に伴うチップ面積の増大を引き起こすことなく、半導体基板の表面の平坦性を向上させる。

【解決手段】ダミーアクティブ領域であるn型埋込み層3の上部には、厚い膜厚を有する高耐圧MISFETのゲート絶縁膜7が形成されており、このゲート絶縁膜7の上部には、内部回路の抵抗素子IRが形成されている。n型埋込み層3と抵抗素子IRとの間に厚いゲート絶縁膜7を介在させることにより、基板1(n型埋込み層3)と抵抗素子IRとの間に形成されるカップリング容量が低減される構造になっている。

(もっと読む)

半導体装置

【課題】複数のフローティング領域の間の電位差の不均一を軽減することができる半導体装置を提供する。

【解決手段】半導体装置は、領域3(k)と領域3(k+1)間に、外部容量6(k)を備えている。複数の外部容量6(k)は、その容量がkの増加とともに(即ち、図1の紙面右側から紙面左側に向かうほど)大きくなるように選定されている。この構造により、領域3(k)と領域3(k+1)間の電位差の不均一を軽減することができる。

(もっと読む)

浅いトレンチ分離および基板貫通ビアの集積回路設計への統合

【課題】浅いトレンチ分離および基板貫通ビアの集積回路設計への統合を提供すること。

【解決手段】ICを製造する方法は、第1の側、および第2の対向する側を有する基板を用意すること、基板の第1の側にSTI開口を形成すること、および基板の第1の側に部分的TSV開口を形成すること、および部分的TSV開口を延長することを含む。延長された部分的TSV開口は、STI開口より基板内への深さが深い。方法はまた、STI開口を第1の固体材料で充填すること、および延長された部分的TSV開口を第2の固体材料で充填することを含む。STI開口、部分的TSV開口、または延長された部分的TSV開口のいずれも、基板の第2の側の外面を貫通しない。少なくとも、STI開口および部分的TSV開口は同時に形成され、またはSTI開口および延長された部分的TSV開口は同時に充填される。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、トランジスタを容易にOn(オン)させることが可能で、かつ良好なデータ保持特性を実現することの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板12に形成され、第1の方向に延在する第1の素子分離用51、及び第1の素子分離用溝51を埋め込む第1の素子分離用絶縁膜53よりなり、複数の素子形成領域Rを有した活性領域16を区画する第1の素子分離領域14と、半導体基板12に、第1の方向と交差する第2の方向(Y方向)に延在するように形成され、第1の素子分離領域14の一部を分断する第2の素子分離用溝54、及び第2の素子分離用溝54を埋め込む第2の素子分離用絶縁膜56よりなり、複数の素子形成領域Rを区画する第2の素子分離領域17と、を有する。

(もっと読む)

液晶表示装置、及びその作製方法

【課題】作製工程を削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】島状半導体層を形成するためのフォトリソグラフィ工程及びエッチング工程を省略し、ゲート電極(同一層で形成される配線等を含む)を形成する工程、ソース電極及びドレイン電極(同一層で形成される配線等含む)を形成する工程、コンタクトホールを形成する(コンタクトホール以外の絶縁層等の除去を含む)工程、画素電極(同一層で形成される配線等を含む)を形成する工程の4つのフォトリソグラフィ工程で液晶表示装置を作製する。コンタクトホールを形成する工程において、半導体層が除去された溝部を形成することで、寄生チャネルの形成を防ぐ。

(もっと読む)

エピレス基板における分離型の相補型MOS装置

【課題】高い実装密度を得ることが可能な半導体装置の製造プロセスを提供する。

【解決手段】半導体装置を電気的に分離するための構造は、エピタキシャル層を含まない半導体基板240内にドーパントを打込むことにより形成される。この打込みに続き、極めて限られた熱収支に上記構造を晒すことでドーパントが顕著に拡散しないようにする。その結果として、上記分離構造の寸法が制限かつ規定され、こうして、エピタキシャル層を成長させる工程とドーパントを拡散させる工程とを含む従来のプロセスを用いて得られるよりも高い実装密度を得ることができる。

(もっと読む)

薄膜トランジスタとその製造方法、薄膜トランジスタアレイとその製造方法、及び、ディスプレイ装置

【課題】製造工程において半導体膜の膜質を低下させることなくその性能を維持し、少ない工程数によって、かつ、製造上の歩留まり及びスループットの優れた構造を有する薄膜トランジスタ及びその製造方法等を提供する。

【解決手段】薄膜トランジスタ100は、酸化物半導体膜120を有し、当該酸化物半導体膜120は、各薄膜半導体毎に、ゲート電極160下及び隣接された薄膜トランジスタ間とにそれぞれ形成された第1領域121及び122と、ソース電極140及びドレイン電極150下であって第1領域121の前記水平方向におけるそれぞれの両端に並設されており、ソース電極140及びドレイン電極150にそれぞれ電気的に接続され、かつ、非駆動時に前記第1領域121及び122より低抵抗である第2領域123及び124と、を有している。

(もっと読む)

半導体素子分離方法

【課題】

本発明の目的は、超高集積素子で素子分離膜の側壁に沿って生じる反転によるリーク電流発生を抑制し、トレンチ内部にキャパシタンスが小さくして素子のRC遅延を減少させた半導体素子の素子分離方法を提供することにある。

【解決手段】

シリコン基板に形成され、複数の微細トレンチの側壁となる少なくとも一つのシリコン柱をトレンチの下部に含むトレンチと、前記複数の微細トレンチの内部に埋め込まれた素子分離絶縁膜とを備え、シリコン柱を含むことによりリーク電流発生を抑制し、微細トレンチに空洞を形成して素子のRC遅延を減少させることを特徴とする。

(もっと読む)

電子装置、電子装置の素子分離方法、電子装置の製造方法、及び電子装置を備えた表示装置

【課題】半導体電子素子を含む電子装置の微細化、及び低コスト化を実現する。

【解決手段】半導体膜を含む電子素子を複数備える電子装置であって、電子素子の素子間に素子分離領域が存在し、素子分離領域は、バンドギャップが1.95eV以上である半導体膜と、絶縁体膜と、素子分離電極と、を含み、素子分離電極は、絶縁体膜によって素子分離領域の半導体膜と隔てられ、電圧が印加されて素子分離領域の半導体膜を高抵抗化し、電子素子間を電気的に分離するための電極であることを特徴とする電子装置。

(もっと読む)

半導体装置

【課題】デカップリング容量及びガードリング等のノイズを低減する構造物を設けるための専用配置領域を必要としない半導体集積回路装置を提供する。

【解決手段】P−型シリコンからなる支持基板2を設け、この支持基板2上にP+型シリコン層3を設け、その上にN+型シリコン層4及びP+型シリコン層12を相互に同層に設ける。P+型シリコン層3及びN+型シリコン層4の不純物濃度は支持基板2の不純物濃度よりも高くする。また、N+型シリコン層4及びP+型シリコン層12上の全面に、埋込酸化膜5及びSOI層6を設ける。そして、P+型シリコン層3を接地電位配線GNDに接続し、N+型シリコン層4を電源電位配線VDDに接続する。これにより、P+型シリコン層3とN+型シリコン層4との間に、電源に並列に接続されたデカップリング容量C1が形成される。

(もっと読む)

多層ウェーハ中のトレンチ構造

【課題】バーズビーク効果を軽減することのできる、SOIウェーハ内にトレンチを製造する方法を提供すること。

【解決手段】本発明は、基板と、基板上の酸化物層と、酸化物層上の半導体層とを備える多層ウェーハ内にトレンチ構造を製造する方法に関し、本方法は、半導体層および酸化物層を貫通して基板中へ延在するトレンチを形成するステップと、トレンチの内部表面において、半導体層のいくらかの材料が、トレンチの内部表面に露出した酸化物層の部分の一部の上に少なくとも流れるように、形成されたトレンチのアニール処理を行うステップとを含む。

(もっと読む)

1 - 20 / 148

[ Back to top ]