Fターム[5F032CA20]の内容

素子分離 (28,488) | 関連技術 (4,816) | 素子領域に形成される素子の種類 (2,839) | 相補型 (349)

Fターム[5F032CA20]に分類される特許

1 - 20 / 349

半導体装置およびその製造方法

半導体装置の製造方法

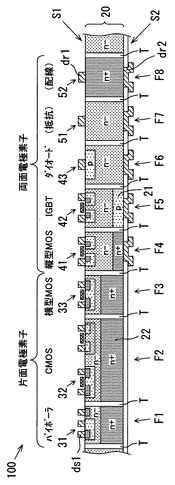

【課題】能動素子または受動素子が一つの半導体基板に複数個形成されてなる半導体装置およびその製造方法であって、両面電極素子についても絶縁分離と集積化が可能であり、安価に製造することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板20が、当該半導体基板20を貫通する絶縁分離トレンチTに取り囲まれて、複数のフィールド領域F1〜F8に分割されてなり、複数個の能動素子31〜33,41〜43または受動素子51,52が、それぞれ異なるフィールド領域F1〜F8に分散して配置されてなり、二個以上の素子が、当該素子に通電するための一組の電極dr1,dr2が半導体基板20の両側の表面S1,S2に分散して配置されてなる、両面電極素子41〜43,51,52である半導体装置100とする。

(もっと読む)

CMOS垂直置換ゲート(VRG)トランジスタ

【課題】本発明は、CMOS垂直置換ゲート(VRG)トランジスタを提供する。

【解決手段】集積回路構造は平面に沿って形成された主表面を有する半導体領域及び表面中に形成された第1及び第2のソース/ドレインドープ領域を含む。絶縁トレンチが第1及び第2のソース/ドレイン領域間に形成される。第1のソース/ドレイン領域とは異なる伝導形のチャネルを形成する第3のドープ領域が、第1のソース/ドレイン領域上に配置される。第4のドープ領域が第2のソース/ドレイン領域上に形成され、第2のソース/ドレイン領域とは相対する伝導形をもち、チャネル領域を形成する。第5及び第6のソース/ドレイン領域が、それぞれ第3及び第4のドープ領域上に形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】低耐圧トランジスタ特性への影響なく、耐圧特性および動作特性が安定した高耐圧素子を組み込む。

【解決手段】同一の半導体基板2上に、トレンチ分離絶縁膜(プラズマ酸化膜6)によって素子分離された高耐圧素子20aと低耐圧素子20bを設けた半導体装置1において、高耐圧素子形成領域におけるトレンチ分離絶縁膜(プラズマ酸化膜6)の表面高さが低耐圧素子形成領域におけるトレンチ分離絶縁膜(プラズマ酸化膜6)の表面高さよりも低く形成されている。高耐圧素子形成領域におけるトレンチ分離絶縁膜(プラズマ酸化膜6)の表面高さが、高耐圧素子20aのチャネルを形成する半導体基板2の表面に対して−10〜60nm(より好ましくは−10〜30nm)だけ高くなるように形成されている。

(もっと読む)

半導体装置の製造方法

【課題】注入した導電性不純物により形成される結晶欠陥の密度を低減し、歩留まり率が向上するような半導体装置の製造方法を提供する。

【解決手段】本発明の実施形態にかかる半導体装置の製造方法は、半導体基板を加熱することにより、半導体基板の基板温度を200から500℃の間の所望の温度に維持すると同時に、半導体基板に導電性不純物をイオン注入法もしくはプラズマドーピング法を用いてドーピングし、ドーピングした導電性不純物を活性化させるための活性化処理を行う。

(もっと読む)

半導体装置の製造方法

【課題】寄生抵抗が低く、接合リーク電流が抑制されたトランジスタを容易に形成することができる半導体装置の製造方法を提供する。

【解決手段】実施形態にかかる半導体装置の製造方法は、シリコン基板中のチャネル領域上にゲート絶縁膜を介してゲート電極を形成し、シリコン基板に所望の不純物を注入することにより、チャネル方向に沿ってチャネル領域を挟むようにシリコン基板中にソース領域とドレイン領域とを形成し、ソース領域及びドレイン領域の表面をアモルファス化することにより、それぞれの表面に不純物を含むアモルファス領域を形成し、アモルファス領域の上にニッケル膜を形成し、マイクロ波を照射して、アモルファス領域とニッケル膜とを反応させてニッケルシリサイド膜を形成しつつ、アモルファス領域を固相成長させてアモルファス領域に含まれる不純物を活性化し、未反応のニッケル膜を除去する。

(もっと読む)

半導体装置の製造方法、半導体装置、SOI基板の製造方法およびSOI基板

【課題】SOI基板のチャージ蓄積による不良を抑制する。

【解決手段】まず、シード基板100の一面に、シード基板100の表面と同一面を形成するように、開口部220を有する絶縁層200を形成する(絶縁層形成工程)。次いで、シード基板100の一面に接するように、支持基板300を貼り合せる(貼り合せ工程)。次いで、シード基板100または支持基板300の一方を薄板化することにより、当該薄板化基板からなる半導体層120を形成する(半導体層形成工程)。以上の工程により、SOI基板を準備する。次いで、半導体層120に半導体素子60を形成する(半導体素子形成工程)。

(もっと読む)

固体撮像装置および固体撮像装置の製造方法

【課題】本発明の一つの実施形態の目的は、素子分離特性を向上可能な固体撮像装置および固体撮像装置の製造方法を提供することである。

【解決手段】実施形態によれば、固体撮像装置の製造方法が提供される。固体撮像装置の製造方法は、素子分離領域形成工程と、電荷蓄積領域形成工程とを含む。素子分離領域形成工程では、第1導電型の半導体層をエピタキシャル成長させて光電変換素子間を分離する素子分離領域を形成する。電荷蓄積領域形成工程では、第2導電型の半導体層をエピタキシャル成長させて前記光電変換素子における電荷蓄積領域を形成する。

(もっと読む)

半導体装置、半導体ウエハ、及びこれらの製造方法

【課題】トランジスタ特性のバラツキが低減された半導体装置を提供する。

【解決手段】SOI基板101は、P型半導体層102の上にN型半導体層104が形成された半導体基板12、その上に形成されたBOX層106、及びBOX層上に形成されたSOI層108を有する。第1素子分離絶縁層110bは、SOI基板101に埋め込まれ、下端16がP型半導体層102に達し、第1素子領域(NFET領域30)と第2素子領域(PFET領域40)とを分離する。P型トランジスタ130bは、第1素子領域40に位置し、チャネル領域120bを有し、N型トランジスタ130aは、NFET領域30に位置し、チャネル領域120aを有する。第1バックゲートコンタクト134bは、第1素子領域40に位置する第2導電型層層104に、第2バックゲートコンタクト134aは、第2素子領域30に位置する第2導電型層104に接続される。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコンエピタキシャル層の支えの喪失を防止した、局所SOI構造の形成方法の提供。

【解決手段】SiGe混晶層31SG1〜31SG4とシリコンエピタキシャル層31ES1,31ES2,31ES3および31ES4が積層された構造において、

それぞれ、Nウェル31NW及びPウェル31PWがSiGe混晶層31SG1〜31SG4側に突き出る構造を形成し、SiGe混晶層31SG1〜31SG4をエッチングにより除去する際に、支えとなるようにする。

(もっと読む)

半導体装置

【課題】ブートストラップ方式のドライブ回路を有する半導体装置において、ブートストラップダイオードの順バイアス時にp-基板側に流れるホールによるリーク電流を抑制することができる半導体装置を提供することにある。

【解決手段】ブートストラップダイオードDb下にSON構造の空洞3を形成し、ブートストラップダイオードDbとグランド電位(GND)となるGNDp領域4との間のn-エピ層2にその空洞3に達するフローティングp領域5を形成することで、外部のブートストラップコンデンサC1充電時のp-基板1へのホールによるリーク電流を抑えることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】製造プロセスが複雑になるといったことを防ぎつつ、n型及びp型MOSトランジスタについて両方の性能を向上させた半導体装置を提供する。

【解決手段】半導体基板1の面内に、n型MOSトランジスタと、p型MOSトランジスタとを備える半導体装置であって、n型MOS型トランジスタが形成される第1の拡散層2aの間を絶縁分離する第1の絶縁層3aと、p型MOS型トランジスタが形成される第2の拡散層2cの間を絶縁分離する第2の絶縁層3bとを備え、第1の絶縁層3aは、半導体基板1の表層に形成された第1の溝部4aに、シリコン窒化膜5と、このシリコン窒化膜5の上にシリコン酸化膜6とを埋め込むことによって形成され、第2の絶縁層3bは、半導体基板1の表層に第1の溝部4aよりも幅広となるように形成された第2の溝部4bに、シリコン酸化膜6を埋め込むことによって形成されている。

(もっと読む)

半導体基板または半導体装置の製造方法

【課題】平板状空洞を形成する際におけるホール半径Rと、ホールとホールの最短距離Sのプロセスマージンを広げ、信頼性の高い半導体装置の製造方法を提供すること。

【解決手段】半導体基板1の表面にホール4を複数形成し、非酸化性雰囲気のアニール処理により、該半導体基板1の表面を半導体の表面マイグレーションを利用して平坦化し、基板内部に平板状空洞6を形成する際に、前記ホール4の開口部が閉じる前に半導体のソースガスを供給する。

(もっと読む)

半導体装置

【課題】より確実に画素間クロストークを抑制することが可能な、固体撮像素子を備える半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面上に配置された第1導電型の不純物層DPWと、不純物層DPW上に、第1導電型の不純物領域と第2導電型の不純物領域とが互いに接合する構成を含む光電変換素子と、光電変換素子を含む単位画素を構成し、光電変換素子と電気的に接続されるトランジスタM1〜M4とを備えている。平面視において光電変換素子の外周部の少なくとも一部には、内部に空隙AGが含まれ、光電変換素子と、光電変換素子に隣接する光電変換素子とを、互いに電気的に絶縁する分離絶縁層SIが配置されている。上記分離絶縁層SIは、第1導電型の不純物層DPWの最上面に接する。

(もっと読む)

半導体装置およびその製造方法

【課題】埋め込み絶縁層により活性層と支持基板とが電気的に絶縁された半導体基板において、支持基板の電位を活性層の表面から取り出すための基板コンタクトの低抵抗化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】活性層16に素子領域4およびコンタクト領域5が形成された厚膜SOI基板2において、CMOSトランジスタ7のB/L層29およびL/I層37、npnバイポーラトランジスタ8のコレクタ層49と同一層に、n型基板コンタクト12の貫通コンタクト58を取り囲むn型コンタクト埋め込み層57を形成する。

(もっと読む)

半導体装置及びその製造方法並びに抵抗器及び半導体素子

【課題】pn接合におけるリーク電流を抑制する。

【解決手段】N−型半導体層10と、シリサイド層20sがその表面に形成されたP−型半導体層20とが、絶縁体9上に形成される。半導体層10にはPMOSトランジスタを、半導体層20にはNMOSトランジスタを、それぞれ形成することができる。半導体層10,20がpn接合J50aを形成する場合、これはシリサイド層20sの端部から近く、結晶欠陥が小さい位置に存在するので、ここにおけるリーク電流は非常に小さい。半導体層10,20が形成するpn接合は、シリサイド層20sの端部から2μm以下の距離にあることが望ましい。

(もっと読む)

半導体装置の製造方法

【課題】塗布法を用いて形成される酸化膜を溝の内部に充填した溝型の素子分離部を有する半導体装置において、溝の内部におけるボイドの発生を抑制して、埋め込み不良を低減することのできる技術を提供する。

【解決手段】0.2μm以下の溝幅を有する溝4Sの内部に埋まるポリシラザン膜の上面がパッド絶縁膜3の上面よりも高く、かつ1.0μm以上の溝幅を有する溝4Lの内部に埋まるポリシラザン膜の上面がパッド絶縁膜3の上面よりも低くなるように、半導体基板1の主面上にポリシラザン膜を形成し、続いて、300℃以上の熱処理を行うことにより、ポリシラザン膜を酸化シリコン(SiO2)からなる第1埋め込み膜8へ転化すると同時に、溝4Sの上部に局所的に生じたボイドを消滅させる。

(もっと読む)

半導体装置およびその製造方法

【課題】ダミーアクティブ領域の配置に伴うチップ面積の増大を引き起こすことなく、半導体基板の表面の平坦性を向上させる。

【解決手段】ダミーアクティブ領域であるn型埋込み層3の上部には、厚い膜厚を有する高耐圧MISFETのゲート絶縁膜7が形成されており、このゲート絶縁膜7の上部には、内部回路の抵抗素子IRが形成されている。n型埋込み層3と抵抗素子IRとの間に厚いゲート絶縁膜7を介在させることにより、基板1(n型埋込み層3)と抵抗素子IRとの間に形成されるカップリング容量が低減される構造になっている。

(もっと読む)

埋め込みドープ層を有する完全空乏型SOIデバイス

【課題】完全空乏型SOIデバイスの製造に適したセミコンダクタオンインシュレータ(SeOI)ウェーハおよびそれを用いたデバイスを提供すること。

【解決手段】本発明は、第1の基板の表面領域にドープ層、ドープ層上に埋め込み酸化物層、埋め込み酸化物層上に半導体層を形成してSeOIウェーハを得る。SeOIウェーハの第2の領域の埋め込み酸化物層および半導体層を維持しながらSeOIウェーハの第1の領域から埋め込み酸化物層および半導体層を除去し、第2の領域に上部トランジスタを形成する。第1の領域にリセスチャネルアレイトランジスタを形成し、第2の領域にpチャネルトランジスタおよび/またはnチャネルトランジスタを形成する。ドープ層内またはこの近傍にバックゲートを形成し、第1の領域にリセスチャネルアレイトランジスタを形成し、ドープ層内またはその近傍にソース領域およびドレイン領域を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】包囲型ゲート電極付きの歪みSOI構造のMISFETの提供

【解決手段】

半導体基板1上に第1の絶縁膜2が設けられ、第1の絶縁膜2上に第2の絶縁膜3が選択的に設けられ、第2の絶縁膜3上に設けられた第1の半導体層5間に、第2の絶縁膜3が設けられていない部分上に設けられた第2の半導体層6が挟まれた構造からなる半導体層が島状に絶縁分離されて設けられ、第2の半導体層6の周囲にはゲート絶縁膜12を介して包囲型ゲート電極13が設けられ、第1の半導体層5には概略高濃度ソースドレイン領域(8、11)及び低濃度ソースドレイン領域(9、10)が設けられ、第2の半導体層6には概略チャネル領域が設けられ、高濃度のソースドレイン領域(8、11)及び包囲型ゲート電極13には配線体(17、18、20、21)が接続されているMISFET。

(もっと読む)

1 - 20 / 349

[ Back to top ]