Fターム[5F032CA18]の内容

素子分離 (28,488) | 関連技術 (4,816) | 素子領域に形成される素子の種類 (2,839) | バイポーラトランジスタ (198)

Fターム[5F032CA18]に分類される特許

1 - 20 / 198

半導体装置の製造方法

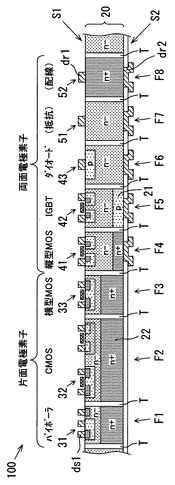

【課題】能動素子または受動素子が一つの半導体基板に複数個形成されてなる半導体装置およびその製造方法であって、両面電極素子についても絶縁分離と集積化が可能であり、安価に製造することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板20が、当該半導体基板20を貫通する絶縁分離トレンチTに取り囲まれて、複数のフィールド領域F1〜F8に分割されてなり、複数個の能動素子31〜33,41〜43または受動素子51,52が、それぞれ異なるフィールド領域F1〜F8に分散して配置されてなり、二個以上の素子が、当該素子に通電するための一組の電極dr1,dr2が半導体基板20の両側の表面S1,S2に分散して配置されてなる、両面電極素子41〜43,51,52である半導体装置100とする。

(もっと読む)

誘電体分離基板および半導体装置

【課題】深い不純物拡散層の形成が容易な誘電体分離基板および半導体装置を提供する。

【解決手段】誘電体分離基板10では、半導体基板11に第1の厚さt1を有する絶縁膜12が設けられている。絶縁膜12上に第2の厚さt2を有する第1導電型の半導体層13が設けられている。半導体層13の下部に絶縁膜12に接して第2導電型の不純物拡散層14が部分的に設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに絶縁分離された複数の素子を有する半導体装置の小型化と、その製造コストの低減とを実現できるようにする。

【解決手段】半導体装置は、第1の素子151、第2の素子152、第3の素子153及び第4の素子154を備えている。基板100は、基板を貫通する第1素子分離領域131により互いに分離された第1の区画101及び第2の区画102を有している。第1の区画は、第2素子分離領域132により互いに分離された第1素子領域121及び第2素子領域122を含む。第2の区画は、第3素子分離領域133により互いに分離された第3素子領域123及び第4素子領域124を含み、基板の裏面に露出した裏面拡散層を有している。第3の素子は、第3素子領域に形成され、第4の素子は、第4素子領域に形成され、第3の素子及び第4の素子は、裏面拡散層105を介在させて互いに接続されている。

(もっと読む)

半導体装置

【課題】微細化が可能であるメモリセル構造を備える半導体装置を提供する。

【解決手段】ワード線と、ビット線と、電源ノードと、ビット線と電源ノードとの間にPN結合を成す第1及び第2の領域並びに第2の領域とPN結合を成す第3の領域を少なくとも有するメモリ素子と、メモリ素子の第2の領域とは独立して設けられてメモリ素子の第2の領域と電気的に接続された第1の電極及び前記ワード線に接続された第2の電極を有するキャパシタと、を備える。

(もっと読む)

半導体装置

【課題】ブートストラップ方式のドライブ回路を有する半導体装置において、ブートストラップダイオードの順バイアス時にp-基板側に流れるホールによるリーク電流を抑制することができる半導体装置を提供することにある。

【解決手段】ブートストラップダイオードDb下にSON構造の空洞3を形成し、ブートストラップダイオードDbとグランド電位(GND)となるGNDp領域4との間のn-エピ層2にその空洞3に達するフローティングp領域5を形成することで、外部のブートストラップコンデンサC1充電時のp-基板1へのホールによるリーク電流を抑えることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】異なる不純物濃度の埋め込み層を有する半導体装置を短時間かつ低コストで製造する方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板の表面に第1の酸化膜11を形成する第1の酸化膜形成ステップと、フォトダイオードが形成される第1の領域に形成された前記酸化膜の一部を除去して第1の間隔で第1の開口部を形成すると共に、トランジスタが形成される第2の領域に形成された前記酸化膜を除去して前記半導体基板の表面を露出させる第1の開口部12を形成ステップと、前記第1の酸化膜をマスクとして利用して前記第1の開口部及び前記第2の領域に対して第1の不純物を注入する第1の不純物注入ステップと、前記第1の不純物を熱拡散させる第1の熱拡散ステップと、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】埋め込み絶縁層により活性層と支持基板とが電気的に絶縁された半導体基板において、支持基板の電位を活性層の表面から取り出すための基板コンタクトの低抵抗化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】活性層16に素子領域4およびコンタクト領域5が形成された厚膜SOI基板2において、CMOSトランジスタ7のB/L層29およびL/I層37、npnバイポーラトランジスタ8のコレクタ層49と同一層に、n型基板コンタクト12の貫通コンタクト58を取り囲むn型コンタクト埋め込み層57を形成する。

(もっと読む)

化合物半導体装置及び化合物半導体装置の製造方法

【課題】トレンチを用いて素子分離され、且つ、隣接素子の動作による影響が抑制された化合物半導体装置及び化合物半導体装置の製造方法を提供する。

【解決手段】半導体基板10と、キャリア走行層21とキャリア供給層22を有し、半導体基板上に配置された窒化物半導体層20と、上端部がキャリア走行層とキャリア供給層との界面よりも上方に位置する空洞40を内部に有する、窒化物半導体層の周囲を囲んで配置された素子分離絶縁膜30とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】少工数で製造可能で且つ高い耐圧性能を有する半導体装置を提供する。

【解決手段】素子形成領域と、素子形成領域を外部領域から絶縁分離するべく素子形成領域表面から基板表面までの深さで素子形成領域側面を包囲するよう形成された第1絶縁トレンチ領域10aとを備える半導体装置であって、素子形成領域は、埋め込みコレクタ領域と、コレクタ耐圧領域4と、ベース領域5と、表面コレクタ領域8bと、エミッタ領域8aと、ベース領域と表面コレクタ領域との間におけるキャリアの直線的な移動を遮るよう、当該領域間において素子形成領域表面から基板表面にまでの深さで形成される第2絶縁トレンチ領域10bとを備え、半導体装置を平面視した際、第2絶縁トレンチと第1絶縁トレンチ領域との間には、キャリアが第2絶縁トレンチを迂回してベース領域と表面コレクタ領域との間を移動するためのキャリア迂回領域12a,12bが形成される。

(もっと読む)

浅いトレンチ分離および基板貫通ビアの集積回路設計への統合

【課題】浅いトレンチ分離および基板貫通ビアの集積回路設計への統合を提供すること。

【解決手段】ICを製造する方法は、第1の側、および第2の対向する側を有する基板を用意すること、基板の第1の側にSTI開口を形成すること、および基板の第1の側に部分的TSV開口を形成すること、および部分的TSV開口を延長することを含む。延長された部分的TSV開口は、STI開口より基板内への深さが深い。方法はまた、STI開口を第1の固体材料で充填すること、および延長された部分的TSV開口を第2の固体材料で充填することを含む。STI開口、部分的TSV開口、または延長された部分的TSV開口のいずれも、基板の第2の側の外面を貫通しない。少なくとも、STI開口および部分的TSV開口は同時に形成され、またはSTI開口および延長された部分的TSV開口は同時に充填される。

(もっと読む)

半導体装置

【課題】同一基板上に混載された他の素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】半導体装置は、p形半導体層12と、n形のソース領域13と、絶縁体23と、n形半導体領域20と、n形のドレイン領域14と、p形のチャネル領域12aと、ゲート絶縁膜15と、ゲート電極16と、ソース電極18と、ドレイン電極19と、電極21とを備える。前記絶縁体は、前記p形半導体層の表面から前記p形半導体層の厚み方向に延びて形成されたトレンチt1内に設けられている。前記n形半導体領域は、前記ドレイン領域と前記絶縁体との間の前記p形半導体層の表面に設けられる。前記電極は、前記n形半導体領域に接続される。

(もっと読む)

半導体装置の製造方法

【課題】低コストで高い信頼性を有する逆阻止型の半導体装置およびその製造方法を提供する。

【解決手段】半導体チップを構成する表面構造133、裏面構造134を形成した薄い半導体ウェハ101を両面粘着テープ137で支持基板141に貼り付け、薄い半導体ウェハ101にスクライブラインとなるトレンチを湿式異方性エッチングで結晶面を出して形成し、結晶面が露出したトレンチの側面に逆耐圧を維持する分離層145を裏面拡散層であるpコレクタ領域110と接して表面側に延在するようにイオン注入と低温アニールまたはレーザーアニールで形成する。レーザーダイシングを行って、分離層145の下でコレクタ電極111を過不足なくきれいに切断した後、両面粘着テープ137をコレクタ電極111から剥がして半導体チップとすることで逆阻止型の半導体装置を形成する。

(もっと読む)

エピレス基板における分離型の相補型MOS装置

【課題】高い実装密度を得ることが可能な半導体装置の製造プロセスを提供する。

【解決手段】半導体装置を電気的に分離するための構造は、エピタキシャル層を含まない半導体基板240内にドーパントを打込むことにより形成される。この打込みに続き、極めて限られた熱収支に上記構造を晒すことでドーパントが顕著に拡散しないようにする。その結果として、上記分離構造の寸法が制限かつ規定され、こうして、エピタキシャル層を成長させる工程とドーパントを拡散させる工程とを含む従来のプロセスを用いて得られるよりも高い実装密度を得ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】容易なプロセスにより単結晶半導体層を形成したSOI構造のMISFETの提供

【解決手段】半導体基板1上に、第1の絶縁膜2を介して、一部に空孔4を有する第2の絶縁膜3が設けられ、空孔4上及び第2の絶縁膜3の一部上に島状に絶縁分離された半導体層6が設けられ、半導体層6上にゲート酸化膜12を介して、空孔4直上に空孔4の幅以下のゲート電極13が設けられ、半導体層6には、ゲート電極13に自己整合して低濃度のソースドレイン領域(9,10)が、ゲート電極13の側壁に設けられたサイドウォール14に自己整合して高濃度のソースドレイン領域(8,11)がそれぞれ設けられ、ゲート電極13(配線図示せず)及び高濃度のソースドレイン領域(8,11)にはバリアメタル17を有する導電プラグ18を介してバリアメタル20を有する配線21が接続されているMISFET。

(もっと読む)

半導体装置

【課題】支持基板に接地電極を備えることなく、第1、第2素子形成領域間でノイズが伝播することを抑制することができる半導体装置を提供する。

【解決手段】支持基板10を、第1導電型領域10aと第2導電型領域10bとを有し、第1素子形成領域20にノイズが印加されてノイズが伝播されたときの当該ノイズの伝播経路中に、第1、第2導電型領域10a、10bで構成されるPNP接合またはNPN接合を有するものとする。このような半導体装置では、PNP接合またはNPN接合の間に構成される空乏層により、第1、第2素子形成領域20、30の間でノイズが伝播することを抑制することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ分離されたSOI基板にIGBTとその制御回路等が形成される半導体装置において、IGBTの高耐圧化及びターンオフ特性の改善等が必要になる。

【解決手段】ダミー半導体基板16にN型エピタキシャル層8を形成し、N型エピタキシャル層8にトレンチ30を形成し、トレンチ30側壁及びN型エピタキシャル層8表面にN型バッファ層7、次にP型埋め込みコレクタ層6を形成し、トレンチ30底面及びP+型埋め込みコレクタ層6上を埋め込み絶縁膜5で被覆する。埋め込み絶縁膜5上をポリシリコン膜3で被覆し、該ポリシリコン膜3と絶縁膜2を介してP型半導体基板1を貼り合わせた後、ダミー半導体基板16を除去し、略同一平面状に露出するトレンチ30底面の埋め込み絶縁膜5、P+型埋め込みコレクタ層6、N型バッファ層7、N型ドリフト層8a等を具備するSOI基板を形成する。該SOI基板にIGBT等を形成する。

(もっと読む)

半導体装置

【課題】第1、第2素子形成領域間でノイズが伝播することを抑制することができる半導体装置を提供することを目的とする。

【解決手段】第1、第2素子形成領域20、30に形成された半導体素子のうち、第1素子形成領域20に形成された半導体素子を外部機器と接続し、第1素子形成領域20と第2素子形成領域30との間に、第1導電型層60と、当該第1導電型層60に挟まれる第2導電型層61とを配置し、第1、第2導電型層60、61の間に、オフ時に半導体層12の表面から埋込絶縁膜11に達し、第1、第2素子形成領域20、30との間を仕切る空乏層63、64を構成する。

(もっと読む)

半導体集積回路装置

【課題】絶縁素子分離型のバイポーラトランジスタの放熱性を改善する。

【解決手段】薄い半導体層の第1のエリアに配置された第1のトランジスタと、薄い半導体層の第2のエリアに配置された第2のトランジスタで構成される回路部と、を備え、第1のトランジスタは、並列接続された複数のバイポーラトランジスタ素子を構成する複数の単位能動領域の配列全体を囲って配置された素子分離溝を含み、素子分離溝を能動領域から少なくとも1μm離間して設け、能動領域で生成される熱を単位能動領域を囲んで存在する半導体領域から外方に放熱させる構成を備えてなり、第2のトランジスタは、バイポーラトランジスタ動作を行う単位能動領域と、単位能動領域を取り囲んで形成され単位能動領域から1μm以下の位置に配置された素子分離溝を含む。

(もっと読む)

半導体装置

【課題】体格の増大が抑制された半導体装置を提供する。

【解決手段】絶縁分離トレンチによって半導体基板が複数の素子形成領域に区画され、各素子形成領域に少なくとも1つの電子素子が形成された半導体装置であって、半導体基板の厚さ方向に垂直な平面方向において、1本の絶縁分離トレンチを介して、2つの素子形成領域が互いに隣接するように、絶縁分離トレンチの平面方向に沿う形状が、格子状となっている。

(もっと読む)

ガードリング構造を有する半導体デバイス、ディスプレイドライバ回路、及びディスプレイ装置

【課題】ガードリング構造を有する半導体デバイス、ディスプレイドライバ回路、及びディスプレイ装置を提供する。

【解決手段】本発明による半導体デバイスは、第1導電型の半導体基板と、半導体基板に既定の深さを有して形成された2以上の第2導電型の第1ウェル領域と、第2導電型の第1ウェル領域の内に既定の深さを有して形成された少なくとも一つの第1導電型の第2ウェル領域と、第1ウェル領域の間に位置し、第1ウェル領域と既定の間隔だけ離隔して既定の深さを有して形成された第2導電型のガードリング領域と、を含み、ガードリング領域は、システムグラウンド電圧に連結される。

(もっと読む)

1 - 20 / 198

[ Back to top ]