Fターム[5F033HH29]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | シリサイド (1,618) | 高融点金属のシリサイド (1,006) | MoSi (62)

Fターム[5F033HH29]に分類される特許

1 - 20 / 62

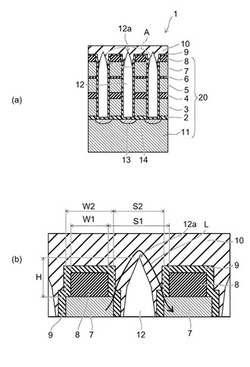

不揮発性半導体記憶装置

【課題】隣接する配線の間におけるリークを抑制することができる不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置1は、シリコンを含む基板11と、基板11の上に設けられた複数のメモリセルと、複数のメモリセルの上方に設けられた配線7と、配線7の上に設けられたリーク抑制層8と、前記リーク抑制層8の上方に設けられた層間絶縁膜10と、を備えている。そして、隣接するメモリセルの間、および、隣接する配線7の間には空隙12が形成され、リーク抑制層8の幅寸法は、配線7の幅寸法よりも短いこと、および、隣接するリーク抑制層8の間の寸法は、隣接する配線7の間の寸法よりも長いこと、の少なくともいずれかである。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の低抵抗化を図る。

【解決手段】本実施形態の半導体装置は、半導体基板10を覆う第1の層間絶縁膜上に設けられる配線60と、配線60の上面上に設けられるキャップ層68と、配線60と第2の層間絶縁膜との間に設けられるバリア膜62と、を含む。配線60は高融点導電層を含み、配線60の配線幅W1は、キャップ層68の幅W2よりも小さい。バリア膜62は、高融点導電層60が含む元素の化合物からなり、配線60を覆う層間絶縁膜69,70に起因する不純物が配線60内に拡散するのを抑制する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細配線を簡易に低抵抗化する。

【解決手段】実施形態に係わる半導体装置は、第1の方向に積み重ねられる第1乃至第3の半導体層3a,3b,3cを有し、第2の方向に延びるフィン型積層構造を有する。第1のレイヤーセレクトトランジスタTaは、第1のゲート電極10aを有し、第1の半導体層3aでノーマリオン状態である。第2のレイヤーセレクトトランジスタTbは、第2のゲート電極10bを有し、第2の半導体層3bでノーマリオン状態である。第3のレイヤーセレクトトランジスタTcは、第3のゲート電極10cを有し、第3の半導体層3cでノーマリオン状態である。第1の半導体層3aのうちの第1のゲート電極10aにより覆われた領域、第2の半導体層3bのうちの第2のゲート電極10bにより覆われた領域及び第3の半導体層3cのうちの第3のゲート電極10cにより覆われた領域は、それぞれ金属シリサイド化される。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】隣接するメモリセルゲート電極間に空隙を形成することで結合容量を抑制し、複数のコンタクト同士の短絡を防止しメモリの信頼性を向上する。

【解決手段】半導体記憶装置は、複数の選択ゲート電極間に形成され、選択ゲート電極に近接した側の側面と当該選択ゲート電極との第2間隔が第1間隔より広い層間絶縁膜11と、複数のメモリセルゲート電極間に空隙AGを備えるよう当該空隙AGの上部を被覆し、複数の選択ゲート電極間においては当該選択ゲート電極の側面および層間絶縁膜11の側面に沿って形成され、その上部に窪部Rを備えて形成されたエアギャップ形成膜12と、複数のメモリセルゲート電極上のエアギャップ形成膜12上に形成され、複数の選択ゲート電極間ではエアギャップ形成膜12の窪部Rの内側に埋込まれたリフィル膜13と、複数の素子領域に接触するように層間絶縁膜11に形成された複数のコンタクトCBa,CBbを備える。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】耐圧確保に有利な構造を提供する。

【解決手段】実施形態の半導体記憶装置は、基板上で所定方向に平行に延伸した複数の素子分離領域と、隣接する素子分離領域に挟まれた素子領域上の第1絶縁膜と、素子領域上の所定方向に間隔を空けて形成され、第1絶縁膜の上に順に積層された電荷蓄積層、第2絶縁膜、及び制御ゲート電極をそれぞれ有する複数のワードラインと、その両側に1つずつ配置され所定方向の幅がワードラインより大きい選択トランジスタと、ワードライン及び選択トランジスタの上面を覆う層間絶縁膜と、ワードライン間に位置し上部を層間絶縁膜に覆われた第1空洞部と、選択トランジスタのワードラインとは反対側の側壁部に形成され上部が層間絶縁膜で覆われた第2空洞部を備える。実施形態の半導体記憶装置は、互いに隣接する選択トランジスタ間の基板表面に酸化膜が形成され、その下の所定方向に垂直方向の断面が凸型形状になっている。

(もっと読む)

半導体素子の製造方法

【課題】本発明は、Si基板の表面にシリサイド層を形成しつつ、Si基板の裏面における低融点金属とSi基板のSiとの相互拡散を防止できる半導体素子の製造方法を提供することを目的とする。

【解決手段】本願の発明に係る半導体素子の製造方法は、Si基板の裏面に低融点金属を形成する工程と、該Si基板の表面に高融点金属層を形成する工程と、該高融点金属層の上にレーザ吸収層を形成する工程と、該レーザ吸収層にレーザ光を照射し、該低融点金属と該Si基板のSiとの相互拡散を防ぐように該低融点金属の温度を低く保ちつつ、該レーザ吸収層と該高融点金属層の界面、及び該高融点金属層と該Si基板の界面にシリサイド層を形成する工程と、該レーザ吸収層をエッチングする工程と、を備えたことを特徴とする。

(もっと読む)

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】周辺回路における回路動作の遅延を低減できる不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板11上に所定間隔を空けて形成され、ゲート絶縁膜1、浮遊ゲート電極2、ゲート間絶縁膜3、及び制御ゲート電極4をそれぞれ有する複数のメモリセルMCと、メモリセルMCの浮遊ゲート電極2の側面、ゲート間絶縁膜3の側面、及び制御ゲート電極4の側面に形成され、空隙を有する側壁絶縁膜18Bと、基板11上に形成され、ゲート絶縁膜1、第1ゲート電極2、ゲート間絶縁膜3、及び制御ゲート電極4を有する周辺トランジスタPTと、周辺トランジスタPTの第1ゲート電極2の側面、ゲート間絶縁膜3の側面、及び制御ゲート電極4の側面に形成され、空隙19Aを有する側壁絶縁膜18Aとを備える。基板11上の最も低い位置にある空隙19Aの上端は、ゲート間絶縁膜3より基板11上の低い位置にある。

(もっと読む)

半導体デバイス用基板洗浄液及び洗浄方法

【課題】基板表面を腐食することなく微粒子付着による汚染、有機物汚染及び金属汚染を同時に除去することができ、しかも水リンス性も良好で、短時間で基板表面を高清浄化することができる半導体デバイス用基板洗浄液を提供する。

【解決手段】

半導体デバイス製造における化学的機械的研磨工程の後に行われる、半導体デバイス用基板の洗浄工程に用いられる洗浄液であって、以下の成分(A)〜(D)を含有してなる半導体デバイス用基板洗浄液。

(A)有機酸

(B)スルホン酸型アニオン性界面活性剤

(C)ポリビニルピロリドン及びポリエチレンオキシド−ポリプロピレンオキシドブロック共重合体から選ばれる少なくとも1種の高分子凝集剤

(D)水

(もっと読む)

表示装置、電子機器

【課題】アクティブマトリクス型の液晶表示装置の画面の大面積化を可能とするゲート電

極とゲート配線を提供することを第1の課題とする。

【解決手段】同一基板上に表示領域と、表示領域の周辺に設けられた駆動回路と、を有し

、表示領域は、第1の薄膜トランジスタを有し、駆動回路は、第2の薄膜トランジスタを

有し、第1の薄膜トランジスタと第2の薄膜トランジスタは、リンがドープされたシリコ

ンでなるゲート電極を有し、ゲート電極は、チャネル形成領域の外側に設けられた接続部

でアルミニウムまたは銅を主成分とする層とタンタル、タングステン、チタン、モリブデ

ンから選ばれた少なくとも1種を主成分とする層とを有する配線と電気的に接続する。

(もっと読む)

ドライエッチング剤

【課題】経済性を備え、地球環境に対する影響が小さく、かつ必要とされる性能を有するドライエッチング剤を提供する。

【解決手段】(A)3,3,3−トリフルオロプロピンと、(B)O2、O3、CO、CO2、COCl2、及びCOF2からなる群より選ばれる少なくとも1種のガスを含むドライエッチング剤を用いることにより、酸化物、窒化物、炭化物、フッ化物、オキシフッ化物、シリサイド及びこれらの合金等を好適にエッチングできる。ドライエッチング剤は、大気中での分解性があり、地球温暖化への寄与もCF4やCF3H等のPFC類やHFC類より格段に低く、環境への負荷が低い。さらに、第二のガスとして、含酸素ガス、含ハロゲンガス、あるいは第三のガスとして不活性ガスと混合することで、飛躍的にプロセスウインドウを広げることができ、特殊な基板の励起操作等なしに高アスペクト比が要求される加工にも対応できる。

(もっと読む)

スパッタリング用ターゲットおよび半導体装置の製造方法

【課題】スパッタリング用ターゲットから垂直方向に叩き出されるターゲット原子の個数を増大させる。

【解決手段】薄膜形成に用いられるターゲット原子Pから構成されたターゲット5において、ターゲット5から斜め方向に叩き出されたターゲット原子Pを側壁に衝突させることでターゲット原子Pがターゲット5から放出されるのを遮る凹部5aを表面に形成する。

(もっと読む)

金属の付着

システム及び方法が、電圧切り換え可能な誘電体材料に1つ以上の材料を付着させることを含む。特定の態様では、電圧切り換え可能な誘電体材料が、導電バックプレーン上に配置される。いくつかの実施形態では、電圧切り換え可能な誘電体材料が、付着に関する特性電圧が相違する複数の領域を含む。いくつかの実施形態は、マスキングを含み、取り除くことが可能なコンタクトマスクの使用を含むことができる。特定の実施形態は、電気グラフトを含む。いくつかの実施形態は、2つの層の間に配置される中間層を含む。 (もっと読む)

半導体装置の作製方法

【課題】電界メッキ法やCMP法を使わないことで製造コストを落として配線を形成する半導体装置の作製方法を提供する。

【解決手段】絶縁膜を形成する工程と、絶縁膜上にマスクを形成する工程と、選択的にエッチングして絶縁膜に開口部を形成する工程と、マスク上および開口部に第1導電膜を形成する工程と、液滴吐出法により開口部の第1導電膜上に導電材料を含む液滴を滴下する工程と、レーザー光を選択的に照射して導電材料を加熱して第2導電層を形成する工程と、マスク上および第2導電層上に第3導電膜を形成する工程と、マスクを除去すると同時にマスク上に形成された第1導電膜および第3導電膜を除去し、第1導電層および第3導電層を形成する工程とを有する半導体装置の作製方法を提供する。

(もっと読む)

多層配線基板及びそれを備えた半導体装置

【課題】遮光領域を抑制することにより、開口率の低下を防止するとともに、製造工程を簡素化することができる多層配線基板及びそれを備えた半導体装置を提供することを目的とする。

【解決手段】TFT基板1は、第1コンタクトホール11が形成された第1絶縁膜8と、第1絶縁膜8の表面及び第1コンタクトホール11の表面に形成された第1配線層14と、第2コンタクトホール15が形成された第2絶縁膜9と、第2絶縁膜9上に積層されるとともに、第2絶縁膜9の表面及び第2コンタクトホール15の表面に形成され、第1配線層14と導通された第2配線層16とを備えている。そして、第1及び第2コンタクトホール11,15が、TFT基板1の上下方向Xにおいて重なった状態で直線的に配置され、第1コンタクトホール11において、第1配線層14上に絶縁性樹脂25が充填されている。

(もっと読む)

半導体装置

【課題】コンタクト抵抗を低減し、動作信頼性を向上出来る半導体装置を提供すること。

【解決手段】半導体基板10上に形成された、第1導電型の第1MOSトランジスタ5と、前記半導体基板10上に形成された、第2導電型の複数の第2MOSトランジスタ6と、円形の平面形状を有する第1コンタクトプラグCP10−1と、楕円形の平面形状を有する第2コンタクトプラグCP10−2とを具備し、前記第2コンタクトプラグCP10−2は、前記第2MOSトランジスタ6のいずれか6−1の、ソースまたはドレイン上に形成され、前記第1コンタクトプラグCP10−1は、残りの前記第2MOSトランジスタ6−2、及び前記第1MOSトランジスタ5の、ソースまたはドレイン上に形成される。

(もっと読む)

半導体装置の製造方法

【課題】デュアルダマシン溝(接続孔)内への異物の残留を回避し、配線接続の信頼性および半導体装置性能の向上を図る。

【解決手段】第4配線層の配線33上に絶縁膜34〜38を順次形成し(絶縁膜34,36,38はシリコン窒化膜からなる。絶縁膜35,37はシリコン酸化膜からなる)、絶縁膜38に溝パターン40a、40bをフォトリソグラフィを用いて転写する。絶縁膜38の溝パターン40を埋め込む反射防止膜41を形成し、さらに孔パターン43を有するレジスト膜42を形成する。レジスト膜42の存在下でエッチング処理を施し、絶縁膜38,37,36および絶縁膜35の一部に孔パターン43を転写する。その後、レジスト膜42,反射防止膜41を除去し、絶縁膜38をマスクとして溝パターン40を絶縁膜37に、孔パターン43を絶縁膜35に転写する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】簡易なプロセスで抵抗層上の所定領域を選択的にサリサイド化することができ、かつ、抵抗の占有面積を小さくすることができる半導体装置の製造方法を提供する。

【解決手段】第1素子形成領域1と第2素子形成領域2とを有し、第2素子形成領域2に第1抵抗層30を形成し、その上に第1絶縁層40と導電層を形成し、第2素子形成領域2の導電層を高抵抗化し、導電層の一部を除去して、第1素子形成領域1にゲート電極50を形成すると同時に、第2素子形成領域2に第2抵抗層52を形成し、第2素子形成領域2の第2抵抗層52の上方に第2絶縁層90を形成し、第1素子形成領域1の半導体基板10に不純物を注入して、ソース領域およびドレイン領域70a,70bを形成し、ソース領域およびドレイン領域70a,70bの上と、第2素子形成領域2の第1抵抗層30および第2抵抗層52の上と、にシリサイド層80を形成する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】外部ストレスによる亀裂などの破損による形状不良や特性不良などの半導体装置の不良を低減することを目的の一とする。よって、信頼性の高い半導体装置を提供することを目的の一とする。また、作製工程中においても上記不良を低減することで半導体装置の製造歩留まりを向上させることを目的の一とする。

【解決手段】一対の第1の耐衝撃層及び第2の耐衝撃層に挟持された半導体集積回路において、半導体集積回路と第2の耐衝撃層との間に衝撃拡散層を有する。外部ストレスに対する耐衝撃層と、その衝撃を拡散する衝撃拡散層とを設けることで、半導体集積回路の単位面積あたりに加えられる力を軽減し、半導体集積回路を保護する。衝撃拡散層は弾性率が低く、破断係数が高い方が好ましい。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極形成時に発生する微小パーティクルに起因するゲート電極とコンタクトのショートを防止する。

【解決手段】半導体基板上に配置されたゲート電極膜に対してエッチングすることにより複数のゲート電極が形成される。第一の窒化膜が形成される。第一の窒化膜をエッチバックすることにより複数のゲート電極の間の領域の半導体基板が露出する。熱酸化により、ゲート電極の間の領域に形成されたゲート電極の一部が熱酸化膜に置換される。ゲート電極の間の領域にコンタクトが形成される。微小パーティクルによりエッチング時にゲート電極膜の端部に残りが発生しても、その残りを増速酸化膜に転化することができ、ショートを防止することができる。

(もっと読む)

1 - 20 / 62

[ Back to top ]