Fターム[5F033MM21]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 配線の平面形状 (698)

Fターム[5F033MM21]の下位に属するFターム

スリットを有するもの (119)

凹凸を有するもの (91)

Fターム[5F033MM21]に分類される特許

481 - 488 / 488

可撓性基板上に作られた電子回路に関する新規な伝導体構造

可撓性基板(21)上に形成された可撓性伝導体。ある実施形態では、かかる基板は半導体基板である。デバイスは、周期的構造のアイランド(14)、及び、前記周期的構造のアイランドに添付した直列の繰り返し構造特性(18)を有する少なくとも1つの伝導体(10)を有する。伝導体の構造特性は、基板が曲がったとき、伝導体を破壊するのではなく伝導体を伸縮させるように適合される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

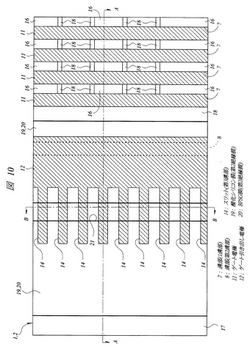

【課題】 寄生容量の増加を抑制しつつ、所望のゲート耐圧を有するパワーMISFETを製造できる技術を提供する。

【解決手段】 基板上に多結晶シリコン膜を堆積し、その多結晶シリコン膜で溝部7、8を埋め込んだ後、その多結晶シリコン膜をパターニングすることにより、活性セル領域においては溝部7内にてゲート電極11を形成し、ゲート配線領域においては溝部8内を埋め込み、一部が溝部8内から連続して溝部8の外部に延在し、ゲート電極11と電気的に接続するゲート引き出し電極12を形成し、溝部8外のゲート引き出し電極12には、ゲート引き出し電極12の端部から延在するスリット14を形成する。その後、基板上に酸化シリコン膜19およびBPSG膜20を堆積する。

(もっと読む)

アクティブマトリクス基板、その画素欠陥修正方法及び製造方法

【課題】異物や膜残り等によるソース電極とドレイン電極との短絡、ドレイン電極やドレイン引出配線の断線及びTFT動作不良等による画素欠陥に対して、開口率を減少させることなく、点欠陥となる画素を容易かつ確実に修正することができ、液晶表示装置の歩留りを向上させることができるアクティブマトリクス基板を提供する。

【解決手段】基板上に、複数本の走査信号線及びデータ信号線と、信号線の交点に設けられ、ゲート電極が走査信号線に接続され、ソース電極がデータ信号線に接続された薄膜トランジスタと、上記薄膜トランジスタのドレイン電極又はドレイン引出配線に接続された画素電極とを備えるアクティブマトリクス基板であって、上記アクティブマトリクス基板は、データ信号線が少なくとも部分的に複線化された構造を有し、かつ修正用接続電極を備えるアクティブマトリクス基板である。

(もっと読む)

金属メッシュ構造を含む半導体集積回路

集積回路に使用する金属メッシュ構造が説明される。一実施形態では、半導体集積回路は、例えば1つまたは複数の能動半導体デバイスを有するデバイス層を含む第1領域を備える。回路は回路配線を含む金属化層含むことがある第2領域も備える。回路は更に第1領域と第2領域の間に挿入された金属メッシュ層を含み、金属メッシュ層は、別の金属化層の少なくとも一部分の上に実装されることがある。  (もっと読む)

(もっと読む)

少なくとも1つの層の構造化方法並びに層から成る構造を備えた電気素子

本発明は、少なくとも1つの構造化された層(10A)を作成するための方法を提供し、その際第1の構造(20A)および第2の構造(20B)を有するマスク構造(20)が基板(5)上に存在している層(10)に生成される。このマスク構造(20)を通して第1の構造(20A)は等方性構造化法を用いてかつ第2の構造(20B)は異方性構造化法を用いて層(10)に移される。本発明の方法により、少なくとも1つの層に唯一のマスク構造を用いて2つの構造(20A,20B)を生成することが可能になる。  (もっと読む)

(もっと読む)

補強された内部接続メタライゼーションを有するワイヤボンディングされた半導体部品

ドープされたシリコン基板製の半導体チップ2を含む半導体部品であって、前記チップは、半導体デバイスの中へドープされて構造化され、そして、コンタクトウインドウ中に内部接続メタライゼーション7を含み、前記半導体チップの前記内部接続メタライゼーションは、ワイヤボンド接続9によって、各外部接続メタライゼーションと接続され、前記内部接続メタライゼーションは、前記ドープされたシリコン基板上に開放格子構造体を有する補強システム8を含むことを特徴とする半導体部品。  (もっと読む)

(もっと読む)

フリップチップFET素子

【課題】電力素子のオン状態抵抗、放熱特性、インダクタンスを改善する。

【解決手段】半導体素子は導電パッド領域26,36を含み、各々の導電パッド領域は複数の金属トレースに電気的に接続される。複数の金属トレースは各々が順番に拡散に接続される。はんだバンプやビアなどの導電接点素子は各々の導電パッド領域に取り付けられ、導体素子が第1のピッチを有する反復パターンに配列され得る。半導体素子は平行移動トレース50,60も含み、各々の平行移動トレースは2つ以上の導電接点素子に電気的に接続され得る。各々の平行移動トレースはそこに取り付けられる相互接続素子を有し得る。相互接続素子は第1のピッチより実質的に大きい第2のピッチを有する反復パターンに配列され得る。

(もっと読む)

配線構造および基板の製造方法ならびに液晶表示装置およびその製造方法

【課題】 短絡や断線を回避しながら、基板の接続配線の抵抗の均一化を図る。

【解決手段】 基板の各信号配線3と素子側端子8とを接続する接続配線7を、それぞれ所定の線幅を有する複数の接続部である第1の区間7a、第2の区間7bから構成し、該複数の接続部の膜厚を調整したり、第1の区間7aに積層配線19を設けて多層構造とすることにより、各接続配線7で全抵抗が略同じになるように構成する。これにより、接続配線7の最大線幅と最小線幅の差を約2倍程度に抑えることができるため、太い接続配線7における短絡や、細い接続配線7における断線を回避しながら、各接続配線7の抵抗の均一化を図ることができる。

(もっと読む)

481 - 488 / 488

[ Back to top ]