Fターム[5F033MM23]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 配線の平面形状 (698) | 凹凸を有するもの (91)

Fターム[5F033MM23]に分類される特許

1 - 20 / 91

半導体装置及び半導体装置の製造方法

【課題】情報が読み取られることを防止する半導体装置を提供する。

【解決手段】本明細書に開示する半導体装置10は、コンタクト15aを有する第2絶縁層15と、コンタクト17aを有する第3絶縁層17と、第2絶縁層15と第3絶縁層17との間に配置された第2配線層16と、を備え、コンタクト15aとコンタクト17aとの間の第2配線層16の部分には配線が配置されておらず、コンタクト15aとコンタクト17aとの間の距離は、コンタクト15a又はコンタクト17aと、第2絶縁層15及び第3絶縁層17及び第2配線層16内の他のコンタクト又は配線との間の距離よりも短い。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ゲート電極とコンタクトとの間の短絡の発生を抑制する。

【解決手段】基板(2)に設けられた第1拡散領域(3)と、基板(2)に設けられた第2拡散領域(3)と、第1拡散領域(3)に接続された第1コンタクト(11)と、第2拡散領域(3)に接続された第2コンタクト(11)と、第1拡散領域(3)と第2拡散領域(3)の間に設けられたチャネル領域と、ゲート絶縁膜(6)を介してチャネル領域の上に設けられたゲート電極(5)とを具備する半導体装置を構成する。ゲート電極(5)は、第1コンタクト(11)と第2コンタクト(11)とに挟まれた第1領域(A−A’)と、第1領域と異なる第2領域(B−B’)とを備える。第1領域(A−A’)は、第1コンタクト側の第1側面と、第2コンタクト側の第2側面とを含む。第1側面は、第1コンタクトから離れる方向に傾斜する。第2側面は、第2コンタクトから離れる方向に傾斜する。

(もっと読む)

半導体装置

【課題】占有面積の小さな直線状の電気ヒューズを有する半導体装置を提供する。

【解決手段】複数の突出部10fは、電気ヒューズ部10aの中央位置からずれた位置、より具体的には、ビア10dに近くかつビア10eから遠い位置に設けられている。また、複数の突出部20fは、電気ヒューズ部20aの中央位置からずれた位置、より具体的には、ビア20dから遠くかつビア20eに近い位置に設けられている。つまり、突出部10fおよび突出部20fは、ジグザグ状に配置されている。

(もっと読む)

駆動装置、表示装置、駆動装置複合物及び集積回路装置

【課題】 小型かつ簡素な構成の駆動装置や、当該駆動装置を備える表示装置、複数の当該駆動装置から成る駆動装置複合物、当該駆動装置に備えられる集積回路装置を提供する。

【解決手段】 駆動装置1は、表示部に出力する出力信号を生成する集積回路部10と、集積回路部10と電気的に接続する配線部20と、を備える。集積回路部10は、出力信号を生成する複数の出力回路を備える。配線部20は、一端部が出力回路に電気的に接続する複数の出力配線24−1〜24−3と、出力配線24−1〜24−3の他端部に電気的に接続するとともに駆動装置1の外部に出力信号を出力する複数の出力部23−1〜23−3と、を備える。出力部23−1〜23−3は、所定方向(X方向)に沿って配置され、複数の出力部23−1〜23−3で出力部群G1〜G3が構成される。

(もっと読む)

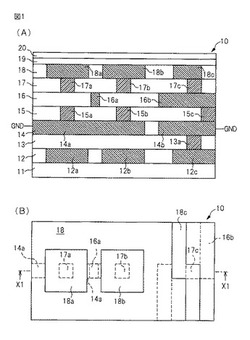

キャパシタおよび半導体装置

【課題】キャパシタの電極として機能する配線の延伸方向への電流供給を容易とすること。

【解決手段】第1金属層12と、前記第1金属層の膜厚方向に離間して設けられ、第1方向および前記第1方向に交差する第2方向に配列された複数の孔36を備えた第2金属層14と、前記第2金属層の膜厚方向で前記第1金属層とは反対側に離間して設けられ、前記第1方向および前記第2方向とは異なる方向に延伸し、第1配線と第2配線とが交互に設けられた複数の第1配線16aおよび複数の第2配線16bと、前記複数の第1配線と前記複数の第2配線との間に設けられた誘電体膜26と、前記複数の第1配線を、それぞれ前記複数の孔を通過し前記第1金属層に電気的に接続する複数の第1ビア配線32と、前記複数の第2配線を、それぞれ前記第2金属層に電気的に接続する複数の第2ビア配線34と、を具備するキャパシタ。

(もっと読む)

集積回路装置及びその製造方法

【課題】ビアの形成が容易で抵抗が低い集積回路装置及びその製造方法を提供する。

【解決手段】相互に平行に配列された複数本の配線14a、14bと、各配線に接続されたビア16とを備える。配線におけるビアが接続された部分には、配列の方向に延出した凸部31が形成されており、配線における凸部が形成された部分から離隔した部分には、配列の方向に後退した凹部32が形成されている。隣り合う2本の配線において、一方の配線に形成された凸部と他方の配線に形成された凹部とは相互に対向している。各配線において、凹部が形成された部分はその両側の部分から切込33で分断されており、凸部が形成された部分からも分断されている。

(もっと読む)

半導体装置

【課題】半導体装置におけるSM不良による信頼性や歩留りの低下を抑えることが可能な半導体装置を提供する。

【解決手段】半導体装置においては、第1の配線と、第1の配線と接続され、第1の配線より細幅の第2の配線と、一方の端部が、第1の配線と第2の配線の接続部の近傍で、第1の配線と接続され、他方の端部より局所的に細幅となる中間部を有する犠牲的配線と、を備える。

(もっと読む)

半導体ウェハ及び半導体装置

【課題】ウェハを個々のチップに分割する際のダイシングによってチップ側面に生じるクラックがチップ領域内に伝播することを防止し、それにより半導体装置の品質を向上させることを目的とする。

【解決手段】少なくとも2つのシールリング121、122に凹凸を形成し、シールリング121、122間で隣り合う凹凸の突出方向を逆向きにすると共に、突出先端部を近接させることにより、ダイシング等により発生したチップ領域120方向への外力をスムーズにチップ外周部へと逃がすことができるため、半導体ウェハ101を個々のチップに分割する際のダイシングによってチップ側面に生じるクラックがチップ領域120内に伝播することを防止し、それにより半導体装置の品質を向上させることができる。

(もっと読む)

配線構造、半導体装置及び不良箇所特定方法

【課題】不良箇所の特定の容易化を実現し得る配線構造、半導体装置及び不良箇所特定方法を提供することにある。

【解決手段】基板10上に形成された第1の配線14と、第1の配線上に形成され、第1の領域において第1の配線と重なり合う第2の配線20とを有し、第1の配線は、第1の領域外に突出する第1のタブ部16を有している。

(もっと読む)

固定用構造および嵌合構造

【課題】チップの縁領域は、膨張係数が異なることによって、温度サイクル中に、TC応力とも称される特定の負荷を受けることが多い。これらの縁領域は特にTC応力を受け易いため、同領域内において様々な不良が生じる可能性がある。これによって、実際のデバイスにおける信頼性のリスクが増大する可能性がある。

【解決手段】半導体デバイスの金属構造210のための固定用構造200は、オーバーハング形状の側壁230を少なくとも1つ含んだ固定用凹部構造220を含んでいる。上記金属構造210は、少なくとも部分的に上記固定用凹部構造220内に配置されている。

(もっと読む)

コプレーナ線路のエアブリッジ構造

【課題】コプレーナ線路の信号線路とエアブリッジとの交差容量の影響を抑制しつつ、複数のエアブリッジを容易に使用できるようにする。

【解決手段】エアブリッジ構造100のうち、下層配線層8に、接地線路2A,2Bのうち信号線路1を挟んで互いに対向する位置を切り欠いて形成した空孔領域12A,12Bをそれぞれ設けるとともに、上層配線層7に、空孔領域12Aの上部位置に下層配線層8の接地線路2Aと電気的に接続された上層接地電極13Aと、空孔領域12Bの上部位置に下層配線層8の接地線路2Bと電気的に接続された上層接地電極13Bとを設け、エアブリッジ3で、上層接地電極13A,13Bを介して接地線路2A,2B間を電気的に接続する。

(もっと読む)

半導体素子及びその半導体素子のパターン形成方法

【課題】 フォトリソグラフィ工程の解像限界内で、具現可能なサイズのパターンを利用して超微細な幅及び間隔を持つ高密度パターンを形成できる配置構造を持つ半導体素子及びその半導体素子パターン形成方法を提供する。

【解決手段】 半導体素子は、コネクション領域に隣接するメモリセル領域を含む基板、メモリセル領域からコネクション領域まで第1方向に延びて配され、第1ライン幅及び第1ライン間隔を持つ複数の第1導電ライン、第1導電ラインそれぞれに連結されるように配され、第2ライン幅及び第2ライン間隔を持つ複数の第2導電ライン、コネクション領域に配され、第1導電ラインに電気的に連結された複数のパッド、を備える。半導体素子上のパターン形成方法は、微細ライン幅及び間隔を提供するために2段階のスペーサ形成工程を含むことができる。

(もっと読む)

半導体装置およびその製造方法

【課題】パッド電極に荷重または衝撃力が加わっても、周囲の絶縁膜にクラックが発生しにくい構造の半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、平面形状が、略円形、略楕円形、少なくとも1つの内角が90°より大きい略多角形、および、少なくとも1つの角部に面取りや丸みをつけた略多角形、ならびに、これらの少なくとも一部分を含む形状の組合せからなる群から選ばれた平面形状となるような凹部を形成する凹部形成工程と、前記凹部の内面に少なくとも一部を被覆する下敷膜を形成する下敷膜形成工程と、絶縁膜で覆われた前記凹部に導電性の電極材質を埋め込むパッド部形成工程とを含み、前記凹部形成工程は、第1の凹部を形成する工程と、前記第1の凹部の一部分においてさらに深く凹む第2の凹部を形成する工程とを含む。

(もっと読む)

半導体集積回路及びその製造方法

【課題】検査時におけるプロービングの機械的な力学的ストレスや、組立のワイヤ・ボンディングによる機械的な力学的ストレスによって発生する応力を緩和できる構成を有する半導体集積回路を提供する。

【解決手段】半導体集積回路は、半導体基板上(100)に形成されたパワー・トランジスタ(100A)と、パワー・トランジスタ(100A)の直上に形成され、パワー・トランジスタの第1の電極及び第2の電極として機能する複数の第1の金属パターン及び複数の第2の金属パターンと、複数の第1の金属パターンと電気的に接続する第1のバス(140)と、第2の金属パターンと電気的に接続する第2のバス(150)と、第1のバス(140)及び第2のバス(150)に1つづつ設けられたコンタクト・パッド(304)とを備え、第1のバス(140)及び第2のバス(150)の各々には、少なくとも1つのスリット(10a)が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】配線とコンタクトプラグの短絡を効果的に防止する。

【解決手段】半導体装置の製造方法は、隣り合う配線の間に位置する層間絶縁膜内に、配線が露出した第1のコンタクトホールを含む複数のコンタクトホールを形成する。次に、(i)配線の露出した側面が、第1のコンタクトホールの第1の絶縁膜から構成される内壁側面と実質的に同一面となるか、又は(ii)第1のコンタクトホールの内壁側面において配線の露出した側面が窪んだ凹形状が形成されるように、露出した前記配線の一部を除去する。この後、コンタクトホールの内壁側面上にサイドウォール膜を形成後、コンタクトホール内に導電材料を充填することによりコンタクトプラグを形成する。

(もっと読む)

半導体集積回路

【課題】少なくともロジック回路ブロックを含む半導体集積回路において、半導体集積回路の電源用パッドとロジック回路ブロックの電源ラインとを接続する電源配線、及び/又は、半導体集積回路のグランド用パッドとロジック回路ブロックのグランドラインとを接続するグランド配線の抵抗値を下げる。

【解決手段】この半導体集積回路は、半導体基板と、半導体基板上にそれぞれの層間絶縁膜を介して形成され、半導体基板に形成された複数のトランジスタに接続されて複数のトランジスタと共に少なくともロジック回路ブロックを構成する複数の配線層と、複数の配線層が形成された半導体基板上に層間絶縁膜を介して形成され、複数の配線層における最大膜厚の5倍〜20倍の膜厚を有する最上層の配線層とを具備する。

(もっと読む)

半導体装置

【課題】デュアルダマシン構造の多層配線構造を有する半導体装置において、コンタクトのストレスマイグレーション耐性を向上させる。

【解決手段】デュアルダマシン構造を有する上層導体パターン47Aは延出部47Bに設けられたビアプラグ47Cを介して下層配線パターン43Aと接続している。この接続部でのストレスマイグレーションによる接続不良を防止するため延出部47Bより先端部の領域に下層配線層のダミーCuパターン43Bとダミービアプラグ47Dで接続する構造を追加する。ストレスマイグレーションは先端部の下層配線層のダミーCuパターン43Bとダミービアプラグ47Dの接続部で発生し、ビアプラグ47Cと下層配線パターン43Aの接続部ではストレスマイグレーションの発生は防止される。

(もっと読む)

半導体装置

【課題】ワイヤボンディング接続されるパッケージに搭載される場合のワイヤ長を短くできる半導体装置を提供する。

【解決手段】本発明に係る半導体装置100は、シリコン基板103の内部素子領域153に形成された複数の素子と、シリコン基板103上に形成される配線層120と、配線層120を貫通し、内部素子領域153を囲む環状のシールリング101と、内部素子領域153の上方、かつ、配線層120上に形成され、複数の素子に含まれる第1素子と接続されるパッド102と、シールリング101上に形成され、当該シールリング101と接続されたパッド102aとを備える。また、シールリング101は、複数の素子に含まれる第2素子と接続されている。

(もっと読む)

半導体記憶装置

【課題】層間接続により生ずるチップ面積の増大を抑制し、コスト削減を実現する半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、前記半導体基板上に前記半導体基板と垂直方向にそれぞれ複数層形成された互いに交差する複数の第1及び第2の配線、並びにこれら第1及び第2の配線の各交差部に接続された複数のメモリセルを有するセルアレイブロックと、前記セルアレイブロックの第n層目(nは自然数)の第1の配線と前記第n層目の第1の配線以外の第1の配線、前記半導体基板、又は他の金属配線とを接続する前記セルアレイブロックの積層方向に延びる第1のビア配線とを備える。前記第1のビア配線は、前記セルアレイブロックの積層方向と直交する断面が楕円形状であり、この断面の長径方向が前記第1の配線方向に対し垂直であることを特徴とする。

(もっと読む)

半導体装置の製造方法及びマスク

【課題】樹脂製のバンプコアの上に導電膜を形成したバンプを有する半導体装置の歩留まりを高くしつつ、バンプピッチを狭くする。

【解決手段】保護絶縁膜120上に感光性樹脂膜210を形成する。次いで、感光性樹脂膜210を露光及び現像することにより、保護絶縁膜120上に、第1の直線に沿って複数のバンプコアを形成する。次いで、複数のバンプコア上、複数の電極パッド130上、及び保護絶縁膜120上に導電膜を選択的に形成することにより、複数のバンプ、及び複数のバンプそれぞれをいずれかの電極パッド130に接続する複数の配線を形成する。そして複数のバンプコアを形成する工程において、多階調マスク50を使用して感光性樹脂膜210を1回のみ露光することにより、バンプコアの側面のうち配線に面する領域を、第1の直線と交わる領域より傾斜を緩やかにする。

(もっと読む)

1 - 20 / 91

[ Back to top ]