Fターム[5F033MM22]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 配線の平面形状 (698) | スリットを有するもの (119)

Fターム[5F033MM22]に分類される特許

1 - 20 / 119

半導体装置およびその製造方法

半導体集積回路装置

【課題】銅埋め込み配線を主要な配線層とする半導体集積回路装置に於いても、通常、ワイヤボンディング特性を確保するために、最上層配線層をアルミニウム系パッド層とすることが多い。このアルミニウム系パッド層は、一般に、配線層(電源配線、信号配線等の一般相互接続配線)としても使用されている。しかし、このような一般相互接続配線は、配線長が比較的長いためアンテナ効果により、プラズマ処理時にデバイスにダメージが入り易い等のデメリットがある。

【解決手段】本願発明は、メタル多層配線系が、下層の埋め込み型多層配線層と上層の非埋め込み型アルミニウム系パッドメタル層を有する半導体集積回路装置に於いて、前記非埋め込み型アルミニウム系パッドメタル層は、実質的に電源リング配線を有しないものである。

(もっと読む)

半導体装置

【課題】アンダーバリアメタルに起因する応力集中を緩和し、トランジスタの特性の変動を抑制することができるパッド電極構造を備える半導体装置を得られるようにする。

【解決手段】半導体装置は、半導体基板1の上に形成された電極パッド6と、電極パッド6の上に形成され、且つ、電極パッド6の一部が露出するような第1開口部を有する第1絶縁膜7と、第1絶縁膜の上に形成され、且つ、第1開口部における少なくとも一部が露出するような第2開口部を有する第2絶縁膜8と、第2絶縁膜8及び電極パッド6の上に形成されたアンダーバリアメタル10とを備えている。アンダーバリアメタル10は、第2絶縁膜8の表面における第2開口部の外側である第1領域と電極パッド6の表面における第2開口部の内側である第2領域とにより挟まれる第3領域により分離されている。

(もっと読む)

半導体装置

【課題】半導体装置において、少なくとも容量素子とトランジスタとを有する回路要素が占める面積を小さくする。

【解決手段】第1のトランジスタと第2のトランジスタと容量素子とを有する半導体装置において、第2のトランジスタよりも上方に第1のトランジスタ及び容量素子を配置する。そして、第1のトランジスタのソース又はドレインの一方と、容量素子の一方の電極とを兼ねる共通電極を設ける。さらに、容量素子の他方の電極を共通電極よりも上方に配置する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型トランジスタの特性にばらつきが生じることを抑制する。

【解決手段】半導体基板100には縦型MOSトランジスタ20が形成されている。半導体基板100の表面上には、第1層間絶縁膜300及び第1ソース配線312が形成されている。第1ソース配線312は、第1層間絶縁膜300上に形成されており、平面視で縦型MOSトランジスタ20と重なっている。第1層間絶縁膜300にはコンタクト302が埋め込まれている。コンタクト302は、縦型MOSトランジスタ20のn型ソース層140と第1ソース配線312とを接続している。そして第1ソース配線312には、複数の開口316が形成されている。

(もっと読む)

半導体装置

【課題】 より信頼性の高い接合界面を有する半導体装置を提供する。

【解決手段】 半導体装置100を、第1半導体部と、第2半導体部とを備える構成とする。第1半導体部には、接合界面側の表面に形成されかつ第1の方向に延在する第1電極16を設ける。そして、第2半導体部には、接合界面で第1電極16と接合されかつ第1の方向と交差する第2の方向に延在する第2電極26を設ける。

(もっと読む)

半導体装置及びその製造方法並びに積層型半導体装置

【課題】貫通電極と直接に接続される配線の信頼性を向上できるようにする。

【解決手段】半導体装置100は、貫通孔1Aを有する半導体基板1と、半導体基板1の上に形成された第2層間絶縁膜7bと、第2層間絶縁膜7bに貫通孔1Aを覆うように形成された第1の外部接続用配線8a1と、第2層間絶縁膜7bの上に、第1の外部接続用配線8a1を覆うように形成された第3層間絶縁膜7cと、第3層間絶縁膜7cにおける第1の外部接続用配線8a1の上側部分に形成された第2の外部接続用配線8b1と、貫通孔1Aにおける少なくとも内壁面に形成されると共に、各外部接続用配線8a1、8b1とそれぞれ電気的に接続される貫通電極15Aとを備えている。第1の外部接続用配線8a1は、複数の孔部19aを有し、第2の外部接続用配線8b1は、第1の外部接続用配線8a1の孔部19aを覆うように形成されている。

(もっと読む)

キャパシタおよび半導体装置

【課題】キャパシタの電極として機能する配線の延伸方向への電流供給を容易とすること。

【解決手段】第1金属層12と、前記第1金属層の膜厚方向に離間して設けられ、第1方向および前記第1方向に交差する第2方向に配列された複数の孔36を備えた第2金属層14と、前記第2金属層の膜厚方向で前記第1金属層とは反対側に離間して設けられ、前記第1方向および前記第2方向とは異なる方向に延伸し、第1配線と第2配線とが交互に設けられた複数の第1配線16aおよび複数の第2配線16bと、前記複数の第1配線と前記複数の第2配線との間に設けられた誘電体膜26と、前記複数の第1配線を、それぞれ前記複数の孔を通過し前記第1金属層に電気的に接続する複数の第1ビア配線32と、前記複数の第2配線を、それぞれ前記第2金属層に電気的に接続する複数の第2ビア配線34と、を具備するキャパシタ。

(もっと読む)

集積回路装置及びその製造方法

【課題】ビアの形成が容易で抵抗が低い集積回路装置及びその製造方法を提供する。

【解決手段】相互に平行に配列された複数本の配線14a、14bと、各配線に接続されたビア16とを備える。配線におけるビアが接続された部分には、配列の方向に延出した凸部31が形成されており、配線における凸部が形成された部分から離隔した部分には、配列の方向に後退した凹部32が形成されている。隣り合う2本の配線において、一方の配線に形成された凸部と他方の配線に形成された凹部とは相互に対向している。各配線において、凹部が形成された部分はその両側の部分から切込33で分断されており、凸部が形成された部分からも分断されている。

(もっと読む)

半導体装置、電子デバイス及び電子デバイスの製造方法

【課題】対向するバンプ、パッド等を良好に接続し、接続部分の水平強度を高めるための半導体装置を提供する。

【解決手段】半導体基板2の上方に形成される第1絶縁膜15と、第1絶縁膜15内に形成される導電パターン19と、第1絶縁膜15上に形成される第2絶縁膜21と、第2絶縁膜21内に形成され、導電パターン19に接続されるビアプラグ24と、記ビアプラグ24の上に接続され、開口部25aを有する電極パッド25と、第2絶縁膜21内でビアプラグ24の周辺に形成される内部空間21aとを有し、電極パッド25上面及び開口部25a内には外部の突起状電極58が接続される。

(もっと読む)

半導体装置

【課題】半導体装置の特性を向上させる。

【解決手段】LDMOSと、LDMOSのソース領域と電気的に接続されるソースプラグP1Sと、ソースプラグP1S上に配置されるソース配線M1Sと、LDMOSのドレイン領域と電気的に接続されるドレインプラグP1Dと、ドレインプラグP1D上に配置されるドレイン配線M1Dと、を有する半導体装置のソースプラグP1Sの構成を工夫する。ドレインプラグP1Dは、Y方向に延在するライン状に配置され、ソースプラグP1Sは、Y方向に所定の間隔を置いて配置された複数の分割ソースプラグP1Sを有するように半導体装置を構成する。このように、ソースプラグP1Sを分割することにより、ソースプラグP1SとドレインプラグP1D等との対向面積が低減し、寄生容量の低減を図ることができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電極パッド部の安定した電気的接触を確保しつつ電極パッド部の面積を小さくすることができる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板の主表面上であって平面視において素子形成領域内およびダイシングライン領域内の少なくともいずれかに形成された半導体チップ用電極パッド部,TEG用電極パッド部PTとを備えている。半導体チップ用電極パッド部,TEG用電極パッド部PTは、外部と電気的に接続するための表面OSFを有し、かつ半導体チップ用電極パッド部,TEG用電極パッド部PTの辺SIDに対して斜めに傾斜した方向に延びた溝部THPを表面OSFに有している。

(もっと読む)

成膜装置

【課題】表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンを成膜できる成膜装置を提供すること。

【解決手段】下地を有した被処理体1を収容する処理室101と、処理ガス供給機構114と、加熱装置133と、排気機構132と、コントローラ150とを具備し、コントローラ150が、加熱した下地にアミノシラン系ガスを流し、下地の表面にシード層を形成する工程と、加熱した下地の表面のシード層にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層上にアモルファスシリコン膜を形成する工程とが実施されるように処理ガス供給機構114、加熱装置133及び排気機構132を制御し、シード層を形成する工程における下地の加熱温度及び処理時間を、アモルファスシリコン膜を形成する工程におけるそれらよりも低く及び短くする。

(もっと読む)

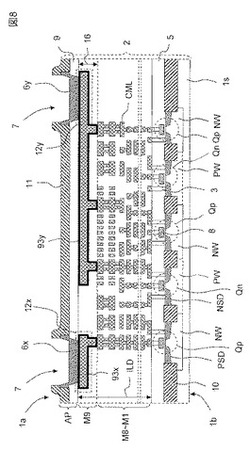

能動領域ボンディングの両立性のある高電流構造体

【課題】ボンディング・パッド下方に各回路を有する集積回路。

【解決手段】一実施例において、集積回路は基板と、最上部導電層と、1つ以上の中間導電層と、絶縁材料から成る各層と、各デバイスとを具備する。最上部導電層は少なくとも1個のボンディング・パッド及び比較的硬質の材料から成る副層を有する。1つ以上の中間導電層は最上部導電層及び基板の間に形成する。絶縁材料から成る各層は各導電層を分離する。更に、絶縁材料から成る各層のうちの1つの層は比較的硬質で、最上部導電層及びこの最上部導電層に最も近接した中間導電層の間に位置する。各デバイスは集積回路に形成する。また、最上部導電層に最も近接した少なくとも中間導電層は、ボンディング・パッド下方の各選択デバイスの機能的相互接続部に対して適合する。

(もっと読む)

半導体装置、半導体装置の検査方法、及び、半導体装置の製造方法

【課題】半導体装置の製造工程の増大を抑制しつつ、パッドの針跡を容易に確認できるようにする。

【解決手段】半導体装置は、半導体基板1と、半導体基板1上に形成された回路素子と、半導体基板1上に形成され、回路素子と電気的に接続されたパッド(接続パッド4)と、を有している。パッドは、平面視において、導体が存在する実体パターン41と、前記導体が存在しない開口パターン42と、を含む所定のパターン形状に形成されている。

(もっと読む)

薄膜トランジスタアレイ基板、及び液晶表示装置

【課題】透明導電膜上層に形成される絶縁膜の膜浮きの発生を防止或いは抑制し、歩留り或いは信頼性を向上することの可能な薄膜トランジスタアレイ基板、及び液晶表示装置を得る。

【解決手段】この発明のTFTアレイ基板100においては、TFT51と、ソース電極53及びドレイン電極54、並びにソース電極53及びドレイン電極54と同一材料により同層に形成される金属パターン5の何れかに直接重なり形成される透明導電膜パターン6と、透明導電膜パターン6上を含むゲート絶縁膜8上を覆う上層絶縁膜9を備え、少なくとも額縁領域42に形成される透明導電膜パターン6は、ソース電極53、ドレイン電極54或いは金属パターン5のパターン端面を覆うことなく形成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 ダイシングラインの寸法を縮小された半導体装置およびその製造方法を提供する。

【解決手段】 半導体装置は、複数のチップ領域2を有する半導体基板1を含む。絶縁膜11、13、15は、半導体基板を覆う。半導体基板上および層間膜中に設けられた電子素子4および配線5、6を含んだ電気回路は、チップ領域内に、チップ領域ごとに相互に電気的に独立して設けられる。導電性の境界パターン12は、複数のチップ領域の相互間の境界領域3中の層間膜中に形成され、チップ領域を囲み、電子素子から電気的に独立しかつ間に間隔を有する。

(もっと読む)

半導体装置の製造方法

【課題】高周波領域において優れた電気的特性が得られるように、寄生容量を低減し得る半導体装置の製造方法を得る。

【解決手段】第1のソース電極、ゲート電極、ドレイン電極、及び第2のソース電極が、所定方向に沿ってこの順に並んで半導体基板の上面上に形成された構造を有するトランジスタを形成する。犠牲層を、トランジスタを覆って半導体基板の上面上に形成する。犠牲層を部分的に除去することにより、第1のソース電極及び前記第2のソース電極を露出する。第1のソース電極及び第2のソース電極に接続され、所定方向に沿って延在する配線を、犠牲層の上面上に形成する。犠牲層を除去する。トランジスタ及び配線を覆う形状に加工されたシート、テープ、又は基板を、トランジスタ及び配線を覆って半導体基板の上面上に貼り付ける。

(もっと読む)

パターン形成方法及びデバイス製造方法

【課題】露光装置の解像限界よりも微細な非周期的な部分を含むパターンを、露光装置を用いて形成する。

【解決手段】パターン形成方法は、ウエハW上に第1L&Sパターン71を形成し、第1L&Sパターン71を覆うように第1保護層48、周期方向が直交する第2L&Sパターン78、及びフォトレジスト層60を形成し、第2L&Sパターン78の一部と重なるように、フォトレジスト層60に第1開口部60A,60Bを有する第3パターンを形成し、第1開口部60A,60Bを介して第1保護層48に第2開口部48A,48Bを形成し、第2開口部48A,48Bを介して第1L&Sパターン71の一部を除去する。

(もっと読む)

半導体素子及びその半導体素子のパターン形成方法

【課題】 フォトリソグラフィ工程の解像限界内で、具現可能なサイズのパターンを利用して超微細な幅及び間隔を持つ高密度パターンを形成できる配置構造を持つ半導体素子及びその半導体素子パターン形成方法を提供する。

【解決手段】 半導体素子は、コネクション領域に隣接するメモリセル領域を含む基板、メモリセル領域からコネクション領域まで第1方向に延びて配され、第1ライン幅及び第1ライン間隔を持つ複数の第1導電ライン、第1導電ラインそれぞれに連結されるように配され、第2ライン幅及び第2ライン間隔を持つ複数の第2導電ライン、コネクション領域に配され、第1導電ラインに電気的に連結された複数のパッド、を備える。半導体素子上のパターン形成方法は、微細ライン幅及び間隔を提供するために2段階のスペーサ形成工程を含むことができる。

(もっと読む)

1 - 20 / 119

[ Back to top ]