Fターム[5F033QQ28]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチングマスク (2,287) | 絶縁膜 (1,171)

Fターム[5F033QQ28]に分類される特許

1,161 - 1,171 / 1,171

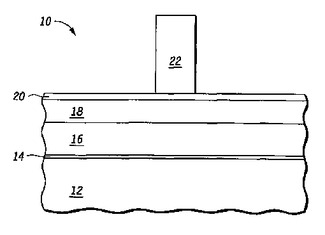

有機反射防止膜(ARC)を有する半導体装置及びその方法

半導体装置(10)の製造において、エッチングされる導電性材料(16)上のパターニング積層部は、下層にあるオルトケイ酸テトラエチル(TEOS)層(20)のパターニングに用いられるパターニングフォトレジスト層(22)を有している。TEOS層(20)は、従来より低い温度で成膜される。低温TEOS層(20)は、有機反射防止膜(ARC)(18)上に設けられ、有機反射防止膜は、導電層(16)上に設けられる。低温TEOS層(20)は、有機ARC(18)とフォトレジスト(22)との間の接着を提供し、低い欠陥性を有し、ハードマスクとして機能し、有機ARC(18)と共に望ましくない反射を低減させる位相シフト層として機能する。  (もっと読む)

(もっと読む)

溝配線を有する半導体装置および半導体装置の製造方法

【課題】 多層配線において、ショートやビア抵抗増加のような目合わせずれによる問題を回避し、信頼性の高い多層配線を得る。

【解決手段】 半導体装置は、第1配線層(201)と、層間絶縁層(202〜208)とを具備する。第1配線層(201)は、基板の上面側に設けられ、第1配線を含む。層間絶縁層(202〜208)は、前記第1配線層(201)上に設けられ、一方の端を前記第1配線に接続されたビアと、前記ビアの他方の端に接続された第2配線とを含む。前記層間絶縁層(202〜208)はシリコン酸化膜より低い比誘電率を有する。前記層間絶縁層(202〜208)の上部は、下側から順に、シリコン酸化膜(206)、シリコン窒化膜(207)、シリコン酸化膜(208)を備える。

(もっと読む)

集積回路デバイス内の相互接続構造体

【課題】 フォトレジスト汚染の問題に悩まされないデュアル・ダマシン構造体を形成する方法を提供すること。

【解決手段】 本発明は、集積回路デバイス内のデュアル・ダマシン相互接続構造体の製造に関する。具体的には、平坦化材料及び拡散障壁材料を用いて、低kの誘電体薄膜内にシングル又はデュアル・ダマシン構造体を形成するための方法が開示される。この方法の好ましいデュアル・ダマシンの実施形態において、最初に誘電体材料にビアを形成し、次にビア内及び誘電体材料上に平坦化材料を付着させ、平坦化材料上に障壁材料を付着させる。次に、リソグラフィにより像形成材料にトレンチが形成され、障壁材料を通して平坦化材料がエッチングされ、トレンチ・パターンが誘電体材料に転写される。これらのエッチング・ステップの過程の間及び該エッチング・ステップの過程に続いて、像形成材料、障壁材料及び平坦化材料が除去される。次に、結果として得られるデュアル・ダマシン構造を金属化することができる。この方法を用いる場合、層間誘電体材料によるフォトレジスト汚染の問題が軽減される。

(もっと読む)

ライン及びビア導体のための異なる材料を有するデュアル・ダマシン相互接続構造体

【課題】 ライン導体のために用いられるものと異なる、ビア又はスタッドのための材料を用いて、デュアル・ダマシン相互接続構造体を形成する方法を提供すること。

【解決手段】 ライン導体に用いられるものとは異なる、ビア又はスタッドのための材料を用いるか、又はトレンチ・ライナに用いられるものとは異なる、ビア・ライナのための材料を用いるか、或いは該トレンチ・ライナのものと異なるビア・ライナ厚を有する、デュアル・ダマシンのバックエンド・オブ・ライン(back−end−of−line:BEOL)相互接続構造体を形成する方法が開示される。改善された機械的強度のために、ビアに厚い超硬合金を用いる一方で、トレンチに薄い超硬合金だけを用い、抵抗を低くすることが好ましい。

(もっと読む)

薄膜電子部品の製造方法および製造装置ならびに薄膜電子部品

本発明は、薄膜電子部品の製造方法およびこの方法を実施する装置に関する。また、本発明は、この方法に従って製造された薄膜電子部品に関する。まず、実質的に誘電性を有する基板上に、導電性材料から成るガルヴァニックに均一な最下段の導電層が形成され、この最下段の導電層から導電領域がガルヴァニックに相互に分離して、電極パターンが形成される。この電極パターン上には、薄膜部品に必要とされる上部の不活性層または活性層を1層または数層形成することが可能である。本発明によれば、この最下段の導電層が分離することによる電極パターンの形成は、ダイカットエンボス加工に基づく切断作業を最下段の導電層に行うことによる。すなわち、切断作業に使用する切断部材の浮彫りが、基板上に永久変形が生じさせ、同時に、導電層から、ガルヴァニックに相互に分離した導電領域に至る領域をエンボス加工する。本発明は、ロールツーロール方式における薄膜部品の製造に適している。

(もっと読む)

(もっと読む)

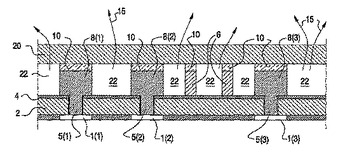

多孔質の誘電体層とエアギャップとを有する基板の製造方法、および基板

金属ライン(8(i))の間および誘電体内にエアギャップを形成する方法である。方法は、デュアルダマシン(dual damascene)構造を得ること、拡散バリア層(10)を、平坦化された面に直接加えること、およびリソグラフィステップを行なうことからなり、これにより、金属ラインを、拡散バリア層の下に遮蔽する。任意として、金属ライン(8(i))間の大きな誘電体領域(6)のいくつかの部分も、遮蔽される。露出した拡散バリア層部分および下にある誘電体がエッチングされる。典型的には150〜450℃の温度に加熱することにより、揮発性成分に分解することができる材料の層が加えられ、エッチングまたはCMPにより平坦化される。分解性生成物に対して透過性である誘電体層(20)が堆積され、その後、基板は加熱される。次いで、使い捨て層が分解し、透過性の誘電体層を通じて消滅し、その後に、金属ライン(8(i))および大きな誘電体領域の間に、エアギャップ(22)を残す。  (もっと読む)

(もっと読む)

絶縁膜形成用塗布液とそれを用いた半導体装置

【課題】配線の信号伝播性能向上を絶縁被膜の誘電率分布の均一化によって実現することを課題とする。

【解決手段】アルコキシシランを加水分解して得られたシリカからなる、平均粒径が1000Å以下であって、粒径の3σが平均粒径の20%以下である第一の微粒子と、平均粒径が1第一の微粒子の1/3以下で、粒径の3σが第二の微粒子の平均粒径の20%以下である第二の微粒子とを含有し、半導体デバイスに用いるに好ましい被膜形成用塗布液。

(もっと読む)

デュアルダマシンによる半導体装置の製造方法

【課題】 放熱性が良好で、製造コストが低く、微細加工に好適なデュアルダマシンによる半導体装置の製造方法を提供する。

【解決手段】 基板1上に無機層間膜5、有機層間膜6、シリコン酸化膜からなる下部マスク7、シリコン窒化膜からなる上部マスク8を形成し、上部マスク8上にシリコン酸化窒化膜からなり膜厚が20乃至100nmであるカバーマスク10を形成する。そして、反射防止膜11及びレジスト膜12を形成する。次に、レジスト膜12をマスクとして、反射防止膜11、カバーマスク10、下部マスク7をエッチングする。そして、カバーマスク10をマスクとして、有機層間膜6及び無機層間膜5をエッチングしてビアホールを形成する。次に、上部マスク8をマスクとして有機層間膜6をエッチングして配線溝を形成する。

(もっと読む)

半導体装置とその製造方法

【課題】 微細トランジスタと高耐圧トランジスタの線幅バラツキを低減する。

【解決手段】 P型の半導体基板1上の段差部を境にしてP型ウエル2及びN型ウエル3が形成されたものにおいて、段差低部に形成される前記P型ウエル2上に第1線幅を有する第1のトランジスタ(微細トランジスタ)が形成され、段差高部に形成される前記N型ウエル3上に第1のトランジスタよりも線幅の太い第2線幅を有する第2のトランジスタ(高耐圧トランジスタ)が形成されていることを特徴とする。

(もっと読む)

高周波用伝送線路およびその製造方法

【課題】 比抵抗の低い半導体基板の上であっても、その上に形成した高周波用伝送線路の伝送損失を抑制できるようにする。

【解決手段】 信号線103およびグランド線104と半導体基板101との間に介在する絶縁膜102と、信号線103の両側の半導体基板101に形成された溝105とを備え、信号線103およびグランド線105は、半導体基板101に接している辺より半導体基板101に垂直な隣辺の方が長い長方形状の断面を有する。

(もっと読む)

多層スピンオン多孔性誘電体からなるlow−k配線構造

【課題】その中にマイクロトレンチを含まない低誘電体層間絶縁膜金属導体配線構造およびそのような構造の形成方法を提供する。

【解決手段】導体抵抗に対する制御は、第1の原子組成を有する多孔性の低誘電体層間絶縁膜の線とバイア誘電体層との間に位置する第2の原子組成を有する埋込みエッチング停止層により行われる。本発明の配線構造は、また、二重波形模様タイプの配線構造を形成する際に助けになるハードマスクを含む。第1および第2の組成は、エッチング選択性が少なくとも10:1またはそれ以上になるように選択され、特定の原子組成および他の発見できる量を有する多孔性の低誘電体層間絶縁膜有機材料または無機材料の特定のグルーブから選択される。

(もっと読む)

1,161 - 1,171 / 1,171

[ Back to top ]