Fターム[5F033UU07]の内容

半導体集積回路装置の内部配線 (234,551) | レイアウト、シミュレーション (1,514) | シミュレーション (64)

Fターム[5F033UU07]に分類される特許

61 - 64 / 64

半導体装置

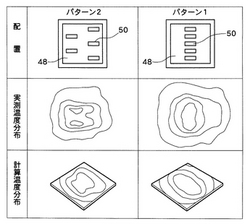

【課題】大電力用の半導体素子において、温度上昇分布をより均一にすることである。

【解決手段】電流が大きいために、上部電極層48の抵抗の場所的分布の影響を受け、上部電極層48内における複数の接続部50の平面配置条件に依存して半導体素子の温度上昇分布が定まる大電流用の半導体素子において、パターン2のようにジグザク状に接続部50を配置するのと、パターン1のように1列に接続部50を配置するとのでは、温度上昇分布が明らかに異なる。このことはシミュレーションの結果と定性的によい一致を示す。この他に、各ワイヤのそれぞれが、上部電極層48との間で複数の接続部を形成するようにしてもよい。

(もっと読む)

回路検証方法、回路検証システム、集積回路及び集積回路の製造方法

【課題】 実用的な速度のシミュレーションによりエレクトロマイグレーションの検証をすることができる回路検証方法、回路検証システム、集積回路及び集積回路の製造方法を提供すること。

【解決手段】 検証目的の回路の構成及び前記検証目的の回路に備わる各配線の幅を示す回路データを入力する回路データ入力工程と、前記回路データに基づいて直流動作点解析を行うことにより、前記各配線節点における直流電流値を算出する直流電流値算出工程と、前記直流電流値算出工程で算出される前記各配線節点における直流電流値と、前記回路データが示す前記各配線節点の幅と、に基づいて前記各配線節点における電流密度値を算出する電流密度値算出工程と、前記電流密度算出工程で算出される前記各配線節点における電流密度値と所定許容値とをそれぞれ比較する比較工程と、前記比較工程における比較結果を出力する比較結果出力工程と、を含む。

(もっと読む)

導体におけるジュール加熱と電流密度間の関係を確立するための方法及びシステム

例示的な一実施形態に従って、導体におけるジュール加熱とこの導体における電流密度間の関係を確立するための方法がウェーハレベル測定(500)を実行することによって実装される。この実施形態に従って、導体(118,)における抵抗の温度係数を得るためにウェーハレベル測定が実行される(ステップ502)。本方法は、又、導体の熱抵抗を判断することを含む(ステップ510)。この熱抵抗は、その後導体におけるジュール加熱と導体における電流密度間の関係を確立するために利用される(ステップ512)。そのようにして得られた関係は、その後、信頼性のある半導体デバイス設計において補助するために設計ルール、平均故障時間、及び他の情報を判断するために利用される(ステップ514)。もう1つの実施形態に従って、ウェーハレベル測定システム(100)が導体におけるジュール加熱と導体における電流密度間の関係を確立するために利用される。  (もっと読む)

(もっと読む)

接触抵抗が低減された半導体デバイス

【課題】パワー半導体デバイスの電気抵抗を小さくする。

【解決手段】 第1の導電性の材料から構成され、表面に電極を有する半導体ダイと、前記第1の導電性の材料の抵抗率よりも低い抵抗率を有する第2の材料から構成され、前記電極の上に設けられた導電性本体とを備える半導体デバイスと、第1の導電性の材料から構成された、半導体デバイスの電極の表面にバリア層を形成するステップと、前記第1の材料の電気抵抗率よりも電気抵抗率が低い第2の導電性の材料から構成されたシード層を、前記バリア層の上に形成するステップと、前記第2の材料から構成された前記シード層の上に導電製本体を形成するステップとを有する、半導体デバイスを製造するための方法に関する。

(もっと読む)

61 - 64 / 64

[ Back to top ]